|

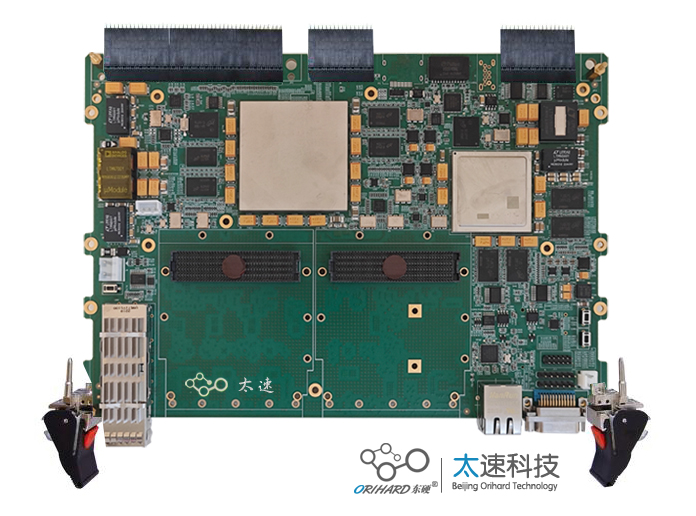

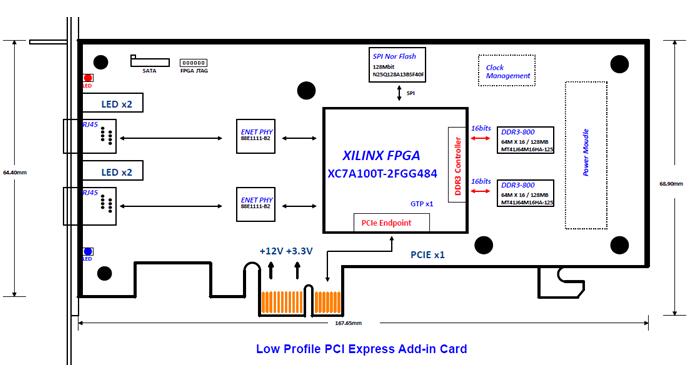

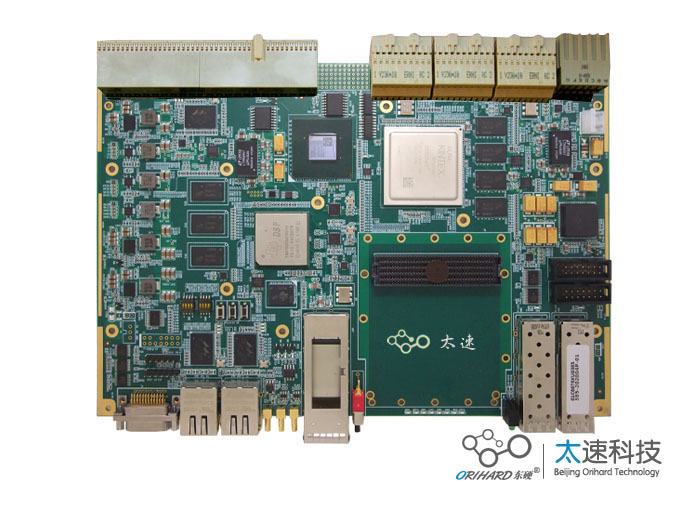

一、板卡概述 本板卡系北京太速科技自主研发的基于6UCPCI处理板,适用于多核处理器多输入芯片验证的应用。芯片采用工业级设计。 基于XCVU440T的多核处理器多输入芯片验证板卡基于6UCPCI架构,是单机中的一个计算控制板卡,以XilinxXCVU440-FLGA2892FPGA(作为处理器载体)为核心,FPGAXC7A200T作为信号的的电平转换功能,辅助外围接口驱动芯片,完成双FMC,光纤,网络,3.3VIO的扩展,为用户完成控制及计算,芯片验证提供充分的可能性。验证板原理框图如下: |

|

图2:板卡结构框图 二、板卡简介 2.1 存储 存储区可配置FLASH、SRAM、DDR3-SRAM,按照目前元器件可获得性及需求,为单板配置: 1)FLASH:(64M×16bit/片)×3片,(可选S29GL01GP,32bit数据+8bit校验,共40位并行); 2)SRAM:(1M×16bit/片×3片)/组×2组,(可选IS61WV102416,32bit数据+8bit校验,共40位并行); 3)DDR3:两组DDR3颗粒,每组容量256M×16共3片,40bit。 2.2 前面板接口 支持2个FMC-HPC接口,每个FMC支持GTHx8,LA、HA、HB接口。 支持1个QSFP+接口。 支持1个1000BASE-T千兆以太网。 支持JTAG调试。 支持多路RS422信号。 2.3 CPCI接口 J1提供板卡供电接口,单电源+12V XJ2支持GTHx16。 J3支持LVDSx16对。 J4、J5支持LVDSx32对 三、物理特性 尺寸:大小为233mmx160mm 工作温度:商业级0℃~+55℃,工业级-40℃~+85℃ 工作湿度:10%~80% 四、供电要求 单电源供电,整板功耗:30W 电压:DC+12V,5A 纹波:≤10% 五、应用领域 芯片验证 |

审核编辑 黄宇

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

芯片

+关注

关注

460文章

52736浏览量

444090 -

板卡

+关注

关注

3文章

146浏览量

17249 -

CPCI

+关注

关注

7文章

72浏览量

33455

发布评论请先 登录

相关推荐

热点推荐

国产化板卡设计原理图:2274-基于FMC接口的JFM7VX690T36的3U VPX信号处理板

),支持导冷,能够满足用户在特殊环境下的使用需求。 二、功能和技术指标:? 板卡功能 参数内容 主处理器 JFM7VX690T36 板卡标准 VPX?VITA?

VPX处理板设计原理图:9-基于DSP TMS320C6678+FPGA XC7V690T的6U VPX信号处理卡 C6678板卡, XC7VX690T板卡, VPX处理板

AI边缘计算,, C6678板卡, PCIe信号, VPX处理板, XC7VX690T板卡

中科亿海微SoM模组——基于EQ6HL9S的单轴光纤陀螺板卡

单轴光纤陀螺板卡是一种基于光纤陀螺技术(FOG,FiberOpticGyroscope)的惯性测量组件,主要用于测量载体绕单一轴向的角速率。单轴光纤陀螺板卡主芯片使用EQ6HL9S-F2CSG100

中科亿海微SoM模组——基于FPGA+RSIC-V的计算机板卡

基于FPGA+RSIC-V的计算机板卡主芯片使用中科亿海微EQ6HL45-CSG324FPGA芯片和高性能微控制器HPM6880,并集合ADCLHA6958H、6通道数字隔离

超大规模芯片验证:基于AMD VP1902的S8-100原型验证系统实测性能翻倍

引言随着AI、HPC及超大规模芯片设计需求呈指数级增长原型验证平台已成为芯片设计流程中验证复杂架构、缩短迭代周期的核心工具。然而,传统原型验证

汉思新材料HS711板卡级芯片底部填充封装胶

汉思新材料HS711是一种专为板卡级芯片底部填充封装设计的胶水。HS711填充胶主要用于电子封装领域,特别是在半导体封装中,以提供机械支撑、应力缓冲和保护芯片与基板之间的连接免受环境因素的影响。汉思

SEGGER SystemView支持多核行为的观察和验证

2025年2月,SEGGER宣布其实时软件验证和可视化工具SystemView增加了多核支持,将其功能扩展到单个芯片上具有多个CPU内核的系统。

XCVU13P板卡设计原理图:509-基于XCVU13P的4路QSFP28光纤PCIeX16收发卡

PCIeX16收发卡 , XCVU9P卡 , XCVU13P , XCVU13P板卡 , QSFP28光纤

调试一块使用lmk04228作为光纤通讯的参考时钟的板卡,遇到的疑问求解答

绝缘后的金属片压在芯片上,光纤收发器能正常工作,观察示波器输出时钟没有任何变化和抖动,所以不知道是不是有什么干扰

下面是我们的配置和原理图,请帮忙看下是不是设计有问题

原理图

发表于 11-11 07:25

基于6U VPX XCVU9P+XCZU7EV的双FMC信号处理板卡

板卡基于6U VPX标准结构,包含一个XCVU9P 高性能FPGA,一片XCZU7EV FPGA,用于 IO扩展接口,双路HPC FMC扩展高速AD、DA、光纤接口等。是理想应用于高性能数字计算,光纤加速的板卡。

XCVU9P 板卡设计原理图:616-基于6U VPX XCVU9P+XCZU7EV的双FMC信号处理板卡 高性能数字计算卡

光纤加速计算 , 基带信号处理 , 高性能数字计算卡 , 高速图像处理卡 , XCVU9P卡

《DNK210使用指南 -CanMV版 V1.0》第十章 板卡信息实验

芯片等外设通讯,通常情况下,这需要查看板卡的原理图来确定使用的IO引脚,但查看原理图的效率较低,且会在脚本文件中固定下程序中使用的IO引脚,不利于脚本程序的移植。综合以上IO引脚使用的

发表于 09-28 15:04

芯片验证板卡设计原理图:基于XCVU440的多核处理器多输入芯片验证板卡

芯片验证板卡设计原理图:基于XCVU440的多核处理器多输入芯片验证板卡

评论