Vivado调用Questa Sim或ModelSim仿真中存在的一些自动化问题的解决方案。

Vivado调用Questa Sim仿真中存在的一些问题

首先说明一下Modelsim与Questa Sim都可以与Vivado联调,也比较相似,但是Questa Sim比Modelsim功能更加广泛,对于System Verilog的语法支持更加完善,本文以Questa Sim为例说明一下Vivado调用第三方仿真软件查看波形的过程中存在的一些问题。

1、添加新的观测信号需要重新仿真

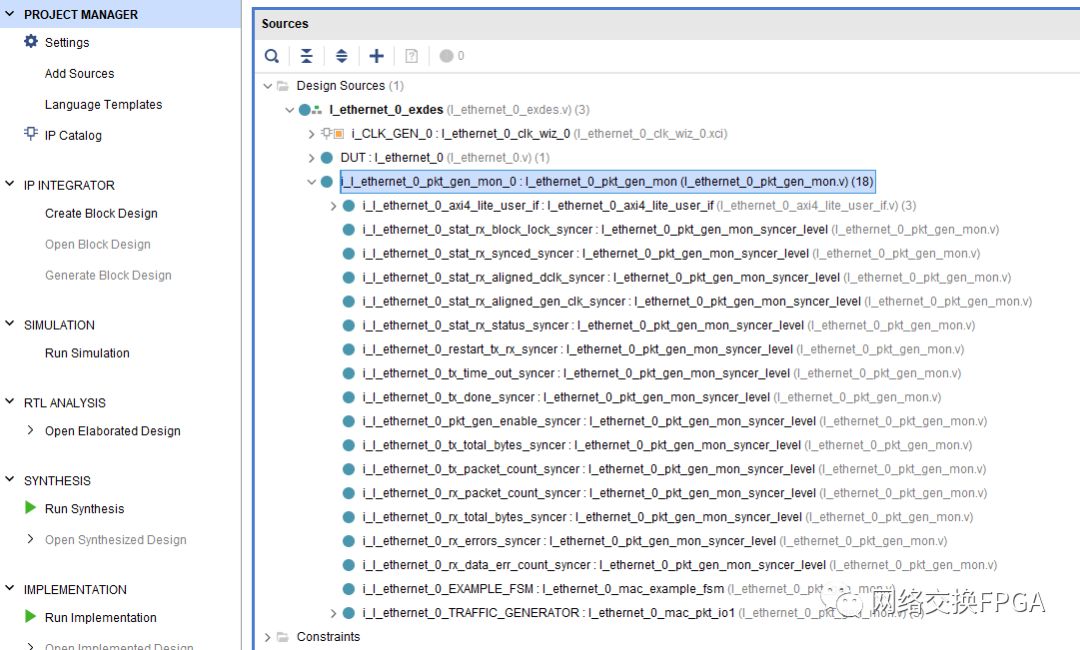

Vivado直接调用Modelsim/QuestaSim进行仿真时,波形文件里默认只会出现仿真最顶层中包含的信号,若此时将仿真运行一段时间后,想要查看其他模块信号波形时,需要重新仿真或者运行do XXX_simulate.do方可。 以图1所示工程为例,

图1 vivado示例工程

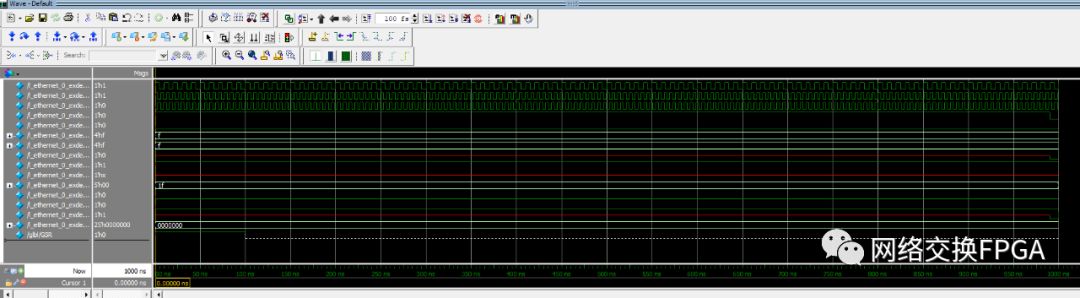

在这个工程中,我们调用Questa Sim进行仿真,可以看到顶层模块会自动跑100ns,如图2所示

图2 QuestaSim仿真波形

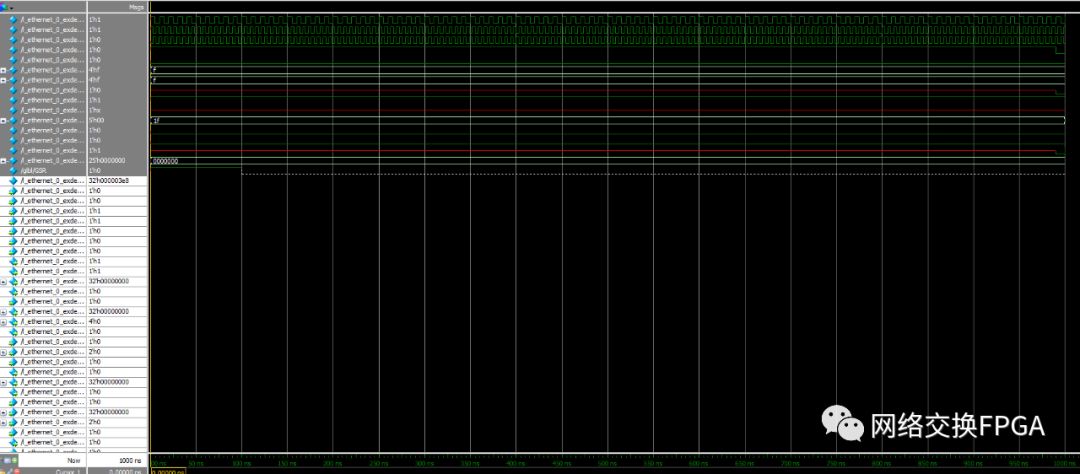

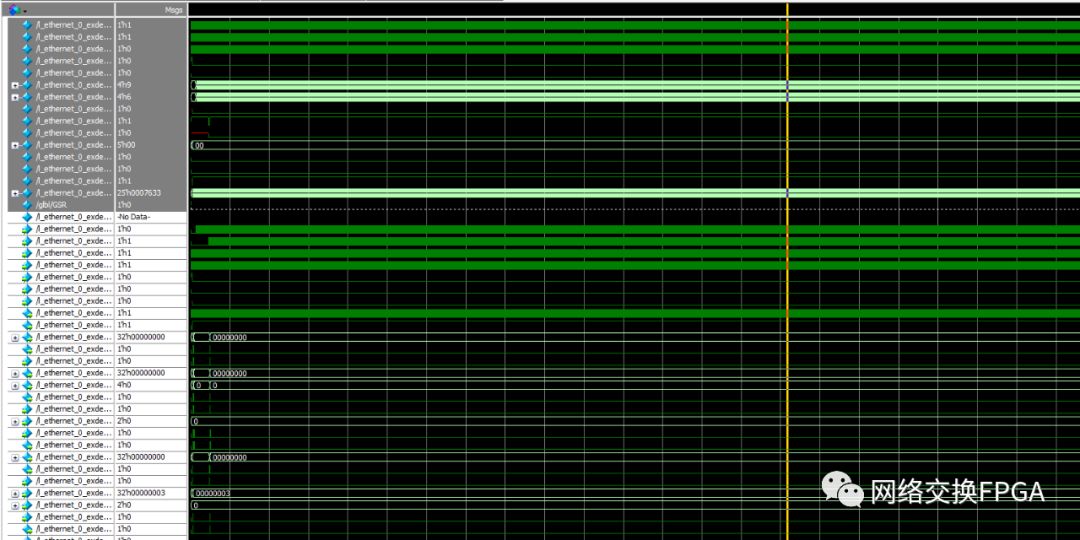

此时,我们若想查看l_ethernet_0_pkt_gen_mon这个模块的波形时,直接进入波形界面进行添加,结果如图3所示。

图3 QuestaSim仿真波形

从图3中可以看到,当模块的信号被添加进来后,已经运行过的仿真时间内,新加入的信号没有仿真结果。

2、修改逻辑代码后,需要重新调用仿真器

在代码调试过程中,修改部分逻辑代码后(不包括IP核),如果想要查看修改后工程的仿真结果,需要关闭当前的仿真器,从vivado中重新调用方可。其原因是vivado在生成XXX_compile.do文件时,会在其末尾自动添加“quit -force”语句,而更改了相应的代码文件后,我们需要执行“do XXX_compile.do”命令重新编码整个库,然而在运行此文件时,当前的仿真器会被强制退出。

解决方案

为了解决上述问题,同时更加方便使用,本文使用TCL语言,编写了一个较为方便的do文件,其可以实现如下功能:

1、对XXX_compile.do自动修改

对XXX_compile.do自动修改,去除其末尾的“quit -force”,并生成新的compile.do文件,其对应的源代码如下:

setfilename[glob*_compile.do] setcontent[open$filenamer+] setrow0 while{![eof$content]}{ incrrow gets$contentline setlist($row)$line } close$content setfilename2"compile.do"; setcontent[open$filename2w+] for{seti1}{$i<=?$row}?{incr?i}?{ ????if?{![string?match?"quit?-force"?$list($i)]}?{ ????????puts?$content?$list($i) ????}???? }; close?$content

2、使用“log -r /*”命令

该命令可以让modelsim/Questa Sim在进行仿真中,对所有信号同步进行仿真,从而解决新加入的观测信号没有仿真结果的问题;

3、保证仿真器不退出

当修改工程中的逻辑代码(不含IP核)后,只需要运行该do文件,其自动进行编译和仿真,且使用修改后的compile.do文件,保证仿真器不退出,其对应的源代码如下:

setfilenamecompile.do do$filename setfilename[glob*_simulate.do] do$filename log-r/* restart-force run1ms

例程

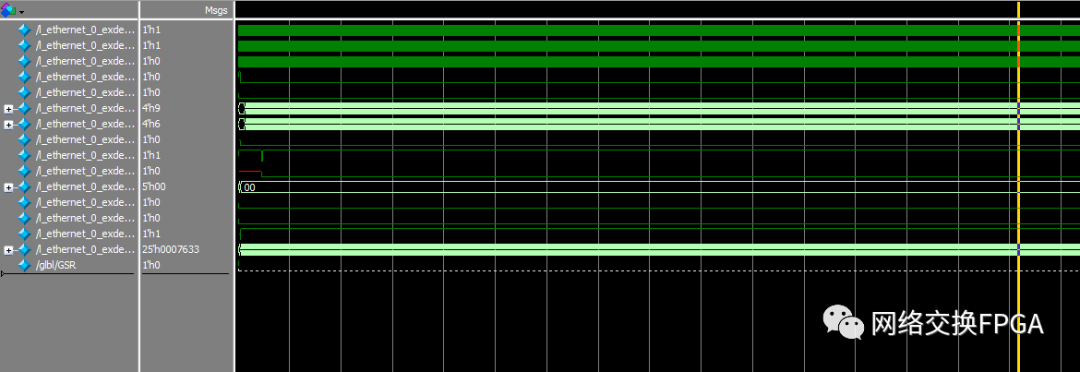

在使用该do文件之前,需要首先通过vivado调用modelsim/ questasim,然后将do文件拷贝到工程对应的behave文件夹下。 仍以图1所示工程为例,当修改了代码内部分逻辑后,在QuestaSim的transcrip界面,输入命令do auto_update_sim.do即可自动重新编译、仿真,结果如图4所示(默认仿真时间设置为1ms)

图4 QuestaSim仿真波形

添加了l_ethernet_0_pkt_gen_mon这个模块,可以发现仿真过的时间内同样有仿真结果,如图5所示。

图5 QuestaSim仿真波形

完整源码

setfilename[glob*_compile.do]

setcontent[open$filenamer+]

setrow0

while{![eof$content]}{

incrrow

gets$contentline

setlist($row)$line

}

close$content

setfilename2"compile.do";

setcontent[open$filename2w+]

for{seti1}{$i<=?$row}?{incr?i}?{

????if?{![string?match?"quit?-force"?$list($i)]}?{

????????puts?$content?$list($i)

????}????

};

close?$content

set?filename?compile.do

do?$filename

set?filename?[glob?*_simulate.do]

do?$filename

log?-r?/*

restart?–force

run?1ms

审核编辑:刘清

-

仿真器

+关注

关注

14文章

1043浏览量

85637 -

TCL

+关注

关注

11文章

1787浏览量

90208 -

Vivado

+关注

关注

19文章

835浏览量

69146 -

MODELSIM仿真

+关注

关注

0文章

15浏览量

7553

原文标题:[源码]Vivado调用Questa Sim仿真小技巧

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

在仿真执行自定义custom指令时,只能执行软件程序中所调用第一条是为什么?

基于saber仿真中一些问题的处理方法

VCS独立仿真Vivado IP核的一些方法总结

使用Vivado仿真器进行混合语言仿真的一些要点

使用VCS仿真Vivado IP核时遇到的问题及解决方案

关于Vivado Non-project,我们应知道的一些问题

Questa Sim不支持-novopt问题

Vivado调用Questa Sim仿真中存在的一些问题

Vivado调用Questa Sim仿真中存在的一些问题

评论