不足5瓦的超低功耗,高达250万的超高性能

RISC-V已成为芯片架构第三级,但迟迟未见高性能芯片方案成熟落地,库瀚团队基于20余年企业级存储及芯片设计经验打破这一局面,现已率先实现全球首颗落地解决方案的RISC-V架构PCIe5.0企业级SSD主控Aurora,并仅用3个月时间完成性能验证,与产业伙伴一同开启国内高端旗舰SSD主控芯片自主低碳新时代。

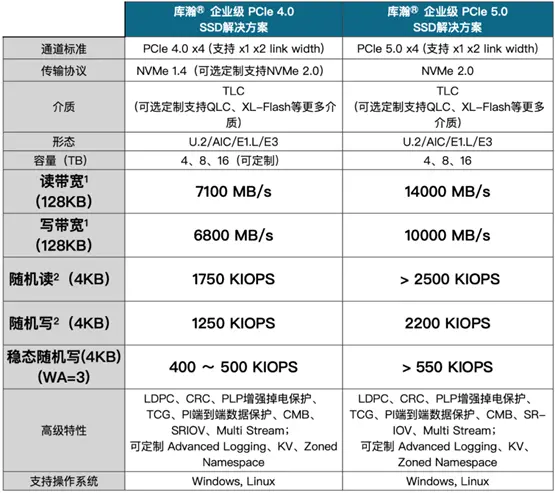

性能达业内顶尖水平

库瀚Aurora实测PCIe5模式下性能达到顺序读14GB/s,顺序写10GB/s,随机读>2.5M IOPS,随机写2.2M IOPS,稳态随机写>550K IOPS。PCIe4模式下性能为顺序读7100MB/s、顺序写6800MB/s,随机读1750K IOPS、稳态随机写400~500K IOPS。两种模式下均实现业内顶尖的性能水准。

*注:

1.顺序读写测试条件:FIO, QueueDepth=128, BlockSize= 128KB

2.随机读写测试条件:FIO, QueueDepth=256, BlockSize= 4KB

芯片能效达50K IOPS/W

关于Aurora设计过程中克服的挑战,库瀚芯片设计总监刘延峰表示,“升级PCIe协议实现性能的提升是SSD性能上升的标准路径,但随着主控性能提升,采用传统架构的SSD会出现比较严重的发热情况,尤其是PCIe5.0接口,发热问题更为突出。直接影响了芯片实际使用性能。库瀚团队一个核心的突破,就是保证了Aurora充分实现PCIe5.0带来的性能跃迁的基础上,实现了非常低的功耗。”每个公司都能用RISC-V,但并非每个公司都能用好RISC-V。库瀚科技基于核心团队20余年的存储芯片设计经验积累以及对新一代存储整体技术栈的理解,充分把握RISC-V开源、极简、模块化的特点,创新设计库瀚Aurora芯片,最终实现以低于5W的工作功耗,实现250万IOPS的随机读性能,围绕数据存储绿色发展问题,有望为我国在数字经济时代实现双碳目标形成巨大的助力。

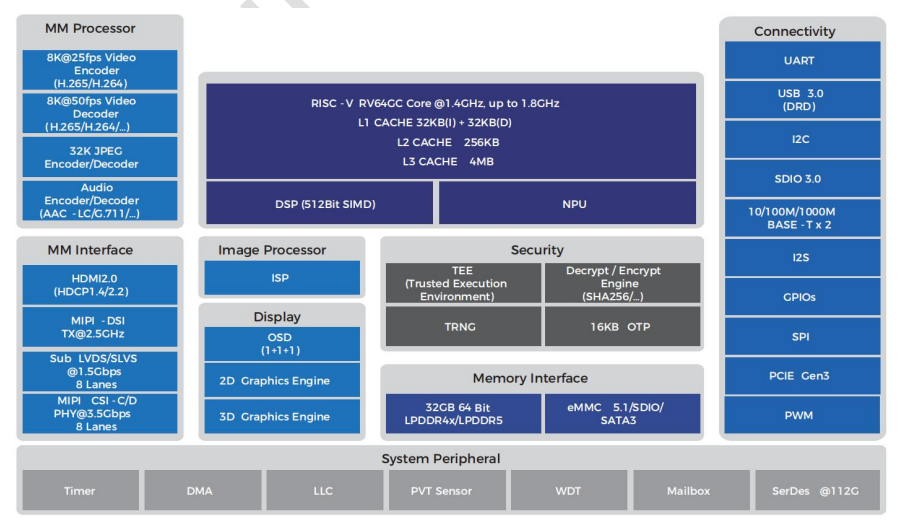

创新架构实现定制化指令集,支持高度灵活软硬融合存储方案

库瀚 Aurora 采用混合RISC-V处理器控制平面,支持定制非标准NVMe命令集,实现固件高度灵活,帮助客户实现独特的客制化功能。同时,库瀚Aurora自研智能软/固件监测方案 ,可按需监测SSD运行情况,提高SSD性能及寿命,优化企业级服务的质量。例如库瀚Aurora具备可供固件使用的可编程硬件警告能力,灵活监控影响QoS的后台活动;可编程暂停/恢复NAND闪存操作能力,以提高读取QoS;以及灵活的ZNS或软件定义的数据放置提示/指南,以减少后端的数据搬迁活动。

库瀚Aurora从研发初期就紧贴客户和产业的实际需求,已与多家客户及产业伙伴深度合作多时,其中,库瀚已于8月联合中国电子云发布全球首个PCIe5.0云定义固态存储解决方案CEAFLASH,定制诸如了增强版ZNS等前沿技术方案,通过更高的可用容量、更高的IOPS、更低的延迟、更灵活的客制化功能,助力云和超大规模数据中心客户降本增效。

库瀚始终追求以卓越的技术实现更高的客户价值,以库瀚Aurora 成功完成性能验证为契机,诚邀更多企业级产业链伙伴共建高性能、低功耗的RISC-V PCIe 5.0 数据中心生态,共同应对海量实时数据时代对高性能、低碳数字经济“新基建”的技术挑战。

关于库瀚

由存储工业界海归专家团队联合创办,聚焦企业级存储最具挑战的基础设施层软硬件关键技术研发与产业化,致力于通过可自主演化的可控RISC-V架构关键技术产品——存储服务器处理芯片SPU、SSD主控芯片Aurora与存储基础软件StorEngine,以软硬件融合技术,实现业界最优的总拥有成本(TCO)、功耗(Power Efficiency)、性能(IOPS)、延时(Latency)、服务质量(QoS),重构数据中心存储基础设施,为广泛的人工智能应用、在线交易等低延时、海量数据存储场景赋能,并建立新一代数据中心存储行业标准。

审核编辑:汤梓红

-

SSD

+关注

关注

21文章

3003浏览量

119961 -

PCIe

+关注

关注

16文章

1365浏览量

85773 -

RISC-V

+关注

关注

46文章

2629浏览量

49187 -

库瀚科技

+关注

关注

0文章

6浏览量

115

发布评论请先 登录

全球首款二维RISC-V MPU!命名“无极”,来自复旦团队

最新PCIe5.0 U.2硬盘抽取盒— ICY DOCK MB491V5K-B 开箱测评

知合计算:RISC-V架构创新,阿基米德系列剑指高性能计算

兆松科技发布高性能RISC-V编译器ZCC 4.0.0版本

Banana Pi BPI-RV2 RISC-V 路由器开发板发售, 全球首款RISC-V路由器

广汽科技日 | 全球首款ASIL-D 6核RISC-V芯片重磅发布

AI SoC# 奕斯伟EIC7700 全球首款基于RISC-V架构的边缘计算SoC芯片

OrangePi RV来了!香橙派首款高性能开源RISC-V开发板,解锁神秘技能!

首款RISC-V架构服务器,助力行业精准适配AI场景

Arm与RISC-V架构的优劣势比较

基于risc-v架构的芯片与linux系统兼容性讨论

risc-v与esp32架构对比分析

加入全球 RISC-V Advocate 行列,共筑 RISC-V 的未来 !

库瀚科技全球首款RISC-V架构PCIe5.0 SSD主控性能发布

库瀚科技全球首款RISC-V架构PCIe5.0 SSD主控性能发布

评论