来源:半导体芯科技编译

SEMI最近与PowerAmerica联盟的执行董事兼首席技术官Victor Veliadis合作,举办了一次题为SiC-碳化硅材料特性、制造基础知识和关键应用的在线研讨会。在接受《半导体工程》采访时,Veliadis详细介绍了SiC制造工艺和Si工艺的差异的一些要点。

Etch蚀刻工艺。SiC在化学溶剂中呈现惰性,只有干法蚀刻可行。掩膜材料、掩膜蚀刻的选择、混合气体、侧壁斜率的控制、蚀刻速率、侧壁粗糙度等都需要重新开发。

Substrate thinning衬底减薄。对于SiC低电阻或厚外延处理(材料硬度要求特殊配方)。CMP用于精细平整度控制。

Doping掺杂工艺。由于碳化硅熔点高,掺杂剂扩散常数低,传统的热扩散在碳化硅中并不实用。评估注入种类、剂量、能量、温度、掩蔽材料等。SiC注入后再结晶和注入物激活退火方法(炉内、RTA等)、温度、升温速率、持续时间、气体流量等。选择退火保护层,最大限度地减少SiC晶片表面退化。CMP可用于压平硅片,减轻高温退火的影响。

Metallization关于金属化。针对SiC需要评估CTE匹配的金属,选择抗蚀剂类型,开发底部剥离轮廓,金属蒸发和剥离,溅射金属沉积和干法蚀刻。

Ohmic contact formation欧姆触的形成。SiC/金属阻隔层的高值导致了整流接触。对于欧姆接触,需要进行金属沉积后退火。优化退火温度、升温速率、持续时间、气体流量,保持表面质量。

Gate oxides栅极氧化物。较差的SiC/SiO2界面质量会降低MOS反转层的迁移率。开发钝化技术,以提高SiC/SiO2界面质量。

Transparent wafers透明晶圆。这使得CD-SEM和计量测量变得复杂,因为焦平面是通过使用光学显微镜来确定的。其他工具需要软件/增益/硬件调整,以转移到SiC不透明的波长。需要SiC计量/校验工具。

Relative lack of flatness in SiC wafers SiC晶圆相对缺乏的平整度。这可能会使光刻和其他加工复杂化,特别是高压器件(厚漂移外延层)。高温工艺会进一步降低晶圆的平整度。CMP可以在制造的不同的制造阶段使晶圆变平。

Insulation dielectrics 绝缘电介质。厚的电介质被沉积在SiC中。评估沉积的介质缺陷对边缘终端和器件可靠性的影响。

Veliadis认为,传统IDM通过调整现有工艺,针对SiC的材料特性进行特定的工艺开发和优化,并达到合格标准后,另需购买一些关键的新设备,现有成熟的Si产线可转化为SiC产线。比如,一条150mm的硅制造生产线转化为SiC生产线,费用大约为2000万美元。

审核编辑 黄昊宇

-

工艺

+关注

关注

4文章

694浏览量

29615 -

SiC

+关注

关注

32文章

3271浏览量

65996

发布评论请先 登录

SiC+Si混碳融合逆变器 · 从概念到系统方案落地的全景解析

技术革新,EtherCAT转CAN网关,新能源汽车电池产线再升级

关于CCG5 platform Flash问题,在烧写images时,如何保留产线校准数据?

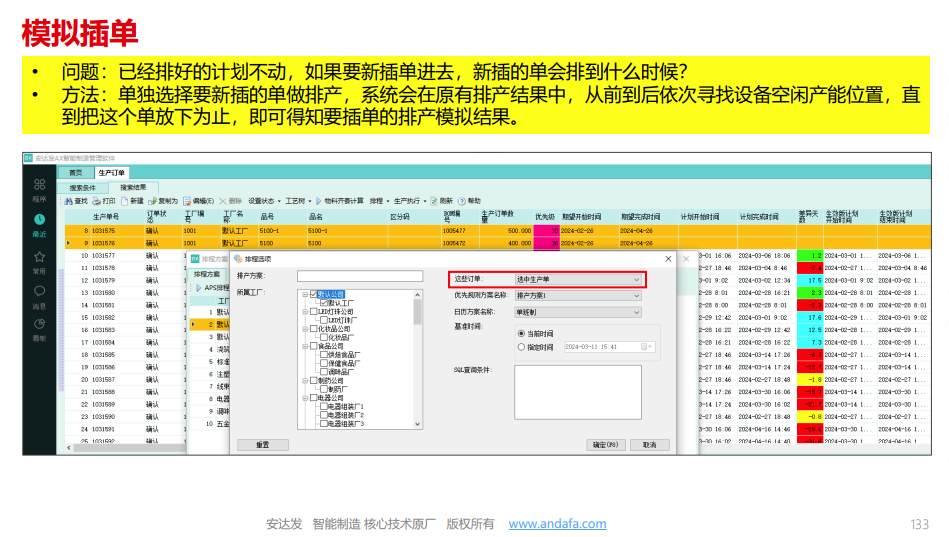

在车间产线层面,APS高级排产软件比MES更专业!

SiC MOSFET 开关模块RC缓冲吸收电路的参数优化设计

GaN、超级SI、SiC这三种MOS器件的用途区别

SiC MOSFET的短路特性和短路保护方法

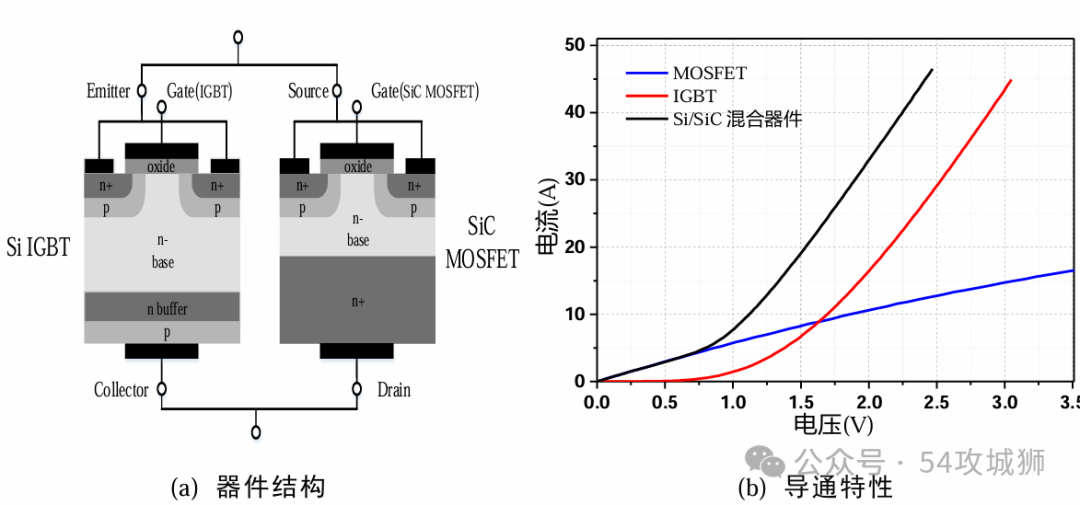

基于Si IGBT/SiC MOSFET的混合开关器件综述

Si IGBT和SiC MOSFET混合器件特性解析

RFID技术在工业制造产线智能管理中的应用

SiC和Si产线差异和转换

SiC和Si产线差异和转换

评论