所有IP核没有正确工作,原因一半是时钟,一半是复位。

前言

复位与初始化部分其实还挺复杂,还好GTX已经帮我们做好了,不想麻烦的直接跳到文末看结论~~~不过了解下也挺有意思的~~

同时GTX复位也挺随意的,你想怎么复位都可以,支持整体复位,单个组件复位。我们也可以不复位,核不会因为我们没有进行软复位就不对核进行复位,在上电之后会自动进行一系列的复位,不随你的意志而转移。下面我们就来仔细研究研究GTX的复位吧!

一、复位与初始化

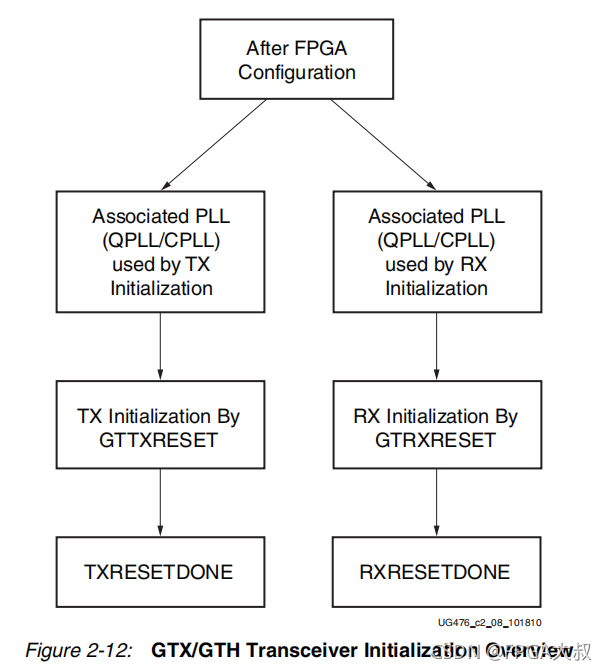

在FPGA上电配置之后,必须进行初始化才能使用GTX/GTH。(后文全用GTX表示,同样适用于GTH)GTX的发送器(TX)和接收器(RX)可以独立的同步进行初始化。

GTX的TX和RX初始化包含两步:

1. 初始化相关的PLL来驱动TX/RX

2. 初始化TX和RX的数据路径(PMA+PCS)

GTX的TX和RX能从QPLL或者CPLL接收一个时钟。所以在TX/RX初始化之前必须对相关的PLL(QPLL/CPLL)进行初始化。TX/RX使用的任何PLL都是单独的进行复位,PLL复位操作与TX/RX复位完全独立。TX/RX的数据路径复位必须在相关的PLL复位完成,locked之后进行。(就跟我们使用PLL IP核一样,等locked拉高之后,时钟稳定才能使用)

看图说话:TX/RX是独立的并行的进行复位操作。

GTX的TX和RX使用一个状态机来控制初始化过程,并被划分为几块来分别复位。该划分允许复位状态机按顺序控制复位过程:PMA可以首先被复位,PCS可以在TXUSERRDY或者 RXUSERRDY信号被断言后进行复位。在需要的时候,它也同样允许PMS,PCS,他们内部的功能模块独立的进行复位。

GTX提供了两种复位类型: initialization 和 component。

? Initialization Reset: 初始化复位。这种复位用作GTX完全复位。必须在设备上电及配置完成之后。在必要的时候,TX端口和RX端口的复位(GTTXRESET 和 GTRXRESET)同样可被用来重新初始化GTX的TX和RX。

? Component Reset: 模块复位。对TX / RX 单独部分进行复位。 TX模块复位端口包括TXPMARESET 和TXPCSRESET 。RX 模块复位端口包含RXPMARESET,RXDFELPMRESET,EYESCANRESET, RXPCSRESET, RXBUFRESET和 RXOOBRESET。(有木有很多很复杂。。)

注:

1. 所有的复位高电平有效。

2. 这些复位都是异步的。对这些异步复位的推荐设计是一个(各自时钟域)时钟周期的脉冲信号。

3. 复位端口不应该被用做下电的目的。

两种复位类型主要有以下不同:

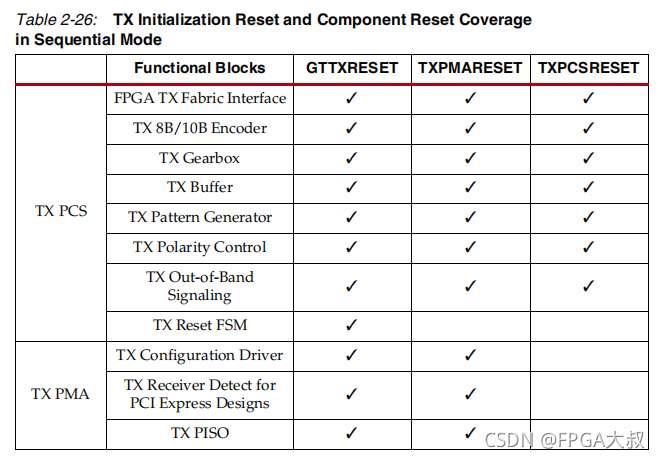

TX部分:

RX部分:

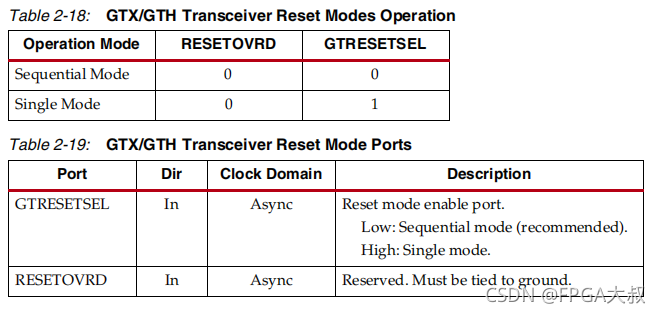

二、复位模式

GTX的初始化复位 (initialization reset) 只能使用顺序复位模式(Sequential mode )。

GTX的TX复位只能使用顺序复位模式(Sequential mode )。

GTX的RX复位可以使用两种复位模式:

Sequential mode :顺序复位。随复位状态机(initialization 或 component)顺序复位各个部分。

Single mode :单独复位。仅复位单个部分(PMA、PCS、内部功能块)。

复位完成由信号(TX/RX)RESETDONE表示,由低到高。

复位模式对CPLL和QPLL没有任何影响。GTX也可以被软件进行弹性复位设置,不管是哪种模式。

使用GTRESETSEL来选择复位模式,RESETOVRD必须驱动为低电平。详细见下表:

注:复位前,GTRESETSEL和RESETOVRD需要300-500ns的有效时间。

三、CPLL复位

在相关时钟边沿信号被检测到之前,CPLL必须使用CPLLPD端口来下电。在CPLLPD被释放后,CPLL在使用之前必须进行复位。每个GTX通道都有3个专用端口用来CPLL复位。如下图:

CPLLRESET :CPLL的复位输入。推荐设计是一个时钟周期。

CPLLLOCK :拉高时,表示CPLL的复位完成。

内部CPLL复位信号:低有效。但是由GTX内部电路产生的真正的CPLL复位必须比CPLLRESET高脉冲时间要长。这个时间跟带宽、时钟频率等有关。

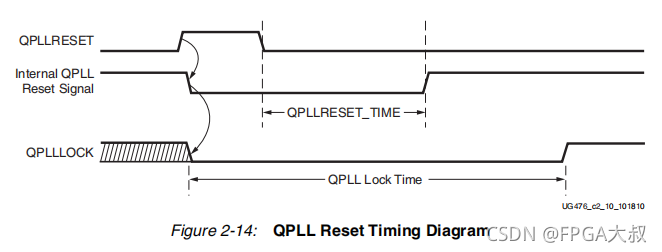

四、QPLL复位

QPLL复位大致与CPLL相同。放张图:

五、GTX TX初始化与复位

开门见山的说:GTX的TX复位只能使用顺序复位模式(Sequential mode )。

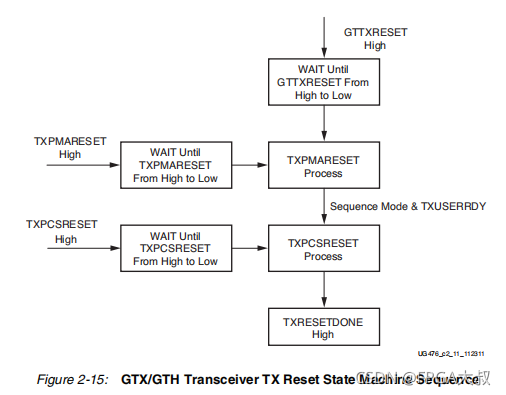

GTX的TX使用一个复位状态机来控制复位过程。TX复位分为两部分:TX PMA和TX PCS。

回忆下(1)GTX基本知识所介绍的:GTX的TX和RX均有PMA+PCS两个子层组成。

在整个PMA和PCS中,都由这个复位状态机按顺序执行复位。如下图:

使用TXPMARESET来对TX进行复位,TXRESETDONE拉高表示复位完成。

直到TXUSERRDY被检测为高时,TX复位状态机才对PCS进行复位。但是,驱动TXUSERRDY为高需满足以下条件:

1. 所有应用到的时钟包括TXUSRCLK/TXUSRCLK2必须稳定,或者locked(在PLL/MMCM被使用的时候)

2. 用户接口已经准备好传输数据到GTX。

5.1 GTX TX复位和初始化的端口信号

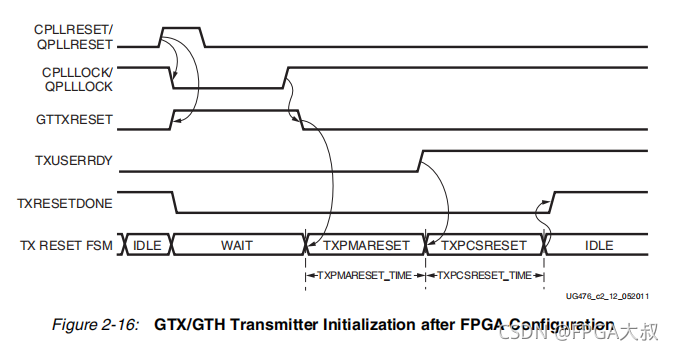

5.2 GTX TX复位对配置完成的响应

TX复位必须满足下列条件:

1. 使用顺序复位模式,GTRESETSEL必须为低。.

2. GTTXRESET必须使用。

3. 在复位完成前(TXRESETDONE拉高),TXPMARESET和TXPCSRESET 必须驱动为低不变。

4. 在PLL locked之前,GTTXRESET不能被驱动为低。

如果加载配置时,复位模式默认为顺序复位模式,在配置加载后等待最少500ns,C/QPLLRESET 和GTTXRESET 就可以被断言了。

如果复位模式为single mode,用户必须:

1. 在配置加载完成后,等待最少500ns。

2. 将复位模式改为顺序复位模式 Sequential mode。

3. 再等待300-500ns。

4. 断言 C/QPLLRESET和 GTTXRESET。

推荐的设计是使用来自相关的CPLL或者QPLL的PLLLOCK 来释放GTTXRESET由高到低。

TX复位状态机等GTTXRESET拉高,开始TX复位,直到GTTXRESET被释放低为止。

如下图所示:

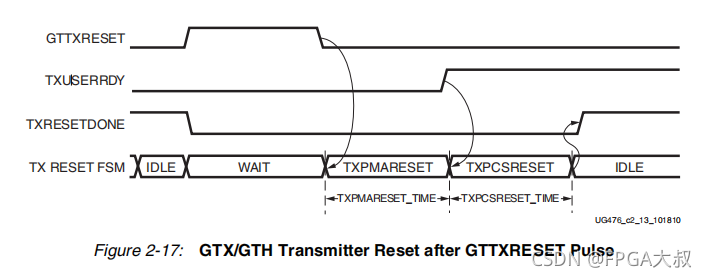

5.3 GTX TX复位对GTTXRESET脉冲的响应

GTX允许用户在任意时刻对TX进行复位,只需要给GTTXRESET一个有效的高脉冲信号。 TXPMARESET_TIME和 TXPCSRESET_TIME 可以被设置为静态的也可以通过DRP端口来动态设置以适配在申请 GTTXRESET之前要求的复位时间。

当使用GTTXRESET时必须满足以下条件:

1. 使用sequential mode必须将GTRESETSEL置低。

2. 在复位完成之前,TXPMARESET 和 TXPCSRESET 必须一直为低。

3. 相关 PLL必须 locked。

4. GTTXRESET的推荐设计是一个时钟周期脉冲。

5.4 GTX TX 模块复位

TX PMA和 TX PCS 可以单独进行复位。在 TXPMARESET 或者 TXPCSRESE复位过程完成之前,TGTTXRESET必须保持为低。驱动TXPMARESET从高到低来启动PMA复位程序, 在TXPMARESET复位过程中,TXPCSRESET必须保持为低。

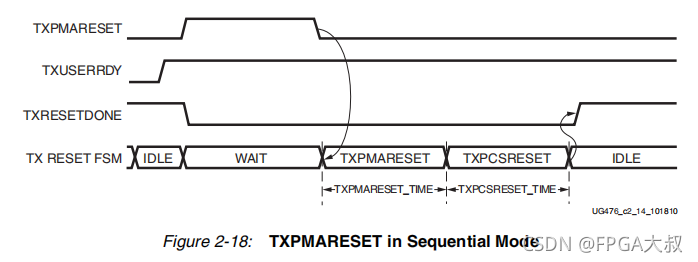

在顺序复位模式,复位状态机在PMA复位完成后,(如果TXUSERRDY为高)自动开始PCS复位。如下图:

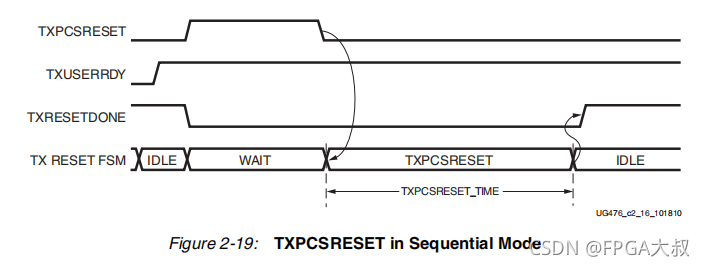

当TXUSERRDY为高时,驱动TXPCSRESET由高到低来启动PCS复位程序。在PCS复位过程中,TXPMARESET 必须保持为低。

在顺序复位模式,复位状态机仅复位PCS,如下图:

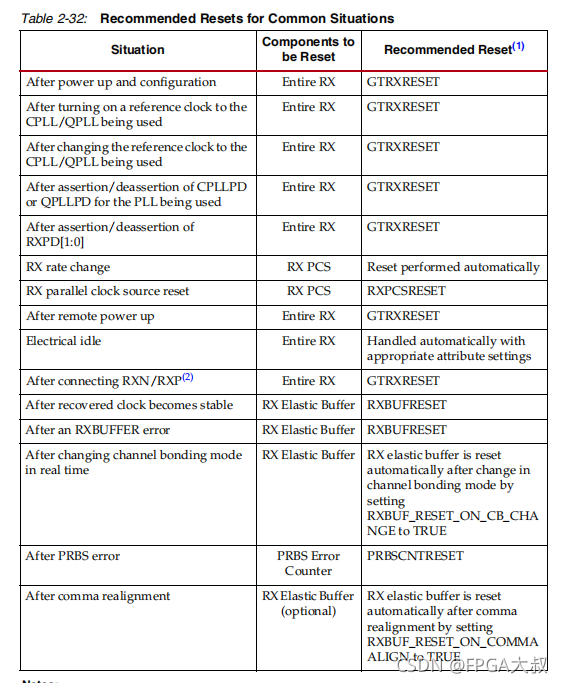

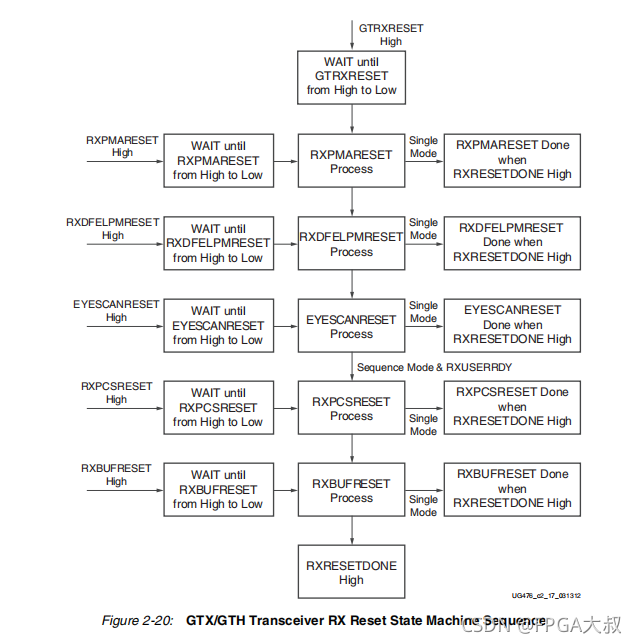

六、RX复位与初始化

已经快11点了,累了,溜了溜了,,,放张图:

结论

由GTX核分别输出了发送端TX和接收端RX的初始化完成信号:

TX: gt0_tx_fsm_reset_done_out(output)

RX: gt0_rx_fsm_reset_done_out(output)

直接使用这两个信号就好,TX复位完成就可以开始发送数据,RX复位就可以接收数据。

也可以加个信号 GT_RESET_DONE;

assign GT_RESET_DONE = gt0_tx_fsm_reset_done_out && gt0_rx_fsm_reset_done_out;

先用起来,后面再深入研究,不过了解了复位过程发现还是有点意思~

OK,前面说了一大堆结论却还是很简单的~

拿去搬砖吧~

审核编辑:汤梓红

-

FPGA

+关注

关注

1646文章

22097浏览量

620720 -

数据

+关注

关注

8文章

7264浏览量

92403 -

Xilinx

+关注

关注

73文章

2185浏览量

127133

发布评论请先 登录

gtx是光纤吗

详解Xilinx的10G PCS PMA IP

【米尔-Xilinx XC7A100T FPGA开发板试用】Key-test

Verilog 测试平台设计方法 Verilog FPGA开发指南

基于Xilinx ZYNQ7000 FPGA嵌入式开发实战指南

【米尔-Xilinx XC7A100T FPGA开发板试用】测试一

将ADC32RF42 EVM与xilinx ZC706开发板直接相连,JESD204B时钟无法建链成功,为什么?

采用Xilinx FPGA的AFE79xx SPI启动指南

【米尔-Xilinx XC7A100T FPGA开发板试用】+04.SFP之Aurora测试(zmj)

【米尔-Xilinx XC7A100T FPGA开发板试用】+01.开箱(zmj)

Xilinx 7系列FPGA PCIe Gen3的应用接口及特性

Xilinx FPGA平台GTX简易使用教程(三)

Xilinx FPGA平台GTX简易使用教程(三)

评论