在DSP 应用系统中,需要大量外扩存储器的情况经常遇到。例如,在数码相机和摄像机中,为了将现场拍摄的诸多图片或图像暂存下来,需要将 DSP 处理后的数据转移到外存中以备后用。从目前的存储器市场看,SDRAM 由于其性能价格比的优势,而被 DSP 开发者所青睐。DSP 与 SDRAM 直接接口是不可能的。

FPGA(现场可编程门阵列)由于其具有使用灵活、执行速度快、开发工具丰富的特点而越来越多地出现在现场电路设计中。本文用 FPGA 作为接口芯片,提供控制信号和定时信号,来实现 DSP 到 SDRAM 的数据存取。

1 、SDRAM 介绍

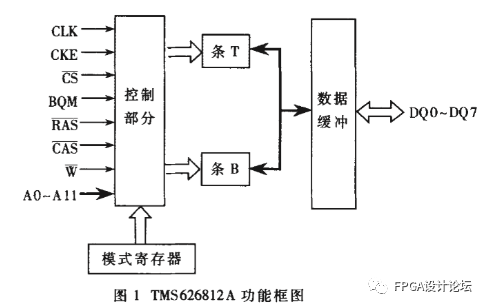

本文采用的 SDRAM 为 TMS626812A,图 1 为其功能框图。它内部分为两条,每条 1M 字节,数据宽度为 8 位,故存储总容量为 2M 字节。

所有输入和输出操作都是在时钟 CLK 上升沿的作用下进行的,刷新时钟交替刷新内部的两条 RAM。TMS626812A 主要有六条控制命令,它们是:条激尖 / 行地址入口、列地址入口 / 写操作、列地址入口 / 读操作、条无效、自动刷新、自动刷新。SDRAM 与 TMS320C54x 接口中用到的命令主要有:MRS、DEAC、ACTV、WRT-P、READ-P 和 REFR。这里,设计目的就是产生控制信号来满足这些命令的时序要求。关于 TMS626812A 的具体说明可以查看其数据手册。

2 、SDRAM 与 TMS320C54x 之间的通用接口

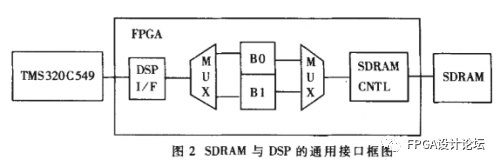

图 2 是 DSP 与 SDRAM 的通用接口框图,图中 DSP I/F 代表 TMS320C54x 端接口单元,SDRAM CNTL 代表 SDRAM 端接口控制单元。SDRAM 被设置成一次性读写 128 个字节,而 DSP 一次只读写一个字节,因而建立了两个缓冲区 B0、B1 来缓存和中转数据。B0、B1 大小都为 128 字节,而且映射到 DSP 中的同一地址空间。

尽管 B0、B1 对应于同一地址空间,但对两个缓冲区不能在同一时刻进行合法访问。实际上,当 B0 被 DSP 访问时,B1 就被 SDRAM 访问,反之也成立。若 DSP 向 B1 写数据,SDRAM 就从 B0 读数据;而当 SDRAM 的数据写到 B0 中时,DSP 就从 B1 读数据。两者同时从同一缓冲区读或写都将激发错误。上边所述的数据转移方式有两种好处:一是加速了 TMS320C54x 的访问速度,二是解决了二者之间的时钟不同步问题。

3 、FPGA 中的硬件设计

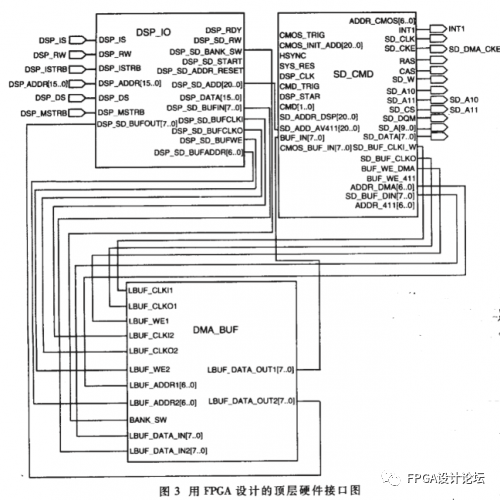

TMS320C54x 为外部存储器的扩展提供了下列信号:CLK、CS、AO~A15、D0~D15、RW、MATRB、ISTRB、IS,而 SDRAM 接收下列信号:CLK、CKE、CS、CQM、W、RAS、CAS、A0~A11。由于两端控制信号不同,需要在 DSP 与 SDRAM 之间加上控制逻辑,以便将从 DSP 过来的信号解释成 SDRAM 能够接收的信号,图 3 是用 FPGA 设计的顶层硬件接口图。

图中主要由三个模块:DSP-IQ、DMA-BUF 和 SD-CMD。其中 DSP-IO 是 DSP 端的接口,用来解码 TMS320C54x 发送的 SDRAM 地址和命令。DMA-BUF 代表缓冲区 BO、B1。SD_CMD 模块用来产生 SDRAM 访问所需的各种信号。

DSP_IO 模块又包括 IO_DMA、DSP_BUF 和 DSP_READ。IO_DMA 产生 SDRAM 的命令信号,即图 3 中的 DSP_RDY、DSP_SD_RW、DSP_SD_BANK_SW、DSP_SD_ADDR[20..0]、DSP_SD_ADDR_RESET、DSP_SD_START。DSP_BUF 产生访问 B0、B1 的地址、数据和控制信号,图 3 中指 DSP_SD_BUFCLKI、DSP_SD_BUFCLKO、DSP_SD_BUFWE、DSP_SD_BUFADDR[6..0]、DSP_SD_BUFIN[7..0]。DSP-READ 子模块用来控制 DSP 的读写方向。

DMA_BUF 分为 B0、B1 两个缓冲区,用来进行数据传送,每个缓冲区的输入输出信号包括:CLKI、CLKO、WE、ADDR[6-0]、DATA_IN[7-0]、DATA_OUT[7-0]。BANK_SW 是一个开关信号,用于 DSP 和 SDRAM 对 B0、B1 的切换访问。

SD_CMD 模块包括刷新、读、写功能。当 DSP 芯片发出 SDRAM 读命令时,128 字节的数据从 SDRAM 中读出来并被存储到 B0 或 B1 中,当 DSP 发出写命令之时,128 字节的数据传到 B0 或 B1 之中并被最终写到 SDRAM 中。

4 、软件设计

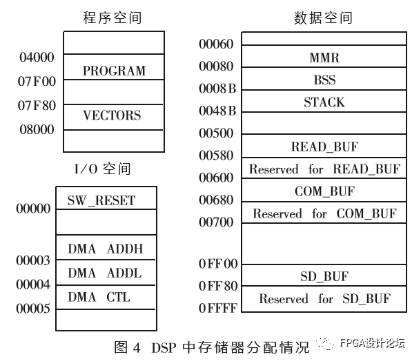

TMS626812A SDRAM 有两兆字节的存储容量。所以 DSP 用两个 I/O 地址向 FPGA 传送访问 SDRAM 的高低地址。此文中,该两个 I/O 地址对应用图 4 中的 03h(DMA_ADDH)和 04h(DMA_ADDL)。另外,还有一个 I/O 地址(图 4 中的 05h)用来向 FPGA 传送命令产生 SDRAM 访问的信号。

DSP 向 SDRAM 写数据时的操作步骤如下:

(1)数据先被写到 B0 或 B1。

(2)SDRAM 的访问地址经由 DSP 的 I/O 地址 DMA_ADDH 和 DMA_ADDL 发送到 FPGA 中。

(3)DSP 向 FPGA 发出一个命令(I/O 地址为 DMA_CTL)产生控制信号,使 SDRAM 从 B0 或 B1 中读取数值。

DSP 从 SDRAM 读数据的操作步骤如下:

(1)DSP 传送访问 SDRAM 的地址。

(2)DSP 经由 FPGA 传送一个命令,使得数据从 SDRAM 中读到 FPGA 中。

(3)DSP 从 B0 或 B1 中读得数据。

图 4 为 DSP 中与数据传送相关的各类存储器的分配情况。

具体设计时,应参考相关资料进行补充。不同的 DSP 与不同类型的 SDRAM 接口时,会有细微的区别,电路设计完毕后要进行认真而多方面的测试。

责任编辑:xj

原文标题:将FPGA作为接口芯片,如何实现DSP和SDRAM数据读取?

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

-

dsp

+关注

关注

558文章

8166浏览量

359276 -

FPGA

+关注

关注

1646文章

22097浏览量

620707 -

芯片

+关注

关注

460文章

52736浏览量

444119 -

SDRAM

+关注

关注

7文章

443浏览量

56502

原文标题:将FPGA作为接口芯片,如何实现DSP和SDRAM数据读取?

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

如何使用QSPI模块读取特殊规则的数据(NCV7725B)?

ADMT4000参照示例读取圈数数据正常,但是断电后再次上电重新读取,发现读数返回为0,请问可能是啥原因啊?

AI大模型深入储能电网,破解能源管理“不可能三角”

STM32H743或者是STM32F767读取NAND时候直接将数据存放到SDRAM中会出错,请问NAND跟SDRAM不能同时访问么?

SDRAM控制器设计之异步FIFO的调用

ADS8363数据输出引脚上依然看不到数据跳变,为什么?

ADS8688转换结果不正确,有哪些可能的原因?

HDC1080损坏的可能原因有哪些?

ADC3663在40Mhz时,数据读取出现错位现象,怎么解决?

LabView怎么保存已经读取的数据方便下次接着用

无论多少G以后,都不可能没有200G

变不可能为可能:如何实现DSP和SDRAM数据读取

变不可能为可能:如何实现DSP和SDRAM数据读取

评论