从雷达到WiFi和对讲机,RF设计已成为我们日常生活中的固定设备,从而使RF PCB布线指南成为我们日常设计中的固定设备。射频范围内的频率范围从数千到数十亿Hz,并且这些频率存在于大量的模拟/混合信号设备中。板不必出现在通信设备中即可被归类为RF电路,但是许多相同的设计规则将适用。

射频PCB布线指南:射频信号和您的叠层

布线RF板以确保信号完整性与设计正确的层堆栈和铺设走线一样重要。通过在PCB中放置正确的叠层,可以抑制信号线中的传输线效应。

虽然通常根据数字信号进行讨论,但是当走线用作传输线时,阻抗不连续处的信号反射会影响模拟信号。当沿着互连的传播延迟大于模拟信号振荡周期的四分之一时,您将需要担心传输线的影响,并确保迹线阻抗匹配。

尽管模拟信号迹线中的反射信号会自然衰减,但模拟迹线会不断被谐波源泵浦,如果在阻抗不连续处反射,反射信号会在迹线中形成驻波。信号走线中的自然衰减只会衰减共振时的最大振幅,而不能完全消除共振。

传输线上的任何模拟信号谐振都可以沿着走线形成驻波(取决于几何形状),从而产生高振幅电场,该电场可以在电路板的其他区域引发噪声。如果走线与源和负载组件的阻抗匹配,则可以消除此问题。

那么,如何确保走线始终保持阻抗匹配?首先,应在层堆叠中使用阻抗控制设计。这样可以确保在信号层中布线的走线在特定公差范围内具有定义的值。您只需要担心源和负载组件的阻抗与此值匹配。换句话说,如果互连末端的一个组件的阻抗与信号走线的阻抗不同,则必须补偿该组件的阻抗,而不是走线本身。

一些射频路由基础知识

由于走线的阻抗非常重要,因此您的布线技术应考虑与以下因素有关的所有因素:

l 来自其他走线/组件的EMI,对外部振荡磁场的敏感性以及电路板辐射的EMI

l 电源与地之间的去耦

l 防止射频信号走线之间的耦合

l 任何会增加走线,电源和负载之间的阻抗失配的因素

l 防止会强烈辐射到电路板其他区域或外部电路板的共振

l 避免尖锐的形状以消除阻抗不连续

l 对RF信号使用屏蔽走线

l 通过同一层和其他层上的间隙将RF迹线分开

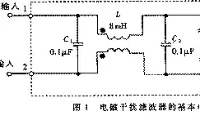

在高频下,RF信号可能会影响其他电路,也可能会受到其他信号的影响。这就是保护射频走线重要的原因。关键方法包括良好的接地,屏蔽和滤波。

尽管这是一个很高的要求,但您无法始终满足所有要求。以下几点应引起更多关注,取决于您的电路板的特定应用。

尽管RF PCB布线指南的清单很广泛,但以下是一些需要考虑的重要指南:

为了抑制从电路到电源网络的辐射,可以使用接地的过孔将电源层包围。将电源平面放置在两个接地平面之间也是一个好主意,因为这将使整个板上的电源平面和接地平面充分解耦。

对于更高频率的RF电路,承载模拟信号的走线将需要很短,以防止传输线影响。线之间的间距应尽可能大,并且不应在很长的距离内将它们靠近布置。平行微带走线之间的耦合随着平行布线距离的增加和分离距离的减小而增加。

一旦计算出给定叠层所需的走线几何形状,就应尽量减少走线上的过孔使用,因为每个过孔都会增加互连的阻抗。除了增加阻抗外,过孔上留下的任何短线都将充当高频谐振器。为了防止在存根中形成驻波,因为存根中的谐振信号可以充当强辐射体或天线,因此应对通孔进行反向钻孔。

如果需要将RF信号线布线到另一层,则可以并联使用两个过孔,以使总的额外电感和阻抗最小化。并联的两个通孔的总阻抗和电感为单个通孔的一半。当由于布线限制而需要在RF信号线中放置弯头时,您将需要使用至少为走线宽度3倍的弯头半径。这将最小化因弯曲走线而引起的阻抗变化。

射频板作为混合信号设备

除非您的RF板是多板系统的一部分,否则您的RF PCB可能是混合信号设备。有些设备是例外,例如RF放大器。因此,在使用这些系统时,您将需要考虑标准的混合信号设计技术。其中一些设备将具有无线功能,因此无线设计规则也将在您的设计过程中发挥作用。

对于RF设备,您可能会在电路板上包括其他支持RF组件并提供更多功能的模拟电路。在这种情况下,您应该尝试将敏感的RF组件与其他模拟组件分开,以避免将模拟返回信号路由到敏感的RF电路块下面。

您需要遵循混合信号设计的最佳实践,包括正确分割接地层,小心放置混合信号IC以及正确布置模拟电源和接地部分。您的目标应该是减少数字部分的噪声,使其不耦合到RF模拟部分,反之亦然。如果要设计这种类型的板,请注意一些用于布线混合信号PCB的基本规则。

出色的仿真程序包可从PCB设计程序包中获取数据,可轻松确定适合特定应用的最佳设计选择。射频设计中有很多问题要考虑,因为正确的设计选择在很大程度上取决于主要工作频率,以及射频板是否真的是混合信号板。

-

印制电路板

+关注

关注

14文章

968浏览量

42062 -

PCB打样

+关注

关注

17文章

2978浏览量

22711 -

电路板打样

+关注

关注

3文章

375浏览量

4930 -

abg欧博DFM

+关注

关注

20文章

3507浏览量

5654

发布评论请先 登录

符合EMC的PCB设计准则

高层数层叠结构PCB的布线策略

射频PCB布线准则用来抑制噪声

射频PCB布线准则用来抑制噪声

评论