毫无疑问,台积电目前是晶圆代工市场的老大,其最新的5nm工艺已经量产,并且独家拿下了苹果A14处理器的订单。不过,近两年三星也在不断的发力晶圆代工业务,不仅投入大笔资金建设先进的晶圆厂,同时也在工艺制程上加速的追赶。虽然,目前三星在市场份额上与台积电有着很大的差距,但是技术上的差距正在缩小。去年,台积电的创始人张忠谋在接受媒体采访时也表示,“台积电跟三星的战争绝对还没结束,我们只是赢了一两场battle(战役),整个war(战争)还没有赢。”

在2020世界人工智能大会期间的“万物智联·芯火燎原”人工智能芯片创新主题论坛上,三星电子高级副总裁Moonsoo Kang介绍了三星Foundry是如何通过提供最佳的Silicon(硅)解决方案来帮助AI芯片实现的。同时,他也介绍了三星Foundry在晶圆代工领域的概况及最新的进展。

▲Moonsoo Kang是Samsung Foundry市场战略团队负责人,负责与工艺技术、设计IP和封装解决方案有关的Samsung Foundry的战略规划和路线图

众所周知,近年来人工智能技术发展迅猛,而对于人工智能来说,算力是极为重要的关键因素之一。而对于人工智能计算来说,最开始的载体是通用型CPU,因为其相对于AI计算来说,非常的灵活。但是随着AI对于算力要求的越来越高,GPU开始成为了AI训练的首选计算架构,因为其相比CPU来说,更加的高效。而现在,相比GPU更加高效的定制型AI芯片开始逐渐成为了AI计算架构的首选。

目前,CPU仍占据当今数据中心AI推理(Inference)应用市场的主导地位,同时在数据中心AI训练应用市场,GPU则占据着主导地位。但是,根据研究机构的数据显示,预计到到2025年,定制型AI芯片将占据数据中心AI推理应用市场40%的份额,在数据中心AI训练应用市场,AI芯片的份额将达到50%。

在半导体芯片领域,我们可以看到的另一个趋势则是,高端制程的逻辑工艺变得越来越昂贵,先进工艺的硅片制造成本越来越高,这也使得先进技术节点的芯片设计成本也随之迅速增加。此外,并非采用先进的工艺,所有SoC内部的模块都能以相同的方式体验高级技术节点的好处。基于此,将传统的SoC芯片分解成分为多个小芯片(Chiplet),每个小芯片可以根据不同的需求选择不同的制程工艺,然后通过先进的封装技术将其封装在一起,这将使得芯片变得更加的高效和经济。

基于这两大趋势,Samsung Foundry也针对性的提供了相应的工艺、IP和封装技术来助力AI行业。

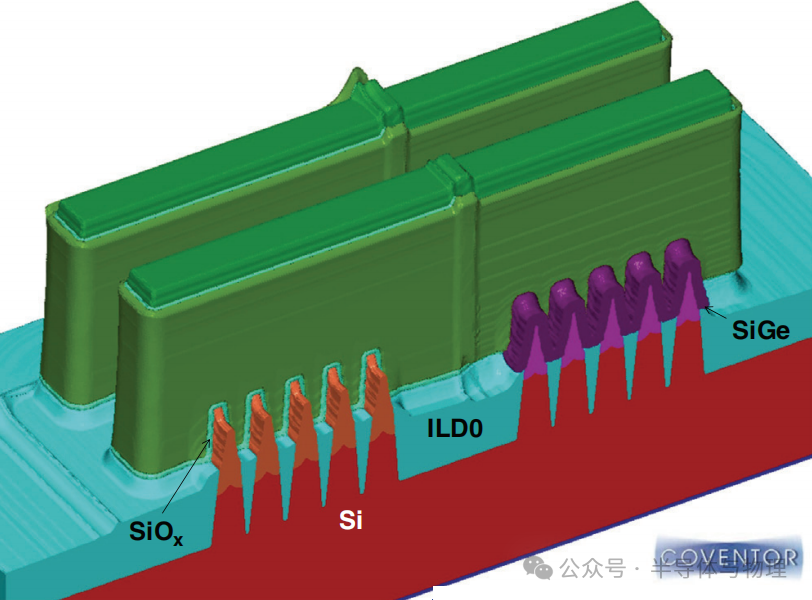

Moonsoo Kang首先介绍了Samsung Foundry在开发硅片先进制程技术方面的历史。比如,在行业中率先在32/28nm工艺上引进了High-K金属栅极技术;随后又在Foundry行业中领先推出第一款采用FinFET晶体管结构的14nm工艺芯片;第一款基于EUV光罩技术的量产7nm芯片;三星还全球率先在3nm技术中引入全环栅极晶体管技术(Gate-all-around transistor,简称GAA)。

Moonsoo Kang表示,硅晶体管多年其就已从平面(Planar)演变到立体的FinFET,来实现更好的面积和电压减缩,现在为了进一步改善并克服FinFET的短通道效应,Samsung Foundry引入了全环栅极的新型晶体管架构(GAA),借助这项新技术,可以进一步降低晶体管的工作电压,从而实现更节能的计算,这对于AI应用至关重要。同样,对于GAA器件,器件宽度会随着纳米片(Nano sheet)通道的垂直堆叠的增加而增加,因此可以实现性能提升的同时,而不会造成面积损失。这项技术可较小的硅片面积中实现更低的能耗和更多的计算能力,作为差别化的技术开发。

根据三星此前公布的数据显示,三星电子已经成功攻克了3nm和1nm工艺所使用的GAA工艺技术,其将在2021年推出基于3nm GAA工艺,相比现有的7nm工艺来说,可实现芯片面积减少45%,功耗降低50%或性能提高35%,预计将于2022年开启大规模量产。

此外,三星还拥有特殊工艺技术来提供差别化的解决方案。比如开发了28nm FD-SOI工艺,并提供了嵌入式非易失性存储器解决方案,包括eFlash和eMRAM。并且三星还正在18nm节点上开发第二代FD-SOI技术。此外,三星还在FD-SOI工艺上提供eNVM解决方案,以实现最终的低功耗应用。

“我们的FD-SOI技术为节能解决方案提供了平台,并且,借助嵌入式非易失性存储器(如eFlash和eMRAM),有可能实现模拟类型的内存计算,与传统的基于数字逻辑的计算架构相比,其功耗更低、面积更小、处理速度更快。”Moonsoo Kang介绍到。

但是,仅仅依靠先进的靠硅制程技术并不一定能提供出色的芯片,要制造出具有竞争力的芯片,还需要其他优秀的设计IP组合。

对此,Samsung Foundry提供了全套的设计IP来支持AI和HPC应用以及移动应用,比如,各种内存接口IP(例如HBM2/2e,GDDR6,DDR5/4和LPDDR5/4)、最高速度可达112G的Serdes IP、高速接口(例如PCIe,MIPI和USB)、Die-to-die接口串行和并行类型。

Moonsoo Kang表示,这些IP并非都是由我们的IP合作伙伴或Samsung Foundry内部开发,并经过所有测试和硅验证的。

此外,封装技术也是Samsung Foundry的技术解决方案的一部分。正如前面提到的,随着异构整合、Chiplet的发展,先进封装技术正成为推动芯片产业发展的关键技术。Samsung Foundry提供并继续开发各种针对AI产品优化的封装解决方案。

比如,可提供使用硅片和RDL中介层(interposer)连接逻辑和高带宽存储器,或逻辑和逻辑芯片的2.5D水平方向集成解决方案。该2.5D集成解决方案可从4个HBM集成进一步扩展到6和多于8个HBM集成。此外,Samsung Foundry还提供3D-TSV芯片堆叠集成解决方案,其中一个芯片位于另一个芯片的顶部,以实现极高的带宽。随着焊盘间距小至10um,3D集成解决方案将进一步扩展到晶圆对晶圆键合和芯片对晶圆技术。

对于AI芯片来说,性能尤为重要,但是功耗也是一个关键,尤其是对于耗电量巨大的数据中心类型的AI芯片而言。因此需要提供优秀的电源完整性(PI)解决方案。

随着计算能力的提高,开关噪声或功率纹波成为关键问题,作为一种解决方案,晶体管附近的高密度硅电容器可以减少电源噪声并提高PI。Samsung Foundry提供了各种电容器解决方案来帮助增强PI,具有高电容密度的集成堆栈电容器(Integrated Stack Capacitor)可以集成在硅片中介层内部或作为分立芯片。集成的堆栈电容器可以显著改善输电网络的峰值阻抗和电压降(如下图片所示)。还提Samsung Foundry供MIM(金属绝缘体金属)电容器和EPS(嵌入式无源基板),以进一步增强电源完整性。

以上,我们介绍了Samsung Foundry的硅工艺技术,设计IP和封装技术,但是,这些技术组件不只是作为离散组件提供,它们是一个完整且客户友好的生态系统,简称为SAFE(Samsung Advanced Foundry Ecosystem),可提供“一站式”解决方案。

Moonsoo Kang表示,百度的昆仑AI芯片就是采用了三星SAFE平台,成功开发了出了同类最佳的AI芯片,该产品采用了Samsung Foundry的14nm逻辑工艺,SAFE可靠的IP解决方案和设计方法和HBM一起构建在2.5D硅片中介层PKG。

根据此前的资料显示,百度昆仑AI芯片基于三星14nm工艺,支持PCIE 4.0*8,内建HBM内存、512GB/s内存带宽,性能高达260TOPS,功耗仅150W。去年下半年百度昆仑AI芯片就已成功流片,目前已经成功量产,并应用于百度的智能云业务。

责任编辑:pj

-

芯片

+关注

关注

460文章

52736浏览量

444139 -

AI

+关注

关注

88文章

35758浏览量

282456 -

人工智能

+关注

关注

1810文章

49221浏览量

251540

发布评论请先 登录

Nexperia推出采用铜夹片封装的双极性晶体管

Cadence UCIe IP在Samsung Foundry的5nm汽车工艺上实现流片成功

多值电场型电压选择晶体管结构

nRF7002是我们独特的Wi-Fi产品组合中的第一款设备

互补场效应晶体管的结构和作用

Samsung Foundry推出第一款采用FinFET晶体管结构的14nm工艺芯片

Samsung Foundry推出第一款采用FinFET晶体管结构的14nm工艺芯片

评论