在数据指数级增长对智能化、灵活应变的网络和数据中心解决方案提出极高要求的今天,全新 Virtex UltraScale+ VU23P FPGA 为行业提供了所需的最大吞吐量、强大的数据处理能力以及灵活性优势,使其可以适应不断演进发展的连接标准,并满足当前与未来需求。

赛灵思公司(Xilinx, Inc.,(NASDAQ: XLNX))今日宣布推出专为联网和存储加速而优化的 UltraScale+ FPGA 产品系列最新成员Virtex UltraScale+ VU23P FPGA,通过独特方式综合多种资源,实现了更高效率数据包处理和可扩展的数据带宽,致力于为联网和存储应用突破性的性能。在数据指数级增长对智能化、灵活应变的网络和数据中心解决方案提出极高要求的今天,全新 Virtex UltraScale+ VU23P FPGA 为行业提供了所需的最大吞吐量、强大的数据处理能力以及灵活性优势,使其可以适应不断演进发展的连接标准,并满足当前与未来需求。

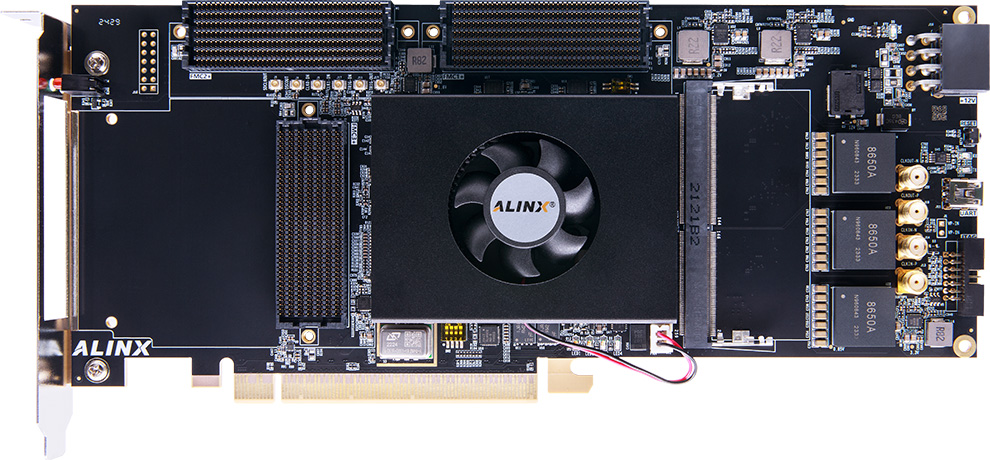

图:Xilinx 推出专为网络和存储加速优化的全新 Virtex UltraScale+ FPGA

VU23P 具备一系列卓越特性,它在 Virtex UltraScale 产品组合中实现了最高的查找表和嵌入式存储器(块 RAM)与 DSP 片之比,能够在尺寸和功耗不变的情况下进行高吞吐量处理。它采用 35mmx35mm 小型封装,尺寸小巧却能提供超强算力,使之成为SmartNIC 等高密度服务器环境的理想选择。该器件的 58G PAM4 收发器可支持高达 200G 的 SmartNIC 和网络系统,采用最先进的 PCIe Gen 4 连接功能实现最大 I/O 带宽。借助 VU23P FPGA 加速,多种应用可以从中取得以下显著优势:

SmartNIC:通过将处理卸载到基于 FPGA 的 SmartNIC,用户能够大幅提升服务器性能、降低系统级总拥有成本( TCO ),同时实现快速的功能创新。采用 Virtex UltraScale+ VU23P FPGA 的 SmartNIC 能够根据工作负载情况实现高达 2x100G 的应用。小型封装选项则有助于灵活构建适用于高密度服务器集群的多样化解决方案。

NMVe-oF:NVMe over Fabrics,也称为 NVMe-oF 或光纤通道非易失性存储器标准,是一种在设计上使用NVMe 议通过网络架构将主机连接到存储的协议规范。Virtex UltraScale+ VU23P 能够针对多种类型的存储工作负载实现强化加速,包括数据压缩、数据解压缩、数据重复删除、排序器功能,同时提高总体存储利用率,最大限度减轻 CPU 负担。凭借小型封装和兼容 PCIe Gen 4 能力,这款新型 Virtex UltraScale+ FPGA 可提供无与伦比的单位面积性能,既实现了灵活部署,也降低了存储系统的总拥有成本。

融合接入前传:在有线通信中,使用融合接入前传网关便于通过单个接口承载所有业务且不会劣化性能。新款 VU23P FPGA 赋予不同器件不同“个性”,可以针对网络基础设施中的每个部署进行选择,它支持多种类型的标准,包括以太网前传、OTN前传和PON前传。此外,集成型 PCIe Gen 4 IP 也为虚拟化现有无线电的基带处理提供了途径。

作为一款突破性器件,VU23P FPGA 将助力新一代联网和存储系统设计人员在竞争中迅速占领先机。如需了解更多信息,请访问:china.xilinx.com/vu23p

-

FPGA

+关注

关注

1646文章

22097浏览量

620717 -

赛灵思

+关注

关注

33文章

1797浏览量

132583

原文标题:赛灵思又一新款 16nm FPGA 面世, 专为速度而生!

文章出处:【微信号:FPGA-EETrend,微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

璞致电子 UltraScale+ RFSoC 架构下的软件无线电旗舰开发平台

AMD FPGA异步模式与同步模式的对比

AMD Spartan UltraScale+ FPGA 开始量产出货

赛灵思低温失效的原因,有没有别的方法或者一些见解?

ALINX 发布 AXVU13P:AMD Virtex UltraScale+ 高端 FPGA PCle 3.0 综合开发平台

易灵思FPGA产品的主要特点

AMD/Xilinx Zynq? UltraScale+ ? MPSoC ZCU102 评估套件

2.34纳秒超低时延,满足金融市场高频交易,AMD发布新一代金融加速卡

赛灵思宣布推出专为联网和存储加速而优化的 UltraScale+ FPGA 产品系列最新成员

赛灵思宣布推出专为联网和存储加速而优化的 UltraScale+ FPGA 产品系列最新成员

评论