时序逻辑电路的建立,保持时间裕量分析

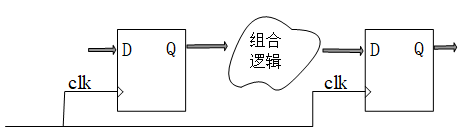

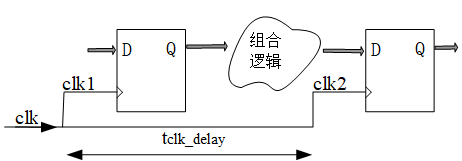

在Verilog里,时序逻辑电路即表示如下图所示的电路。前后两级寄存器之间有一个组合逻辑运算电路。

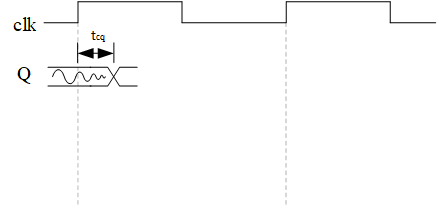

假设寄存器的建立时间要求为tsetup, 保持时间要求为thold, 输出延时为tcq。

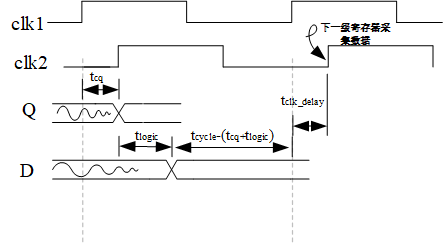

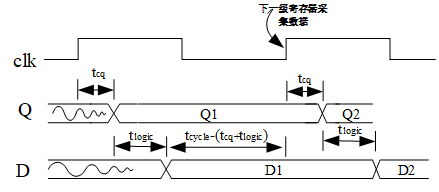

故对于第一个寄存器,时钟上升沿之后,经过时间tcq数据才从Q端输出。波形图示如下。

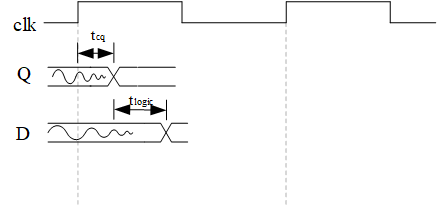

假设组合逻辑运算电路的运算耗时为tlogic。故运算后的数据在时钟上升沿之后经过时间tcq+tlogic才到达下一级寄存器的D端,图示如下。

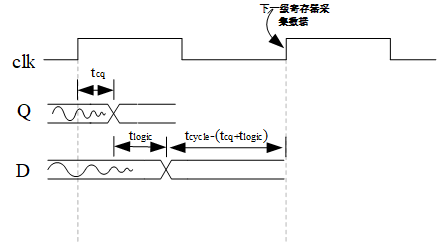

那么对于下一级寄存器在接下来到来的时钟上升沿采集数据,其必须要满足建立保持时间要求。

建立时间:既数据D至少需要提前于clk上升沿多长时间到来,数据的采集才不会出错。

从上述分析可得数据D提前于clk上升沿的时间为 tcycle-(tcq+tlogic)。

其中tcycle为时钟周期。

如果tcycle-(tcq+tlogic) >tsetup 那么建立时间要求就得到了满足。一般称tcycle-(tcq+tlogic) -tsetup 为建立时间裕量,为保证建立时间满足要求,裕量必须要大于0。

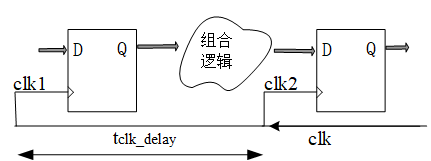

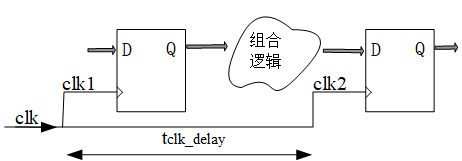

当然上述情况还忽略了时钟的延迟,即默认前后两级寄存器的clk都是同时到达。如果时钟存在正延时,即时钟的传播方向与数据传播方向一致,即电路如下图所示。clk从第一级到后一级寄存器的线路延时为tclk_delay。

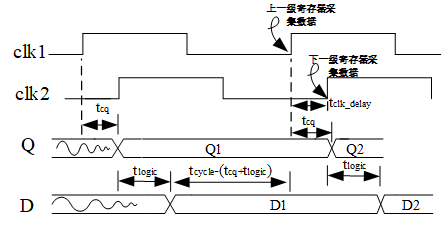

从而对应的时序如下。针对于下一级的寄存器来说,相当于建立时间裕量增加了tclk_delay,即建立时间裕量为tcycle-(tcq+tlogic) -tsetup+tclk_delay。这种情况对于建立时间是有好处的。

相反,如果时钟存在反向延时,即时钟的传播方向与数据传播方向相反,那么对于建立时间是不利的。此时的建立时间裕量为tcycle-(tcq+tlogic) -tsetup-tclk_delay。大家可自行画时序图分析,当作练习。

从上述对建立时间裕量的分析,可以发现,从前端设计的角度去分析,优化建立时间裕量可以靠减少两级寄存器之间的组合逻辑的延时去增大建立时间裕量。后面会有文章去根据示例来介绍优化方法,其中流水线设计就是一种优化方式。

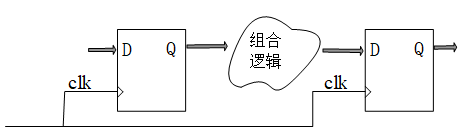

保持时间(thold):就是时钟上升沿之后,数据D还需要维持多长时间不变,寄存器对数据的采集才不会出错。还是对下面这个电路模型进行分析。

对于后一级寄存器来说,时钟上升沿之后,后一级D端的数据要得到改变,必须是上一级的数据Q输出了,并通过组合逻辑运算电路的延时,送到了D端。故在时钟上升沿之后,数据要经过时间tcq+tlogic才到达下一级寄存器的D端,故每次时钟上升沿之后,后一级寄存器的数据D可以维持不变的时间为tcq+tlogic。那么保持时间裕量为tcq+tlogic-thold。时序见下图。

从这可以看出,时序逻辑电路里面tlogic越大,对建立时间裕量不利,但对保持时间裕量有利。

同样,再考虑存在时钟延时对保持时间的影响。如下电路,即时钟存在正延时时。

分析后一级寄存器的保持时间裕量时,对应的时序变成如下。可以看到,相当于前级寄存器的clk比下一级寄存器的clk提前了tclk_delay时间,故数据D2提前到来了。保持时间裕量变成了tcq+tlogic-thold-tclk_delay。

可以看到时钟正向延时对建立时间要求有利,但对于保持时间要求是不利的。对于时钟反向延时,大家自行画图分析。

上面还有一个因素没有说明,就是时钟clk的抖动。因为时钟上升沿不可能每次都固定间隔时间tcycle到来一次。可能与这个时间有一个小小的偏差,但是不确定是提前到来还是延迟到来。这个偏差的时间为tjitter。如果考虑这个因素,建立时间与保持时间裕量都还要减掉这个抖动时间。故最终的建立时间与保持时间裕量计算公式入下(其中的tclk_delay为时钟正向延时):

建立时间裕量 tsetup_slack =tcycle-(tcq+tlogic) -tsetup+tclk_delay-tjitter

保持时间裕量 thold_slack =tcq+tlogic-thold-tclk_delay-tjitter

到这大家明白了,建立时间裕量与保持时间裕量就是一对矛盾的关系,我们需要通过优化时钟延时,组合逻辑延时来折中考虑这两个裕量。在裕量不满足要求时,可以选择增大时钟clk的周期,但这就降低了电路的运行速度。从而就要考虑时序优化,从前端考虑也就是两级寄存器之间的组合逻辑延时优化,比如简化组合逻辑,或者通过流水线设计,后面会通过实例介绍。

-

逻辑电路

+关注

关注

13文章

502浏览量

43471 -

寄存器

+关注

关注

31文章

5448浏览量

125475

原文标题:时序逻辑电路的建立,保持时间裕量分析

文章出处:【微信号:LF-FPGA,微信公众号:小鱼FPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

时序逻辑电路的主要故障分析

组合逻辑电路和时序逻辑电路比较_组合逻辑电路和时序逻辑电路有什么区别

时序逻辑电路的建立,保持时间裕量分析

时序逻辑电路的建立,保持时间裕量分析

评论