LMK04832-SP 是一款高性能时钟调节器,支持 JEDEC JESD204B,适用于太空应用。

PLL2的14个时钟输出可配置为使用器件和SYSREF时钟驱动7个JESD204B转换器或其他逻辑器件。SYSREF 可以使用直流和交流耦合提供。不仅限于JESD204B应用,14 个输出中的每一个都可以单独配置为传统时钟系统的高性能输出。

LMK04832-SP 可配置为在双 PLL、单 PLL 或时钟分配模式下运行,无论是否具有 SYSREF 生成或重新时钟。PLL2 可以与内部或外部 VCO 一起工作。

*附件:lmk04832-sp.pdf

高性能与在功耗和性能之间权衡的能力、双 VCO、动态数字延迟和保持等功能相结合,使 LMK04832-SP 能够提供灵活的高性能时钟树。

LMK04832-SP 采用 10.9 mm × 10.9 mm 64 引脚 CFP 封装。

特性

- 贴片 #5962R1723701VXC

- 总电离剂量 100 krad(不含 ELDRS)

- SEL 免疫 >120 MeV × cm ^2^ /毫克

- SEFI 免疫 >120 MeV × cm ^2^ /毫克

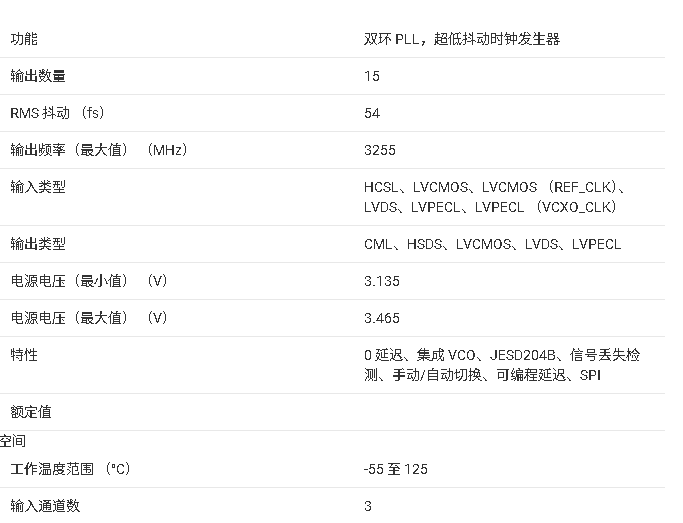

- 最大时钟输出频率:3255 MHz

- 多模:双 PLL、单 PLL 和时钟分配

- 6 GHz 外部 VCO 或分配输入

- 超低噪声,2500 MHz:

- 54 fs RMS 抖动(12 kHz 至 20 MHz)

- 64 fs RMS 抖动(100 Hz 至 20 MHz)

- –157.6 dBc/Hz 本底噪声

- 超低噪声,3200 MHz:

- 61 fs RMS 抖动(12 kHz 至 20 MHz)

- 67 fs RMS 抖动(100 Hz 至 100 MHz)

- –156.5 dBc/Hz 本底噪声

- PLL2

- PLL FOM 为 –230 dBc/Hz

- PLL 1/f 为 –128 dBc/Hz

- 相位检测器速率高达 320 MHz

- 两个集成VCO:2440至2600 MHz和2945至3255 MHz

- 多达 14 个差分器件时钟

- 多达 1 个缓冲 VCXO/XO 输出

- LVPECL、LVDS、2xLVCMOS 可编程

- 1-1023 CLKout分频器

- 1-8191 SYSREF 分频器

- SYSREF时钟的25 ps步进模拟延迟

- 器件时钟和SYSREF的数字延迟和动态数字延迟

- PLL1 的保持模式

- PLL1 或 PLL2 的 0 延迟

- 环境温度范围:–55 °C 至 125 °C

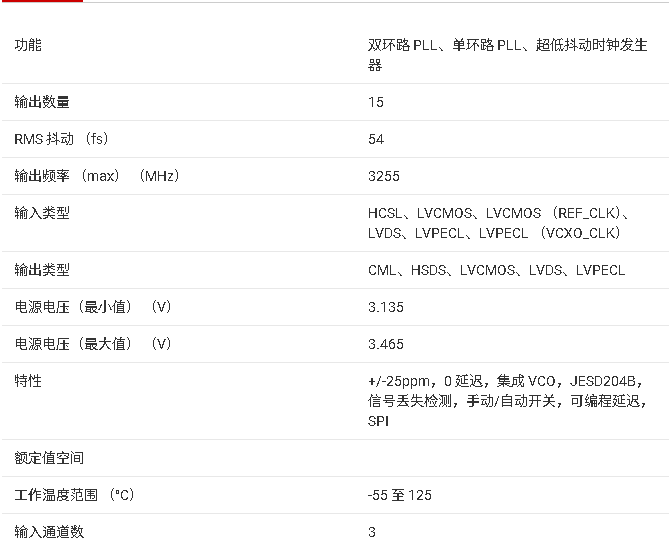

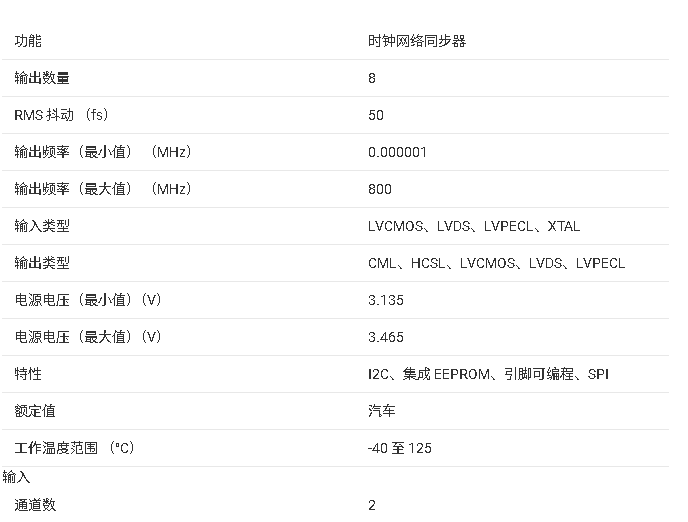

参数

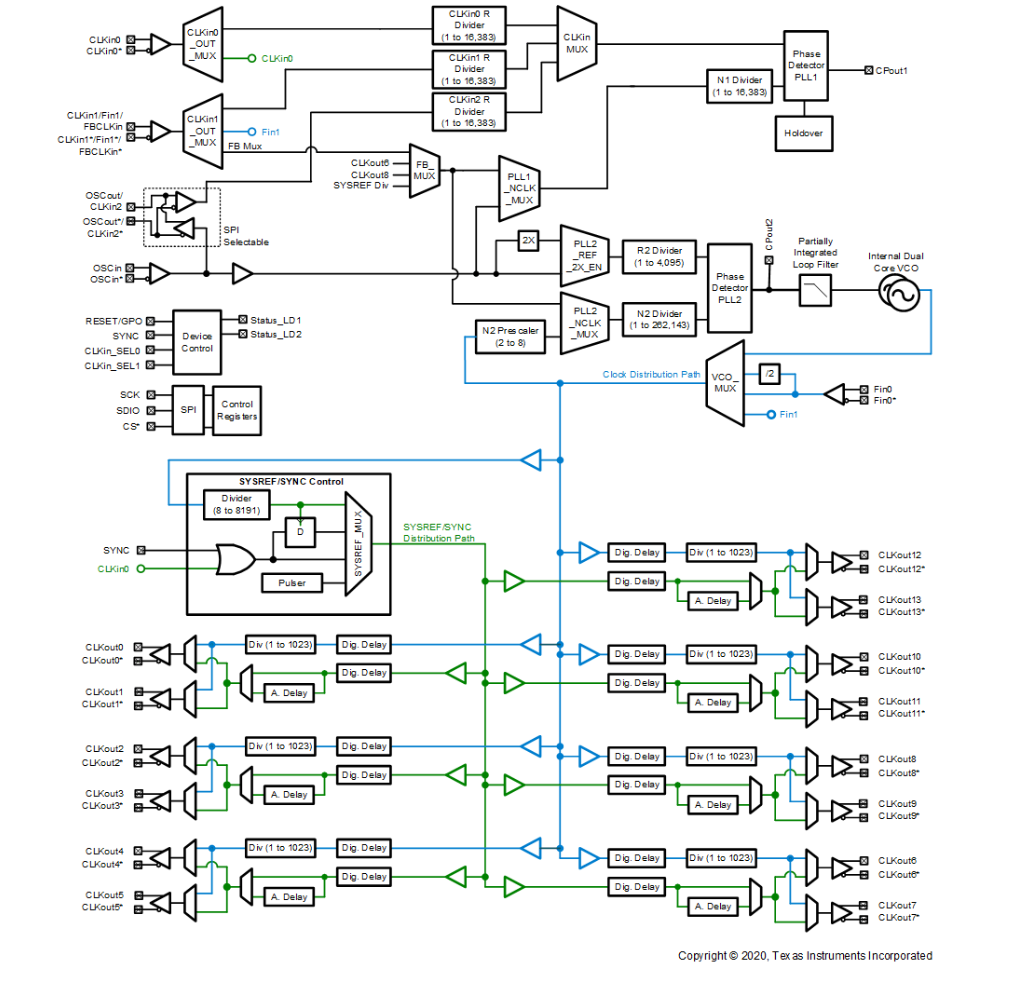

方框图

?1. 产品概述?

LMK04832-SP 是一款航天级超低噪声 JESD204B 双环路时钟抖动消除器,适用于高可靠性空间应用(如通信载荷、雷达成像等)。关键特性包括:

- ?辐射硬化?:总电离剂量 100 krad(ELDRS-free),抗 SEL/SEFI(>120 MeV·cm?/mg)。

- ?高性能时钟?:最大输出频率 3255 MHz,支持双 PLL、单 PLL 或时钟分配模式。

- ?超低抖动?:2500 MHz 下 RMS 抖动低至 54 fs(12 kHz–20 MHz)。

- ?多格式输出?:14 路差分时钟输出,支持 CML/LVPECL/LVDS/HSDS/LVCMOS 等可编程格式。

?2. 核心功能?

- ?双 PLL 架构?:

- ?PLL1?:外部 VCXO 参考,窄带宽(10–200 Hz)用于低频噪声清理。

- ?PLL2?:内部双 VCO(2440–2600 MHz 和 2945–3255 MHz),宽带宽(50–200 kHz)优化高频性能。

- ?JESD204B 支持?:可配置 7 对设备时钟/SYSREF 输出,支持确定性延迟和同步。

- ?0 延迟模式?:嵌套或级联架构确保输入/输出时钟相位对齐。

- ?冗余输入与保持模式?:支持 3 路参考时钟输入切换,在参考丢失时保持频率稳定(±0.71 ppm 典型精度)。

?3. 关键参数?

- ?电气特性?:

- 工作电压:3.3 V ±5%(-55°C 至 125°C)。

- 功耗:典型 780 mA(全功能模式)。

- 相位噪声:-230 dBc/Hz PLL FOM(PLL2)。

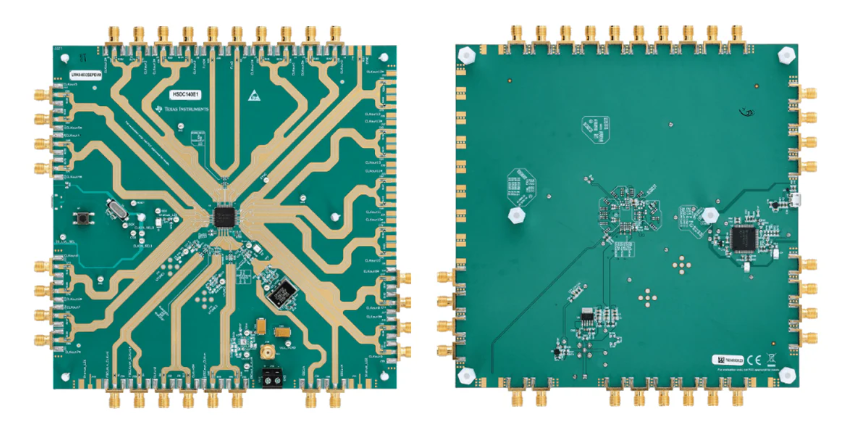

- ?封装?:64 引脚陶瓷扁平封装(10.9 mm × 10.9 mm),带金属盖密封。

?4. 应用设计?

- ?时钟分配?:支持外部 VCO(6 GHz 输入)或内部 VCO 模式。

- ?同步控制?:SYNC/SYSREF 路径支持脉冲、连续或请求模式,满足 JESD204B 初始化需求。

- ?动态延迟调整?:数字延迟(8–1023 周期步进)和模拟延迟(21 ps 步进)优化时序对齐。

?5. 开发支持?

- ?工具链?:TI 提供 Clock Architect(频率规划)、PLLatinum Sim(环路滤波设计)、TICS Pro(寄存器配置)。

- ?辐射认证?:通过 MIL-STD-883 总剂量测试和 JEDEC57 SEE 验证。

?6. 典型应用场景?

-

转换器

+关注

关注

27文章

9218浏览量

153272 -

逻辑器件

+关注

关注

0文章

93浏览量

20488 -

调节器

+关注

关注

5文章

885浏览量

48382 -

交流耦合

+关注

关注

0文章

38浏览量

12492 -

时钟系统

+关注

关注

1文章

115浏览量

12351

发布评论请先 登录

LMK04832配置时钟输出时,IDL和ODL怎么配置?有没有统一的做法?

LMK04832的时钟输出例如CLKOUT2_3两对时钟全部作为DEVICE CLOCK输出时频率只能是一致的吗?

LMK04832EVM开发板在设置0和1通道的时钟是只能输出一样的频率吗?

LMK04832 CMOS输出衰减怎么解决?

LMK04832-SP时钟抖动清除器

LMK04832-SEP符合JESD204B/C标准的航天级、超低噪声、双环路时钟抖动清除器数据表

LMK04832-SP符合JESD204B标准的航天级、超低噪声、双环路时钟抖动清除器数据表

带双环路PLL且符合JESD204B标准的LMK04832超低噪声时钟抖动清除器数据表

LMK04832SEPEVM评估模块技术解析与应用指南

?LMK1D210xL系列超低附加抖动LVDS缓冲器技术文档总结

?LMK05318B-Q1 芯片技术文档总结

?LMK04832-SEP 芯片技术文档摘要

?LMK04832-SP 文档总结

?LMK04832-SP 文档总结

评论