该CDCDB800是一款符合 DB800ZL 标准的 8 输出 LP-HCSL 时钟缓冲器,能够为 PCIe Gen 1-7、QuickPath 互连 (QPI)、UPI、SAS 和 SATA 接口分配参考时钟。SMBus 接口和八个输出使能引脚允许单独配置和控制所有八个输出。该CDCDB800是DB800ZL导数缓冲器,达到或超过DB800ZL规范中的系统参数。该器件还满足或超过DB2000Q规范中的参数。该CDCDB800采用6mm×6mm、48引脚VQFN封装。

*附件:cdcdb800.pdf

特性

- 8 个 LP-HCSL 输出,具有可编程集成 85Ω(默认)或 100Ω 差分输出端接

- 8 个硬件输出使能 (OE#) 控件

- PCIE Gen 7滤波器后的附加相位抖动:11.3fs,RMS(最大值)

- PCIE Gen 6滤波器后的附加相位抖动:16.1fs,RMS(最大值)

- PCIE Gen 5滤波器后的附加相位抖动:25fs,RMS(最大值)

- DB2000Q滤波器后的附加相位抖动:38fs,RMS(最大值)

- 支持通用时钟 (CC) 和单独基准 (IR) 架构

- 扩频兼容

- 输出到输出偏斜:< 50ps

- 输入到输出延迟:< 3ns

- 故障安全输入

- 可编程输出压摆率控制

- 3.3V 内核和 IO 电源电压

- 硬件控制的低功耗模式 (PD#)

- 电流消耗:最大 72mA

- 6mm × 6mm、48引脚VQFN封装

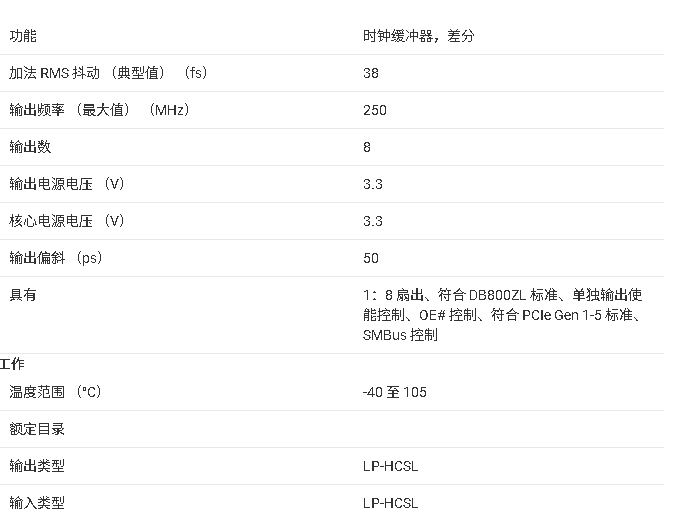

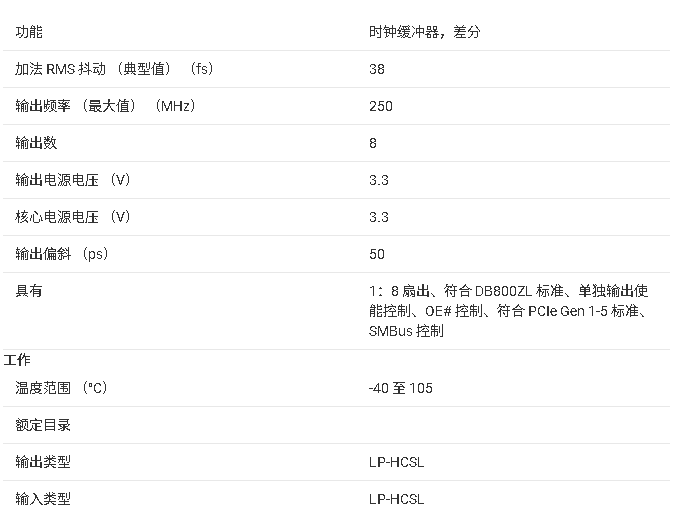

参数

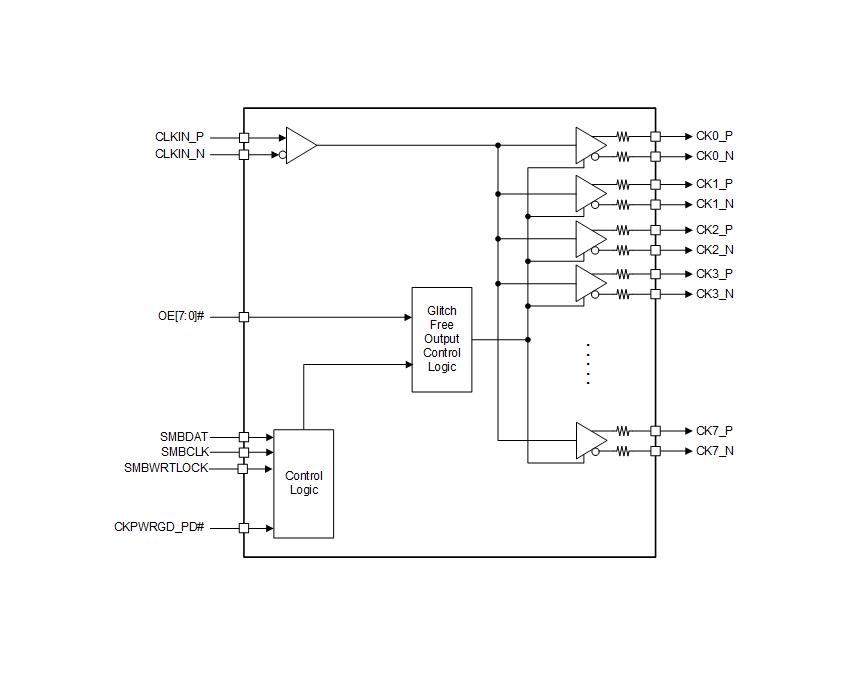

方框图

?1. 产品概述?

CDCDB800是德州仪器(TI)推出的DB800ZL兼容型8输出LP-HCSL时钟缓冲器,专为PCIe Gen 1至Gen 7、QPI、UPI、SAS及SATA接口设计。其核心特性包括:

- ?8路LP-HCSL输出?:支持可编程集成85Ω(默认)或100Ω差分终端阻抗。

- ?低抖动性能?:

- PCIe Gen 7滤波后加性相位抖动:11.3 fs(RMS,最大值)

- PCIe Gen 6滤波后:16.1 fs

- PCIe Gen 5滤波后:25 fs

- ?硬件控制?:8个独立输出使能(OE#)引脚,支持SMBus接口配置。

- ?封装?:6mm×6mm 48引脚VQFN封装。

?2. 关键参数?

- ?电气特性?:

- 工作电压:3.3V±5%(核心与IO)

- 最大功耗:72mA(全输出激活)

- 输出至输出偏移:<50ps

- 输入至输出延迟:<3ns

- ?热性能?:

- 结至环境热阻(RθJA):32.2°C/W

?3. 应用场景?

- 服务器(微服务器、塔式服务器、机架服务器)

- 存储设备(SAN、NAS、HBA卡)

- 硬件加速器

?4. 功能描述?

- ?输出控制?:通过SMBus寄存器或硬件OE#引脚独立启用/禁用每路输出。

- ?故障保护输入?:支持电源未接通时输入信号驱动。

- ?输出阻抗与压摆率调节?:

- 可编程选择85Ω或100Ω差分阻抗。

- 通过CAPTRIM寄存器调整输出压摆率,适应不同布线长度需求。

?5. 设计支持?

?6. 文档与支持?

- 提供TICS Pro软件用于寄存器配置。

- 完整数据手册包含引脚定义、寄存器映射及热性能曲线。

?7. 版本更新?

- 2025年8月修订版(Rev C)新增PCIe Gen 7兼容性验证。

-

接口

+关注

关注

33文章

9168浏览量

154642 -

时钟缓冲器

+关注

关注

2文章

172浏览量

51487 -

封装

+关注

关注

128文章

8918浏览量

146385 -

引脚

+关注

关注

16文章

1903浏览量

53805

发布评论请先 登录

什么是时钟缓冲器(Buffer)?时钟缓冲器(Buffer)参数解析

CDCDB803适用于第1代到第6代PCIe、符合DB800ZL标准的8输出时钟缓冲器数据表

CDCDB800适用于第1代到第6代PCIe、符合DB800ZL标准的8输出时钟缓冲器数据表

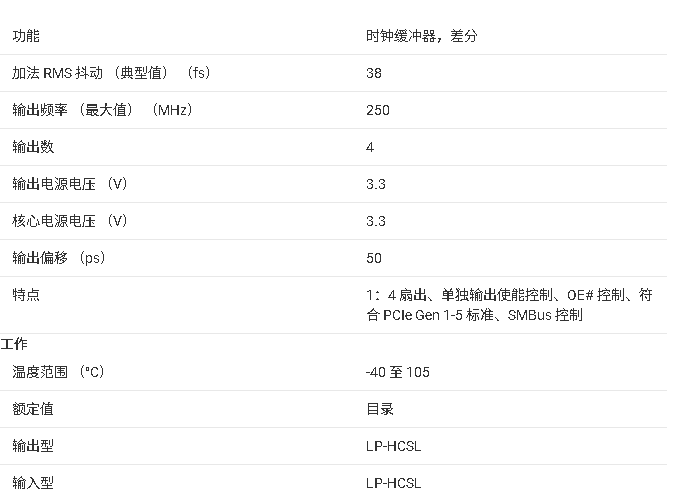

CDCDB400适用于第1代到第6代PCIe、符合DB800ZL标准的4输出时钟缓冲器数据表

CDCLVP1208八路LVPECL输出、高性能时钟2:8缓冲器数据表

符合CDCDB2000 DB2000QL标准的20输出时钟缓冲器,适用于PCIe第1代到第5代数据表

CDCDB800/803超低附加抖动、8路输出PCIe Gen1至Gen5时钟缓冲器

HAC946QN型高速时钟缓冲器

HACP1208QN型低抖动LVPECL时钟缓冲器

Diodes公司PCIe 6.0时钟缓冲器介绍

?CDCDB800 8输出时钟缓冲器技术文档总结

?CDCDB800 8输出时钟缓冲器技术文档总结

评论