本文要点

PCB 走线和 IC 走线中的阻抗控制主要着眼于预防反射。

防止互连路径上发生反射,可确保功率传输至负载,同时避免其他信号完整性问题。

使用集成场求解器的 PCB 设计软件可以评估阻抗匹配并提取互连网络参数。

信号完整性与阻抗匹配之间存在什么关系?信号完整性与阻抗匹配密不可分,精确的阻抗匹配对于确保功率顺利传输至 PCB 互连中的负载器件至关重要。信号完整性问题涉及潜在反射、EMI 和串扰等多种问题,并非所有信号完整性问题都能通过阻抗匹配得以解决。然而,要确保驱动端与接收端之间的信号准确传输,第一步是获得精确的互连阻抗计算结果。

为确保阻抗计算准确且走线几何形状能实现目标阻抗值,最佳方式是使用集成场求解器的 PCB 设计软件来分析互连阻抗。在电路层面验证阻抗匹配时,需通过 SPICE 仿真器计算等效电路阻抗。我们将在本文详细介绍阻抗匹配不良导致的问题,以及如何在设计软件中检查准确的匹配。

信号完整性问题与阻抗匹配

当信号沿互连走线传播时,需要通过阻抗匹配来防止反射。当互连与负载输入阻抗不匹配时,两者接口处会产生反射。但互连中的反射究竟意味着什么?更具体地说,哪些信号完整性问题可归因于阻抗失配?

当阻抗失配处发生反射时,产生的反射会引发多种信号完整性问题:

01

驻波与谐振现象:由于反射作用,长距离互连线上的特定频率会形成驻波,导致走线周围产生强烈的辐射。

02

符号间干扰:当信号在互连中来回反射时,信号会在接收端相互干扰从而产生失真。

01

向负载传输的功率会减少:当功率因阻抗失配而反射时,负载将无法获得正常工作所需的功率。对于数字信号而言,强烈的反射会阻碍逻辑电路完成状态切换。

按目标阻抗进行设计

要预防这些信号完整性问题,需要计算目标阻抗值。该目标阻抗取决于传输线的特性阻抗、负载电路的输入阻抗、任何较长的传输线或馈线,以及 PCB 中的驱动器件。

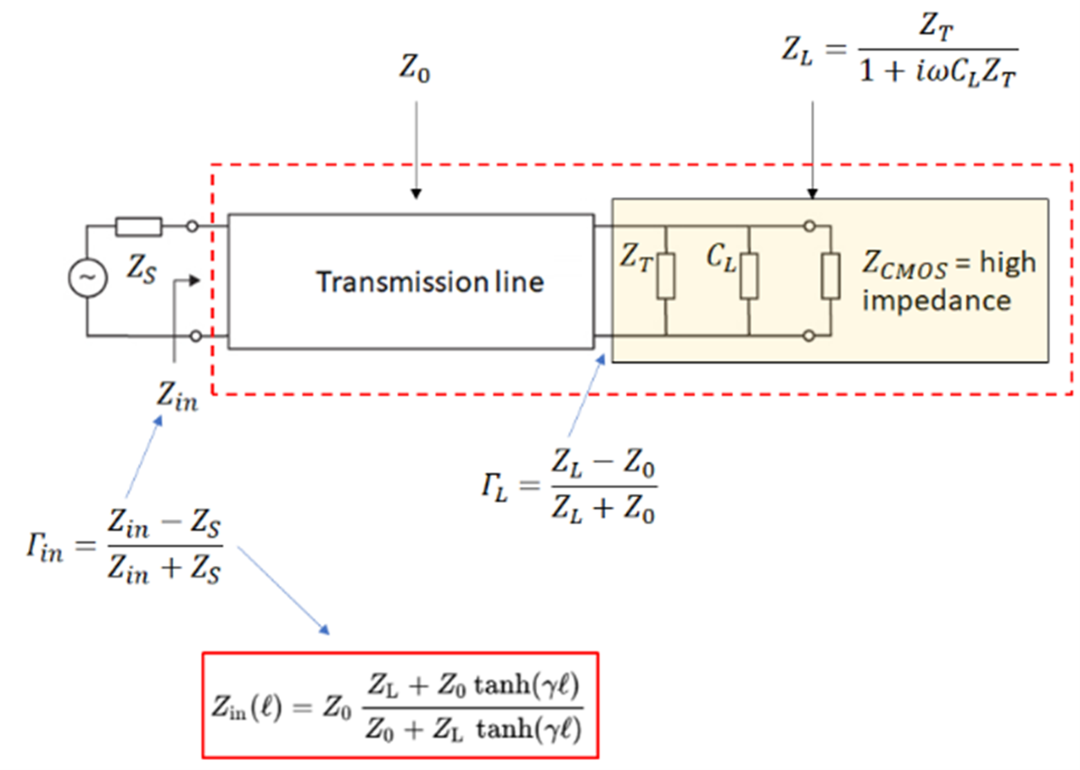

下图展示了与 CMOS 器件接口并采用源驱动的互连示例。有两处位置可能发生阻抗失配(源与传输线之间以及传输线与负载之间),每个接口处的阻抗目标值都是沿信号传输方向的输入阻抗。下图展示了各接口处的反射系数。

与 CMOS 器件接口的互连

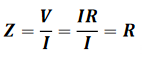

对于 CMOS 电路而言,输入阻抗是端接电阻(假设为并联元件)、负载输入电容以及 CMOS 输入阻抗(假设为无穷大)三者并联。因此,负载输入端的输入阻抗就是根据电路理论计算得出的并联等效阻抗。在驱动端,我们现在有一个与负载串联的传输线,需要计入线路长度才能获得精确的阻抗计算结果。了解了系统中每个元件的输入阻抗和特性阻抗后,现在可以计算每个接口的反射系数,从而确定哪些位置需要进行阻抗匹配。

短互连

当两个电路通过短传输线相连时,由于 tanh(0)=0,通常忽略传输线阻抗,此时输入阻抗即等于负载阻抗。实际应用中,确定目标阻抗时应考虑互连长度,因为源端的输入阻抗取决于线路长度。另一个原因与互连上的损耗形式有关:

01

长线路:长互连的损耗主要由吸收主导,包括铜箔粗糙度、趋肤效应损耗以及 PCB 基板中的介质损耗。

02

短线路:短互连的损耗主要由负载端的反射主导,在 S 参数中表现为较高的回波损耗。

对于短线路而言,主要的损耗机制来源于互连接收端的反射,这完全由阻抗匹配决定。基于上述原因,设计人员需要借助工具在布局前仿真和布局后仿真中评估阻抗失配情况。

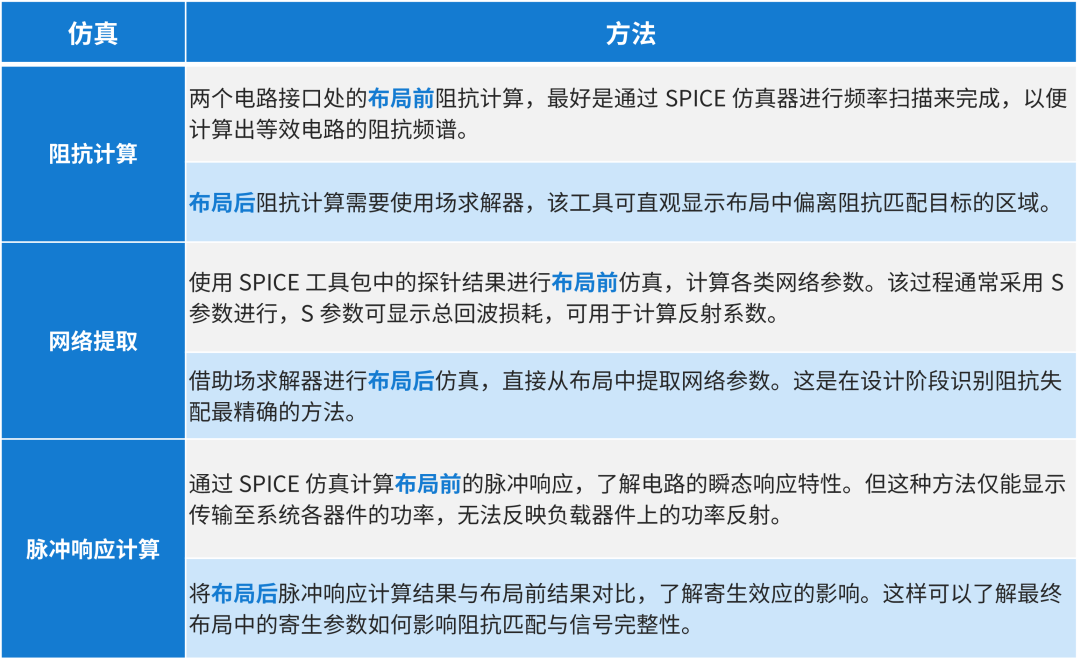

如何评估阻抗匹配

对电路应用阻抗匹配网络或尝试按照目标阻抗设计互连时,都应使用内置仿真引擎对设计进行仿真。分别查看电路原理图和 PCB 布局,可以在布局前仿真和布局后仿真中检查阻抗匹配效果。下表列出了三种在布局前仿真和布局后仿真中评估阻抗匹配的方法。

我们可通过上文所述的多种方式评估阻抗失配情况,并确定其对信号完整性的影响。从最终布局中提取出阻抗失配,就能确定该如何调整互连和电路以确保信号完整性。可能需要修改的项目包括:添加终端器件、精心设计阻抗匹配网络,或重新布线以调整走线阻抗。

如需评估信号完整性和阻抗匹配,集成 3D 电磁场求解器和全套 CAD 工具的 PCB 设计与分析软件将助您一臂之力。Cadence Sigrity X 是 Cadence 最新一代信号和电源完整性(SI/PI)解决方案。搭载了全新的用于系统级分析的强大仿真引擎,并采用旗舰 Cadence Clarity 3D Solver 场求解器创新的大规模分布式架构用于超大规模、5G 通信、汽车等应用——

将系统分析性能提升 10 倍且无损精准度

突破性的大规模分布式仿真实现云端大规模复杂分析

紧密集成、业界领先的 SI/PI 技术在 Cadence 全设计平台可用

带来新的用户体验,用户可以在不同分析工作流程间复用,缩短复杂的系统分析设置时间

-

pcb

+关注

关注

4377文章

23596浏览量

413915 -

阻抗匹配

+关注

关注

14文章

360浏览量

31600 -

信号完整性

+关注

关注

68文章

1460浏览量

97153

发布评论请先 登录

技术资讯 I 信号完整性与阻抗匹配的关系

技术资讯 I 信号完整性与阻抗匹配的关系

评论