请教关于LVDS阻抗匹配的问题 LVDS输出阻抗偏大会出现什么情况?

LVDS(Low Voltage Differential Signaling)是差分信号传输技术,能够提供较高的数据传输速率和较低的电磁干扰。LVDS信号在传输时,需要确保信号通过的阻抗匹配,以确保信号的完整性和稳定性。阻抗不匹配会导致信号反射、丢失和功耗增加等问题,影响信号传输的完整性和可靠性。

LVDS输出阻抗偏大过高,会出现以下几种情况:

1.信号反射

当LVDS信号通过传输线时,如果阻抗不匹配,很容易出现信号反射的情况。当信号反射回LVDS输出端口时,会产生回波和噪声,影响信号传输的完整性和可靠性。对于高速传输的LVDS信号,信号反射会更加明显,因此需要更加严格的阻抗匹配。

2.功耗增加

当LVDS输出端口阻抗偏大时,输出驱动器需要产生更高的电压来驱动传输线,以保证信号完整性。这会导致输出驱动器消耗更多的功率,从而使得整个系统的功耗增加。这对于一些功耗敏感的应用来说是不可接受的。

3.信号丢失

当LVDS输出端口阻抗偏大时,传输线上的信号会受到更强的信号衰减。如果衰减达到一定程度,接收端可能无法正确接收信号,导致信号丢失。这种情况下,需要降低LVDS输出端口的阻抗以提高信号完整性和可靠性。

综上所述,LVDS输出阻抗偏大会导致信号反射、功耗增加和信号丢失等问题,影响传输线的完整性和可靠性。为避免这些问题的出现,需要进行严格的阻抗匹配,并在设计过程中注意输出端口阻抗的控制。

-

lvds

+关注

关注

2文章

1129浏览量

67662 -

电磁干扰

+关注

关注

36文章

2395浏览量

106806 -

输出阻抗

+关注

关注

1文章

104浏览量

12562

发布评论请先 登录

村田贴片电容的阻抗匹配问题如何解决?

如何确保模拟示波器的输入阻抗匹配?

阻抗匹配中所说的50R,90R之类的阻抗是什么意思?

LVDS连接器PCB设计与制造

请问SN74CBT3251的输出阻抗是多少?ADC10321的输入阻抗是多少?

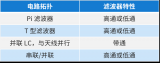

利用两个元件实现 L 型网络阻抗匹配

阻抗对音频设备的影响 静态阻抗和动态阻抗的区别

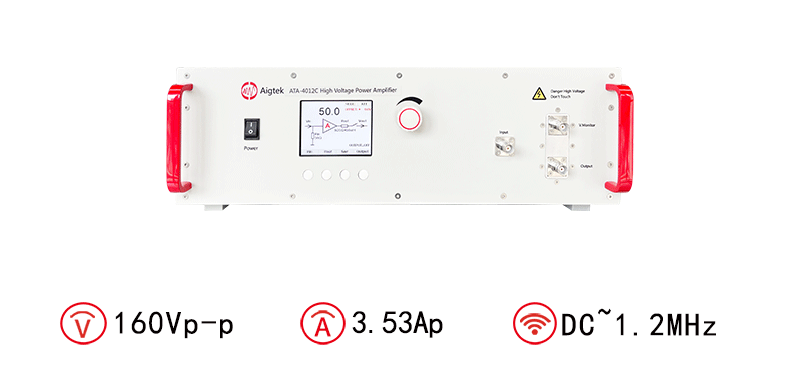

安泰: 功率放大器的输出阻抗是什么意思

请教关于LVDS阻抗匹配的问题 LVDS输出阻抗偏大会出现什么情况?

请教关于LVDS阻抗匹配的问题 LVDS输出阻抗偏大会出现什么情况?

评论