文章来源:学习那些事

原文作者:前路漫漫

本文主要讲述塑封工艺。

概述

塑封是微电子封装中的核心环节,主要作用是保护封装内部的焊线、芯片、布线及其他组件免受外界热量、水分、湿气和机械冲击的损害,同时增强封装的机械强度,便于后续贴片操作。按封装材料划分,电子封装可分为金属封装、陶瓷封装和塑料封装三类。其中,塑料封装因工艺简便、成本低廉,占据了90%以上的市场份额,且这一占比仍在持续上升。在集成电路塑料封装中,环氧模塑料是最常用的材料,在塑封材料中的占比超95%。

塑料按特性可分为热塑性与热固性两类。热塑性塑料的树脂分子呈线性或支链状结构,受热时会软化熔融,可塑造成特定形状,冷却后保持形态,再次加热仍能软化熔融,可重复加工,成型过程通常仅涉及物理变化。

热固性塑料则是通过加热实现固化的聚合物材料,成型时同时伴随物理与化学变化。这类材料在较低温度下会熔融,具备良好流动性;注入模具后,在模具的温度和压力作用下发生化学交联反应,长链分子转化为密集的网状交联结构,最终固化成型。冷却后,即便再次加热也不会软化,温度过高时会出现碳化分解。

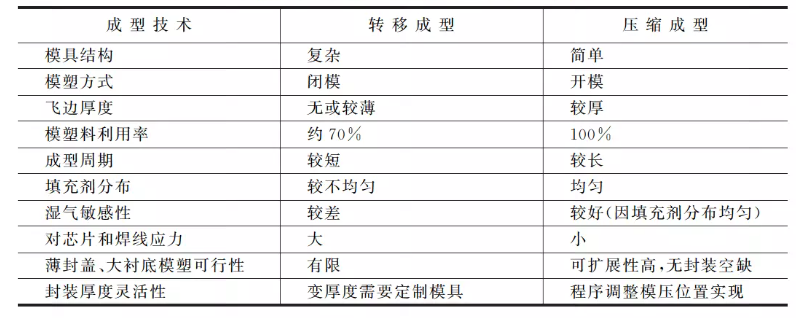

塑料成型技术多样,包括转移成型(又称压注成型、传递模塑)、压缩成型(又称模压成型)和注塑成型等,其中转移成型与压缩成型在微电子封装中应用最为广泛。

注塑成型是常见的塑料成型工艺,具有劳动强度小、成型周期短、产品质量佳、模具使用寿命长、操作安全等优势。但在微电子封装领域,由于引线框架在注塑模具中不易固定,且环氧模塑料采用该工艺难度较高,目前尚未投入实际应用。

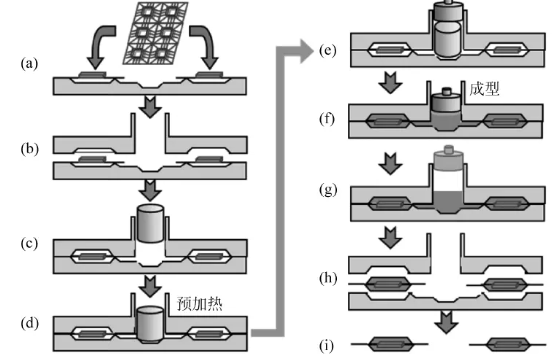

转移成型技术整合了注塑成型与压缩成型的优点,设有独立的加料室。模塑料在加料室内受热熔化后,在低压作用下通过浇注系统快速注入已加热的闭合模具型腔,随后在型腔内经保温保压完成固化。其工艺流程如下:①将引线框架定位放入下模具;②合上上模具;③加入环氧模塑料(这类材料通常储存在冷库,使用前需在室温下回温);④进行预加热;⑤通过活塞加压,将模塑料压入型腔;⑥保温保压,完成固化成型;⑦活塞撤离;⑧打开上模具;⑨取出成型样品。

转移成型具有压注时间短、成型快速、生产效率高的特点,适合加工薄壁、壁厚不均、含细薄金属嵌件、带深孔及形状复杂的塑件,尤其适用于电子元器件的塑封。经其塑封的元器件精度高、尺寸稳定,无气孔和缩孔,且电性能、耐湿性良好,是微电子封装中应用最广的成型技术。不过,该技术也存在不足:一是模塑料利用率仅约70%;二是填充料分布不够均匀;三是树脂流动可能对芯片和焊线产生应力;四是在薄包封上盖及大面积衬底封装时,可能出现封装不充分的问题。

与转移成型不同,压缩成型的加料室与型腔是一体的。模塑料直接放入已加热至成型温度的敞开型腔中,塑化与固化过程均在型腔内完成。但塑料粉末可能干扰合模定位销及用于孔成型的金属嵌件位置,导致塑件精度不足,影响产品质量,且成型效率较低,因此早期塑封多采用转移成型工艺。

随着封装厚度逐渐变薄,以及大尺寸衬底封装、大面积扇出式晶圆级封装等新工艺的发展,转移成型的缺陷愈发明显,已难以满足需求。而压缩成型能很好地解决这些问题,在薄型封装、低翘曲封装、大尺寸衬底封装及大面积扇出式晶圆级封装中得到了有效应用。关于转移成型与压缩成型在微电子封装中的差异,可参考相关对比表。

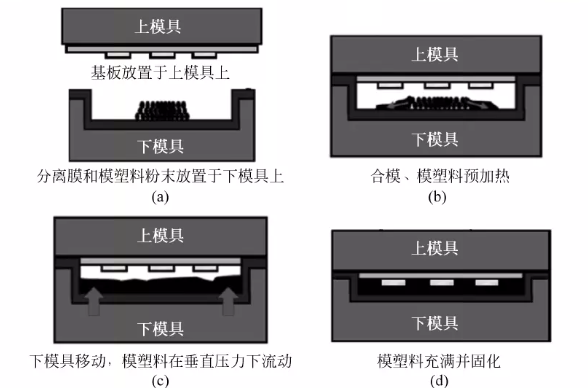

压缩成型的工艺流程如下:①打开上下模具,将基板定位在上模具,通过真空吸附将分离膜贴合到下模具表面,并在膜上放置模塑料粉末;②合上上下模具,对模塑料进行预加热;③下模具活动部分上移,模塑料在垂直压力作用下流动;④模塑料填满型腔,并在温度与压力作用下固化。

塑封后续步骤

塑封工序完成后,还需进行后续的固化处理。具体操作是将塑封后的样品放入烤箱,在170-180℃的温度下烘烤8小时,以此确保环氧模塑料充分固化,同时消除塑封过程中产生的内应力。

经过模塑处理后,封装表面会残留溢出的模塑料,且烘烤后的引线框架表面可能出现氧化层,这些都需要清除干净,以便后续的电镀工序顺利进行。传统的去溢料方法包括机械喷砂(分干法和湿法)、碱性电解法以及化学浸泡结合高压水喷射法。随着激光加工技术在微电子封装领域的应用推广,全自动激光去溢料技术逐渐发展起来,该技术具有清理彻底、效率大幅提升的优势。

为提升引线框架引脚的可焊性与导电性,同时抵御潮湿、高温等外界不利环境的影响,塑封完成后的引线框架需通过电镀或浸锡工艺,在引脚上覆盖一层薄薄的保护性金属层,目前以电镀工艺为主。电镀主要有含铅和无铅两种类型,早期多采用含铅电镀,出于环保要求,现在主流为无铅电镀,即使用高纯度锡镀层或锡银镀层。电镀过程在流水线式的电镀槽中进行:先在专门的上料台放置引线框架,随后框架被传送至装有电镀液的电镀槽,作为阴极浸入其中,金属离子在获得电子后沉积到引脚上完成电镀,最后送至下料台取出。

电镀完成后,还需进行退火处理,通常是在145-155℃的温度下保持2小时。这一步的作用是让无铅镀层在高温烘烤后,通过内部结构的调整来抑制镀层中晶须的生长。晶须是指在长期潮湿或温度变化的环境中,从材料表面生长出的须状晶体,可能导致产品引脚短路,而无铅镀层中较易出现晶须,存在短路风险。

要理解锡须,先明确晶须的定义:晶须是一种发丝状晶体,能从固体表面自然生长,又称“固有晶须”。多种金属表面会生长晶须,常见的有锡、镉、锌、锑、铟等,锡铅合金上也可能出现,但概率较低;而铅、铁、银、金、镍等金属表面则很少出现。一般来说,晶须现象更易发生在质地较软、延展性好的材料上,尤其是低熔点金属。

锡的晶须简称锡须,呈单晶体结构,具有导电性。其形状多为直状、扭曲沟状或交叉状,有时为中空结构,外表面带有沟槽。锡须直径可达10微米,长度甚至能超过9毫米,可承载10毫安的电流,电流过大时通常会被烧断。

锡须的生长速率通常在每年0.03-0.9毫米之间,在特定条件下可能加快100倍以上。其生长速率受多种复杂因素影响,包括镀层的电镀化学过程、镀层厚度、基体材料、晶粒结构以及储存环境等。锡须多从电镀层开始生长,且存在较长的潜伏期,从几天到数月甚至数年不等,因此其可能带来的危害难以准确预测。

一般而言,锡须产生的原因主要有两点:一是锡与铜之间发生相互扩散,形成金属化合物,导致锡层内压应力急剧增加,促使锡原子沿晶体边界扩散,进而形成锡须;二是电镀后镀层存在残余应力,引发锡须生长。

抑制锡须生长的方法主要有以下几种:一是采用电镀雾锡,通过改变晶体结构来减小应力;二是在150℃下烘烤2小时进行退火处理(实验表明,温度高于90℃时,锡须会停止生长);三是在Enthone FST浸锡工艺中添加少量有机金属添加剂,以限制锡铜金属互化物的生成;四是在锡与铜之间添加一层阻挡层,如镍层;五是在锡中添加铅曾是抑制锡须的有效方法,但因铅不环保,需从其他角度寻找解决方案;六是添加1%-2%的黄金,也能有效抑制锡须生长。

切筋成型包含切筋与成型两道工序。其中,切筋是将整片引线框架分割为独立单元的过程;成型则是对已分割的单元进行引脚加工,使其形成工艺所需的形状,之后放入料管或料盘中。简单来说,切筋成型工艺就是先把原本的大块引线框架切割成若干小分块,再对这些小分块进行处理,让引脚达到规定形态。这两道工序有时会同步完成,有时也会分开进行。部分企业会先进行切筋,接着完成上锡,再开展成型工艺,通过这种方式减少引脚截面未镀上焊锡的面积。

作为电子封装产业的分支技术,IC切筋成型技术在产业近年来的快速扩张推动下实现了迅猛发展。随着封装形式从DIP、SOP、QFP逐步向CSP等演进,其与电路板的连接方式、引脚数量都发生了显著变化,这对切筋成型的工艺标准提出了越来越高的要求。

激光打码是利用激光束在封装的正面或背面标注标识,这些标识包含国家、制造商、器件代码、生产批次等信息,便于产品的使用与追溯。

完成打码后,需对成品电路的外观进行检查,合格产品将按照包装规范进行包装,包装方式包括料管、料盘、卷带盘等。

-

芯片

+关注

关注

460文章

52749浏览量

444448 -

封装

+关注

关注

128文章

8852浏览量

145965 -

工艺

+关注

关注

4文章

693浏览量

29601

原文标题:塑封工艺详述

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

芯片塑封工艺过程解析

详解PCB线路板多种不同工艺流程

PCB蚀刻工艺原理_pcb蚀刻工艺流程详解

芯片制造工艺流程步骤

芯片制造工艺流程步骤是什么

集成电路基本的工艺流程步骤

SMT工艺流程详解

塑封、切筋打弯及封装散热工艺设计

详解塑封工艺的流程步骤

详解塑封工艺的流程步骤

评论