01智多晶SerDes IP已经升级到2.0版本

为了满足用户对SerDes日益增涨和多样化的要求。智多晶SerDes IP推出了2.0版本的升级,本次升级相比1.0版本主要带来了以下的变化:

增加了对SerDes内部的不同通道单独进行速率配置的功能

增加了同一路通道内部的TX和RX进行独立参数的配置的功能

增加了对每个单独通道的时钟来源(QPLL/CPLL)选择的功能

增加了从其他quad来的参考时钟来源的选择(North/South Route)功能

增加了选择输出时钟路径:PMA内部时钟或直接输出参考时钟

增加了RX/TX方向64B/66B 相关的功能

增加了Bypass SerDes内部FIFO的功能(使用延迟线代替)

增加了Channel Bonding(多通道绑定同步传输)的功能

02智多晶Serdes IP 2.0界面介绍

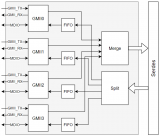

图1 SerDes IP 多通道单独页面配置

智多晶SerDes IP采用了灵活的配置界面可以对每个SerDes通道(channel)进行灵活的配置。如图1所示,用户可以定制对每个channel的速率,参考时钟频率,CPLL/QPLL的选择进行独立的配置,用以满足各种自定义项目中的需求。

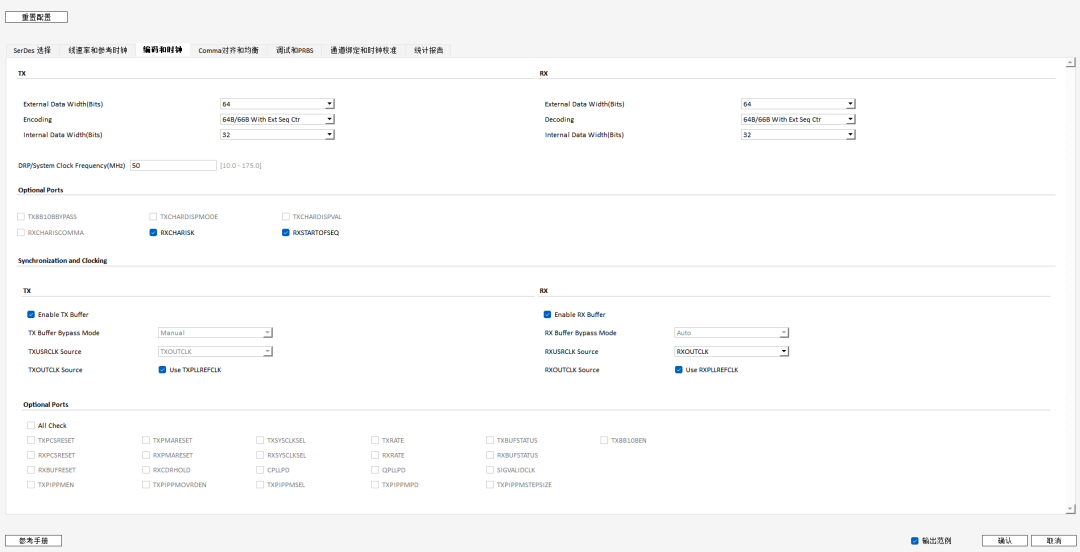

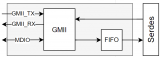

图2 编码选择和时钟输出选择

目前SerDes 2.0已经支持了对8B/10B编码和64B/66B编码(Gearbox层以下)的配置选项。用户可以使用智多晶SerDes硬核的编码器完成8B/10B和64B/66B(Gearbox层以下)的对应功能 。IP界面也提供了对外部位宽和内部位宽的定制化配置。用户可以根据自己的系统和对应的上层协议来灵活的选取数据位宽。

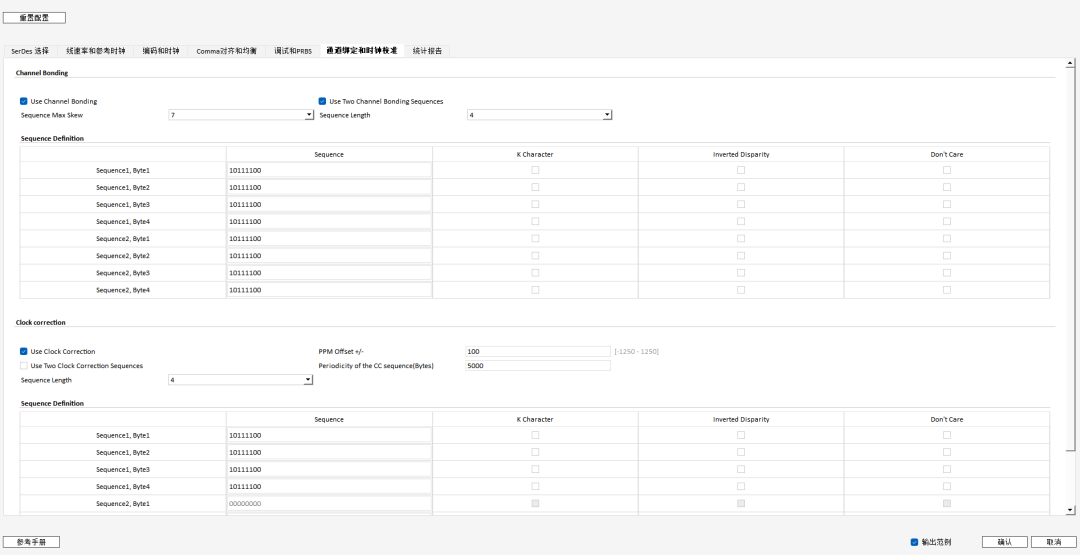

图3 通道绑定和时钟校准功能

目前SerDes 2.0已经支持了对通道绑定和时钟校准的功能。用户可以通过界面上的提示来完成相对应的配置。以通道绑定为例,可以设置具体的通道绑定所需要的码形长度和具体数值等。

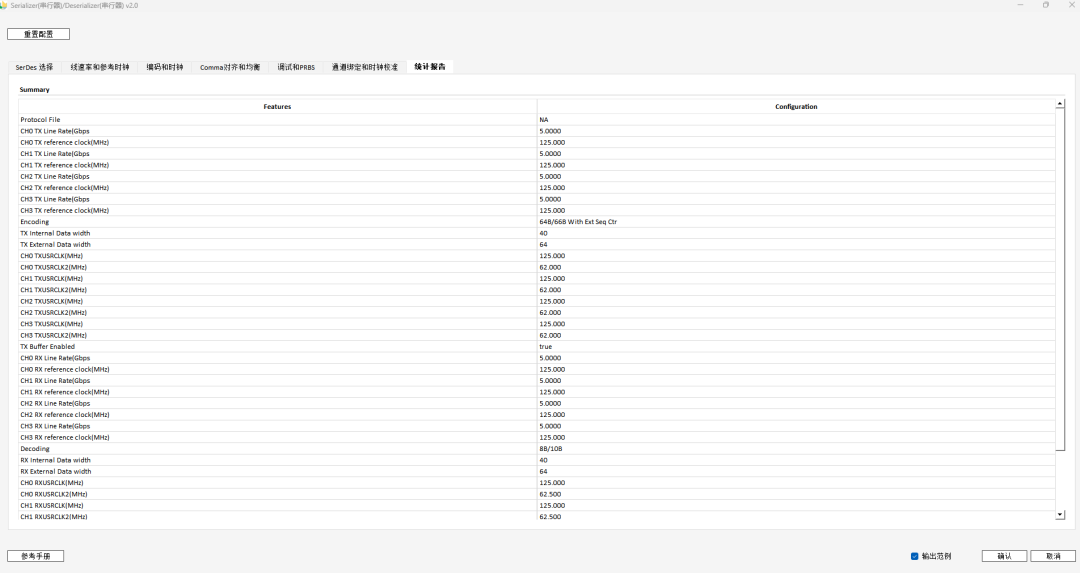

图4 统计报告列表

在配置完成之后,SerDes 2.0 IP会生成对应的统计报告列表,用户可以通过浏览生成的统计报告列表来验证自己的IP是否满足自己的配置要求。同时提供了输出范例工程,供用户作为参考使用。

03智多晶SerDes IP 2.0的常用场景

SerDes(Serializer/Deserializer)是一种高速串行通信技术,主要用于将多路低速并行信号转换为高速串行信号,并通过传输媒体(如光缆或铜线)传输,然后在接收端再将串行信号转换回并行信号随着高速集成电路的发展,对高带宽,低延迟的协议需求越来越大。目前多种高速协议都可以以Serdes 为基础进行进一步的开发,用以完成高速通讯的目的。

目前常见的使用主要包括:

万兆以太网

CPRI

JESD204B

QSGMII

SRIO

XAUI

PCIE

AURORA

DP/eDP

VByOne

目前智多晶Seal 5000系列产品SerDes的性能处于业界领先水平,SDM最大支持0.5-10.3125Gbps线速率,SDP最大支持0.5-6.6Gbps的线速率。SerDes最大速率受到PCB信号完整性设计,外界干扰等多种条件影响。如果要达到理论性能需要有相关设计保障,详细信息请咨询智多晶FAE。

-

IP

+关注

关注

5文章

1825浏览量

153189 -

时钟

+关注

关注

11文章

1909浏览量

133477 -

SerDes

+关注

关注

7文章

222浏览量

35953

原文标题:“芯”技术分享 | 智多晶SerDes 2.0 IP介绍

文章出处:【微信号:智多晶,微信公众号:智多晶】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

智多晶Serdes IP的应用领域及工作原理

智多晶FIFO_Generator IP介绍

智多晶eSPI_Slave IP介绍

国产智多晶FPGA介绍及应用

HDMI_1.4_2.0_RX_Subsystem_IP介绍和基础debug建议

IP_数据表(I-5):SerDes PHY for TSMC 28nm HPC+

为什么我们需要SERDES?SERDES的优点有哪些?

智多晶LPC_Controller IP介绍

智原科技推出最新SerDes IP持续布局联电22纳米IP解决方案

智原推出最新SerDes IP持续布局联电22纳米IP解决方案

智多晶QSGMII IP介绍

智多晶SGMII IP介绍

智多晶SerDes 2.0 IP介绍

智多晶SerDes 2.0 IP介绍

评论