你是否经常在Layout设计中抓瞎,拿着板子无从下手,拿着鼠标深夜狂按;DDR等长没做好导致系统不稳定,PCIe没设相位容差造成链路训练失败……这些都是血泪教训,关键时刻需要靠约束管理器救命!Allegro约束管理器搞差分对,简直是把高速设计的「地狱模式」切换成「新手村」!

上期我们介绍了盲/埋孔的使用,本期我们将教会大家如何使用Cadence的约束管理器,用最少的时间一键速通Layout。

应用场景

一键进行差分对创建,30s即可完成几百对差分信号的绑定,软件自动抓取网络名称配对,告别抓瞎式查找,用最短的时间教会菜鸟不翻车。

解决光模块差分对长度差而导致的光电转换时序错乱,实现真正的自动避坑,简直是硬件狗们的「外挂级防秃神器」!

防手残党翻车,规则自动化锁死作死操作,走线稳如老狗;用好约束管理器,早下班不熬夜,枸杞保温杯里泡的都能少放两粒!

运行环境

1、操作系统:Win 11

2、Cadence软件配置:Allegro X Designer Plus 24.1-2024 P001 [9/4/2024] Windows SPB 64-bit EditionEdition

设置默认物理规则约束

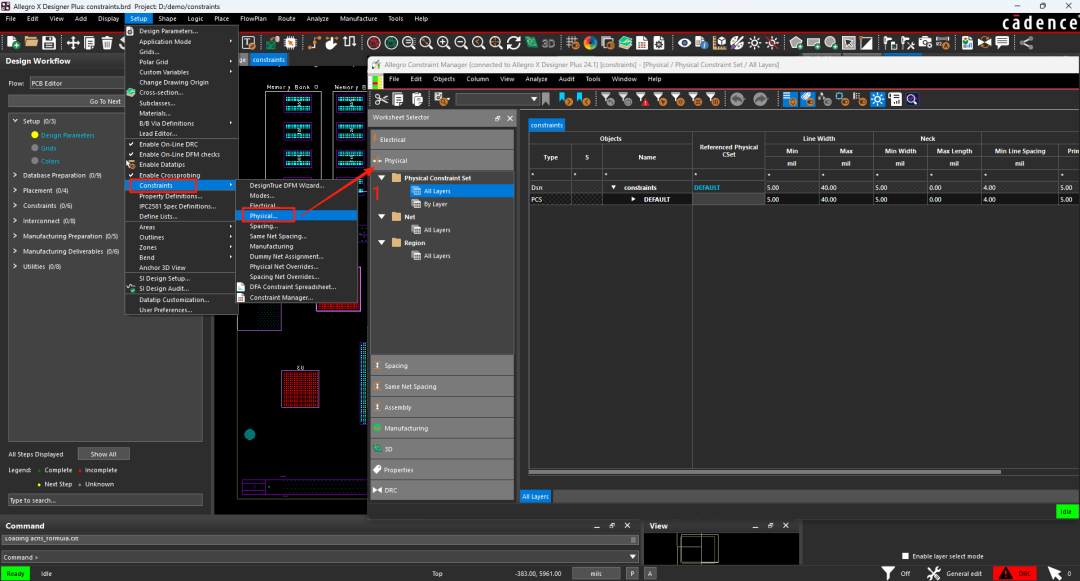

1.打开规则约束管理器,点击菜单Setup-Constraints-Physical,打开物理约束。

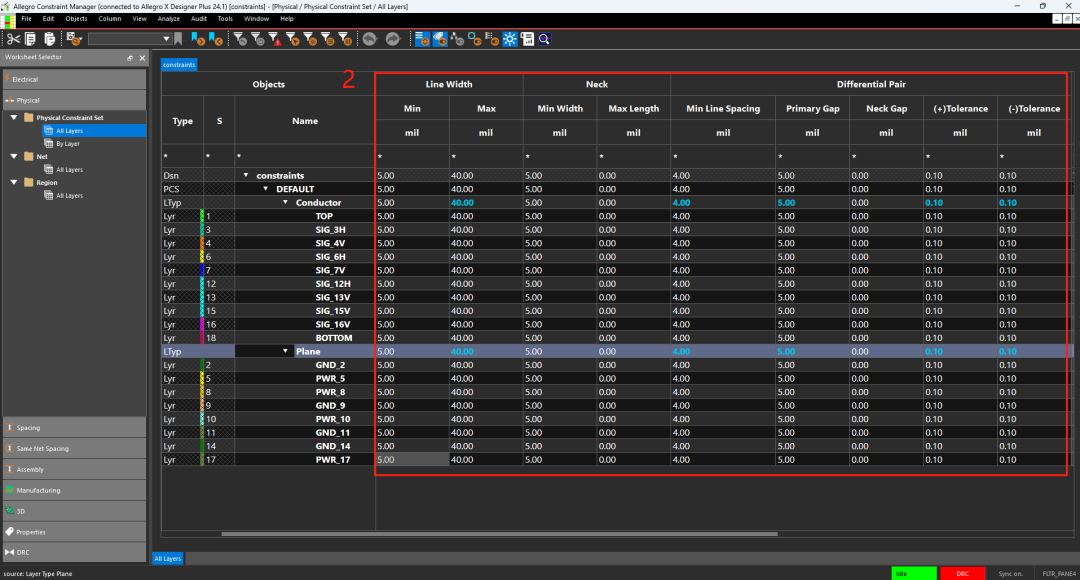

2.选择Physical Constraint Set> All Layers,设置一个默认的物理约束:最小线宽(Min Line Width)5mil、最大线宽(Max Line Width)40mil、劲缩模式最小线宽(Min Neck Width)5mil、颈缩模式最大允许长度(Max Neck Length)0mil、差分对最小线边间距(DP Min Line Spacing)4mil、差分对基准线间距(DP Primary Gap)5mil、颈缩模式差分队间距(DP Neck Gap)0mil、差分对正极性走线动态阻抗容限(DP (+) Tolerance)0.1mil、差分对负极性走线动态阻抗容限(DP (-) Tolerance)0.1mil

在约束管理器中创建差分对

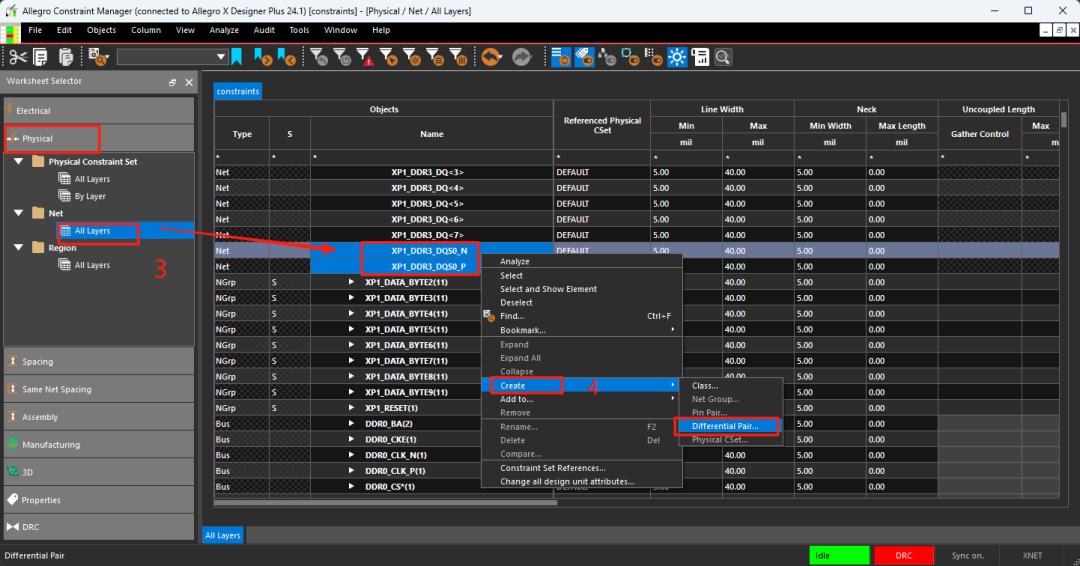

3.创建一对新的差分对,在Physical下找到Net点击All Layers,找到需要定义的差分对名称。

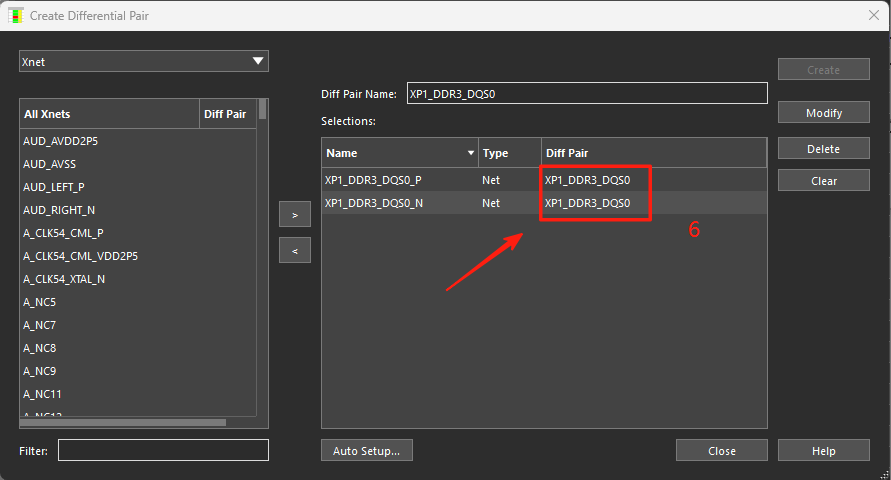

4.将这一对差分对选中XP1_DDR3_DQS0_N与XP1_DDR3_DQS0_P,鼠标右键点击Create-Differential Pair,打开创建差分对表单。

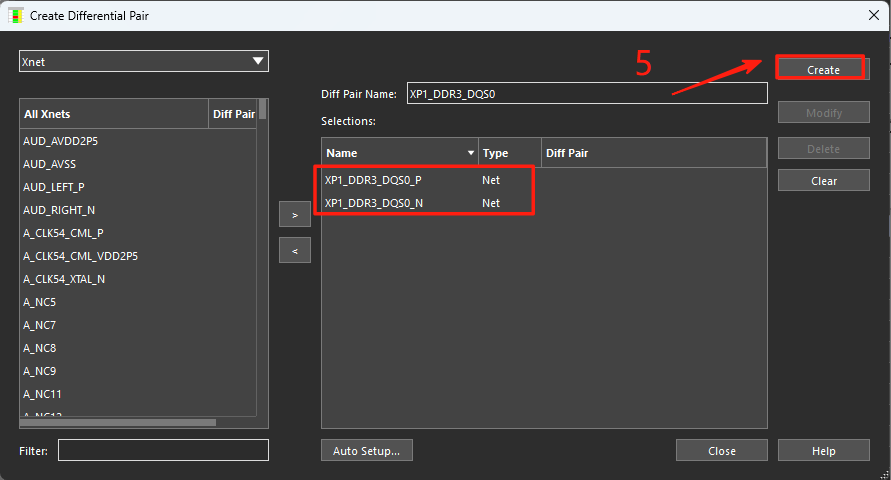

5.点击Create创建差分对,可以看到选中的差分对网络名称已经出现在界面上。

6.在Selections界面框可以看到差分对创建成功。

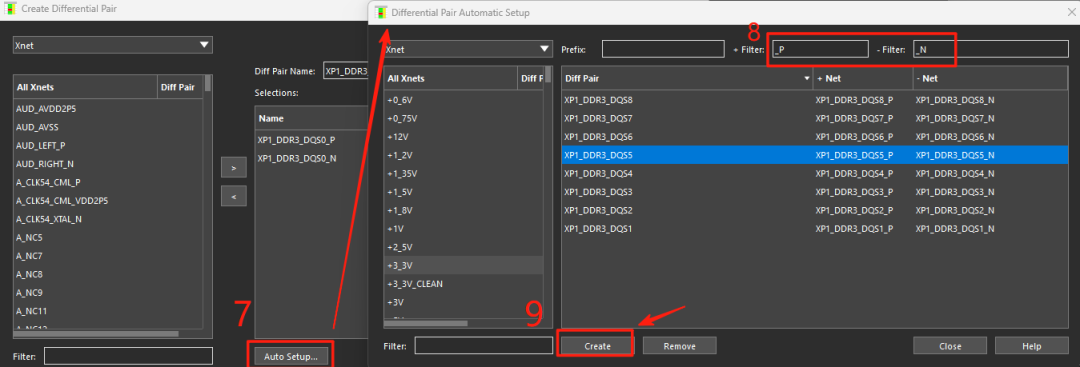

7.根据命名规则一键自动创建多对差分对网络:在刚刚创建成功差分对界面Create Differential Pair下方点击Auto Setup,打开Differential Automatic Setup自动创建差分对。

8.根据差分对网络的命名去搜索差分对网络,在+Filter输入_P,在-Filter输入_N,可以查找到按照这种方式命名的差分对,可以一键进行差分对创建。

9.点击Create进行创建。

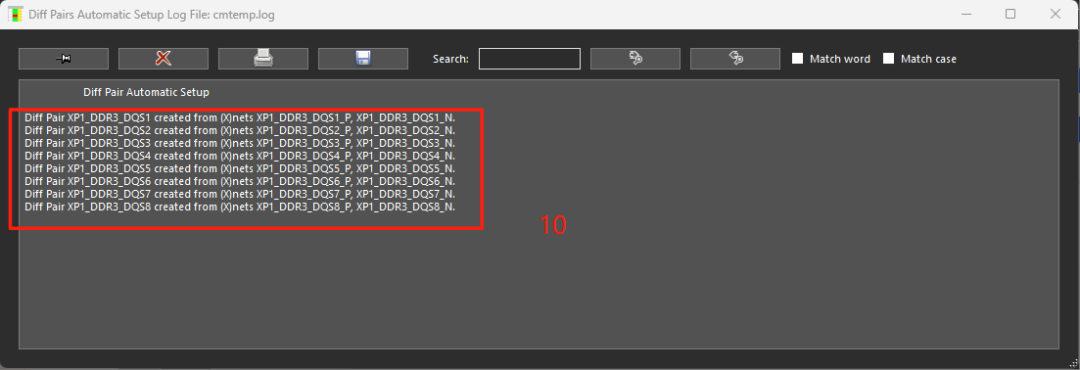

10.查看差分对创建成功日志。

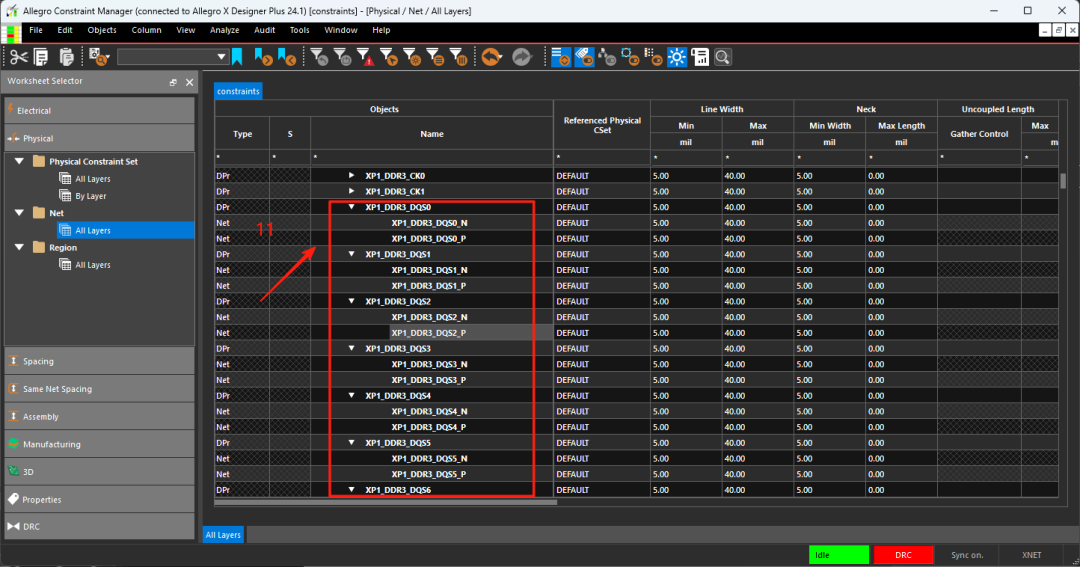

11.在规则约束管理器中的物理规则约束网络中可以看到刚刚创建的8对差分对。

在不同层为差分对创建物理规则约束

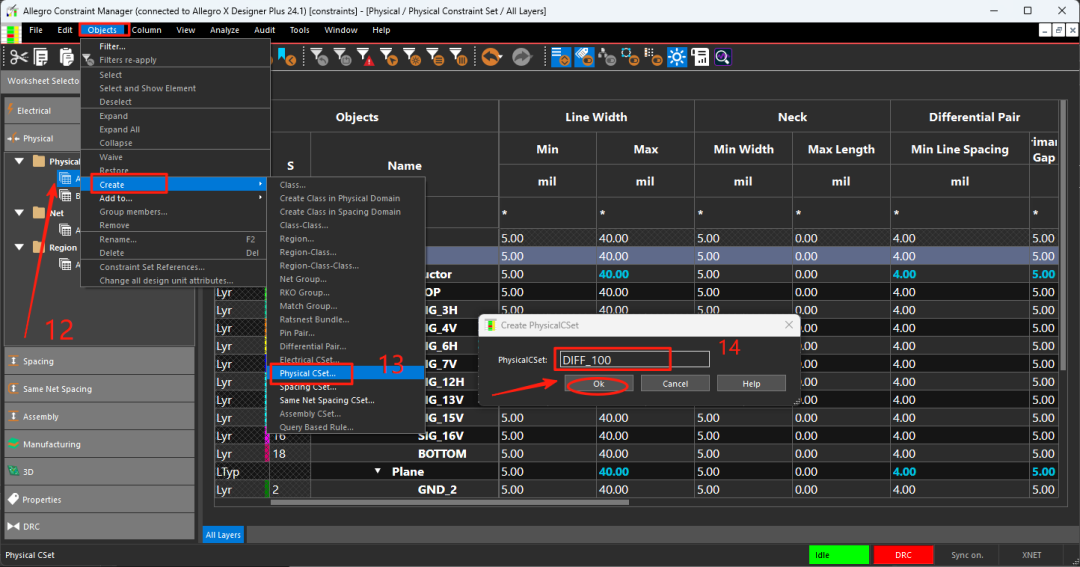

12.在规则约束管理器的Physical下,展开Physical Constraint Set规则设置,点击All Layers。

13.点击菜单栏上的Objects-Create-Physical CSet...

14.创建差分对规则约束名称PhysicalCSet:DIFF_100,点击OK。

将创建的规则分配到差分对网络中

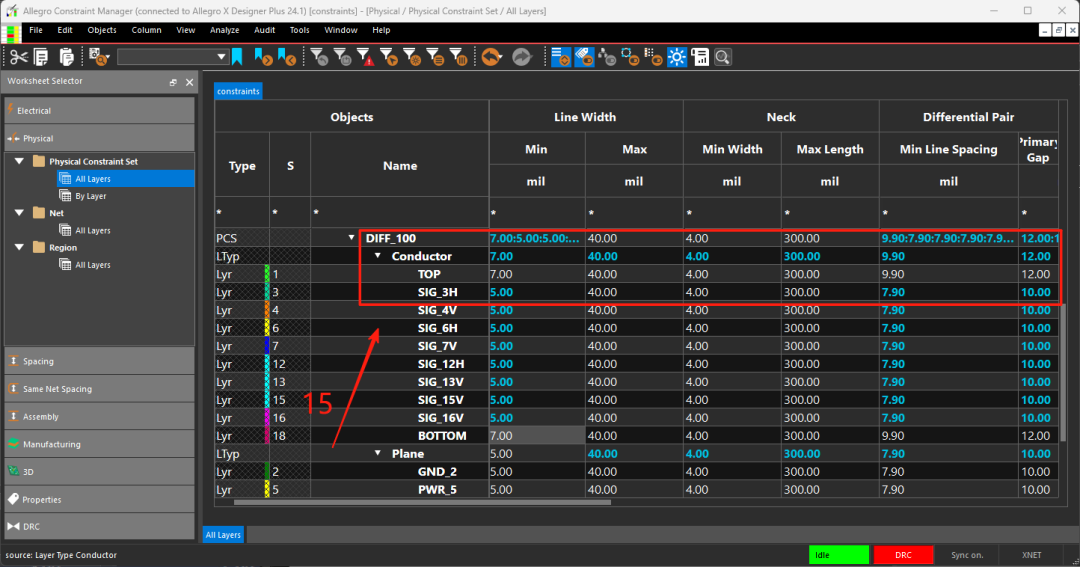

15.根据设计要求更改差分对的规则约束值,对于PCB的顶层与底层的差分对的规则与内层不同。

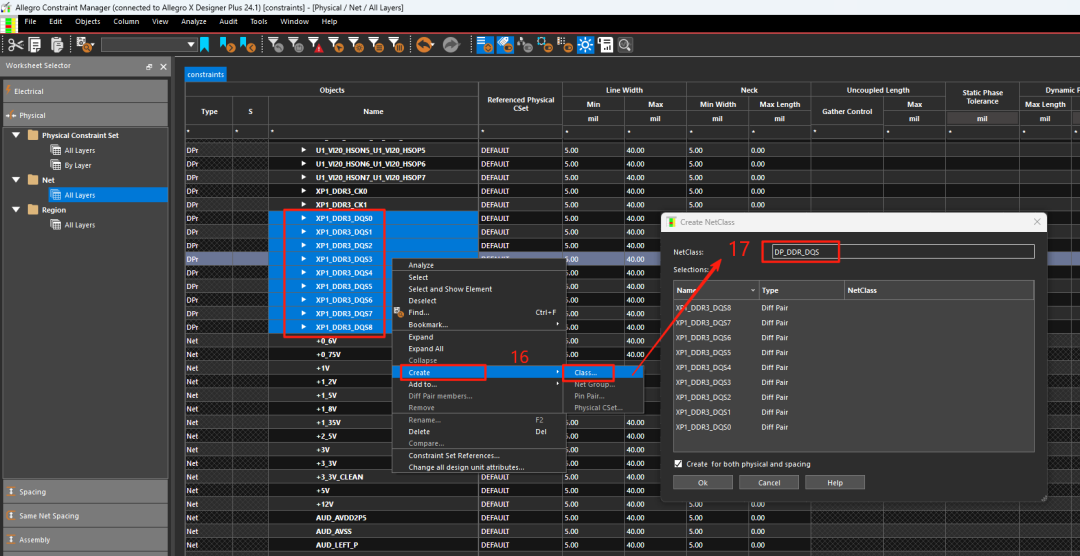

16.为这些差分对创建一个分类,Ctrl选中需要创建类的差分对,鼠标右键点击Create-Class。

17.在Create NetClass界面的NetClass中输入名称,点击OK。

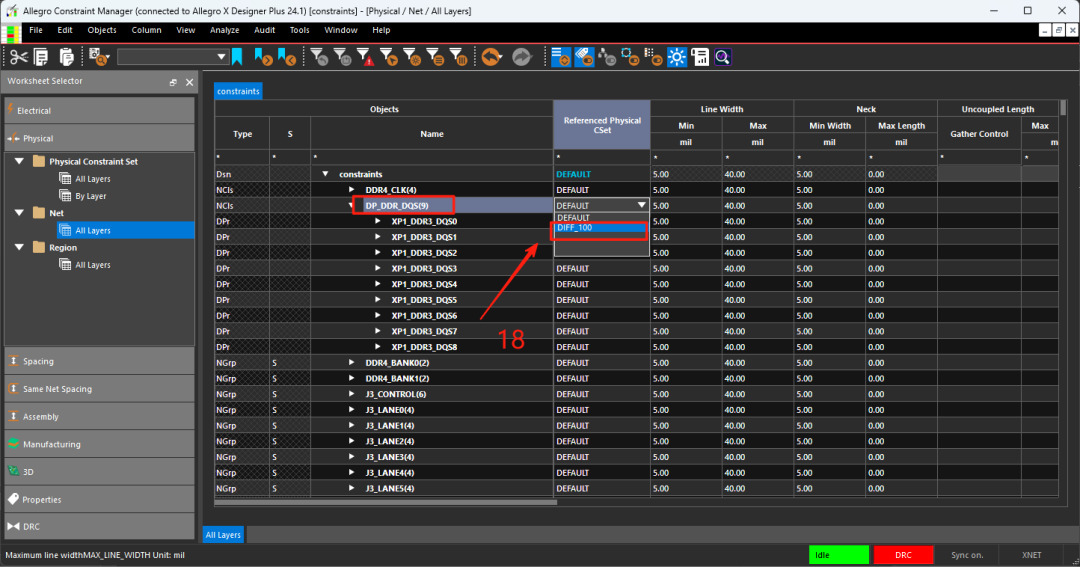

18.在刚刚创建的差分对类的Referenced Physical CSet修改为差分对规则约束:DIFF_100。

总结栏

本期主要介绍了在PCB设计中创建差分对规则约束,让每一位设计师手握开挂神器,一次投板成功。下一期我们将为大家PCB设计中布线的孔的放置技巧。

-

差分

+关注

关注

0文章

63浏览量

21661 -

管理器

+关注

关注

0文章

255浏览量

19160 -

Layout设计

+关注

关注

1文章

15浏览量

1720

发布评论请先 登录

关于差分对之间绕等长的疑问

EDA工具手册Cadence教程之约束管理器的详细使用教程免费下载

技术资讯 I 图文详解约束管理器-差分对规则约束

技术资讯 I 图文详解约束管理器-差分对规则约束

评论