Mentor, a Siemens business 宣布,该公司 Calibre? nmPlatform 和 Analog FastSPICE (AFS?) Platform 中的多项工具已通过TSMC最新版5nm FinFET 和 7nm FinFET Plus 工艺的认证。Mentor 同时宣布,已更新了 Calibre nmPlatform 工具,可支持TSMC的晶圆堆叠封装 (WoW)技术。Mentor 的工具和 TSMC 的新工艺将协助双方共同客户更快地为高增长市场提供芯片创新。

TSMC 设计基础架构营销部资深总监 Suk Lee 表示:“Mentor 通过提供更多功能和解决方案来支持我们最先进的工艺,持续为TSMC 生态系统带来了更高的价值。通过为我们的新工艺提供不断创新的先进电子设计自动化 (EDA) 技术,Mentor 再次证明了对 TSMC 以及我们的共同客户的承诺。”

Mentor 增强工具功能,以支持 TSMC 5nm FinFET 和 7nm FinFET Plus 工艺

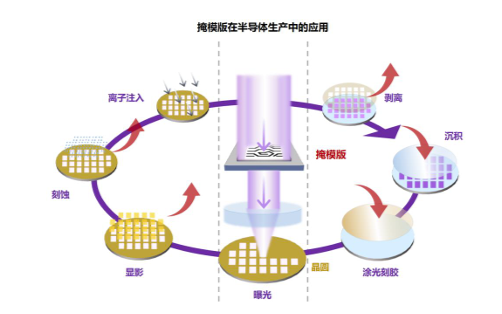

Mentor 与 TSMC 密切合作,针对 TSMC 的 5nm FinFET 和 7nm FinFET Plus 工艺,对 Mentor 的 Calibre nmPlatform 中的各种工具进行认证,其中包括 Calibre nmDRC?、Calibre nmLVS?、Calibre PERC?、Calibre YieldEnhancer 和 Calibre xACT?。这些 Calibre 解决方案现已新增测量与检查功能,包括但不限于支持与 TSMC 共同定义的极紫外 (EUV) 光刻技术要求。Mentor 的 Calibre nmPlatform 团队还与 TSMC 合作,通过增强多 CPU 运行的可扩展性,来改善物理验证运行时的性能,进而提高生产率。Mentor 的 AFS 平台,包括 AFS Mega 电路仿真器,现在也获得TSMC 的 5nm FinFET 和 7nm FinFET Plus 工艺的认证。

Mentor 增强工具功能,以支持 TSMC 的 WoW 晶圆堆叠技术

Mentor 在其 Calibre nmPlatform 工具中新增了几项增强功能,以支持 WoW 封装技术。增强功能包括适用于带背面硅通孔 (BTSV) 的裸片的 DRC 和 LVS Signoff、芯片到芯片的接口对齐与连通性检查以及芯片到封装堆叠的接口对齐与连通性检查。其他增强功能还包括背面布线层、硅通孔 (TSV) 中介层以及接口耦合的寄生参数提取。

Calibre Pattern Matching,可支持 TSMC 7nm SRAM 阵列检查实用工具

Mentor 与 TSMC 密切合作,将 Calibre Pattern Matching 与 TSMC 的 7nm SRAM 阵列检查实用工具进行整合。该流程有助于客户确保其构建的 SRAM 实现可满足工艺需要。借助这种自动化,客户即能成功流片。SRAM 阵列检查实用工具可供 TSMC 7nm工艺的客户使用。

Mentor, a Siemens business 副总裁兼Design to Silicon 部门总经理 Joe Sawicki 表示:“TSMC 持续不断地开发创新晶圆工艺,使我们的共同客户能够向市场推出许多世界上最先进的 IC,我们不仅为 Mentor 的平台能率先获得 TSMC 最新工艺的认证感到自豪,也为我们能与 TSMC 紧密合作,携手开发新技术以协助客户加速硅片生产的目标感到自豪。”

-

芯片

+关注

关注

460文章

52619浏览量

442738 -

sram

+关注

关注

6文章

787浏览量

116225

发布评论请先 登录

龙图光罩90nm掩模版量产,已启动28nm制程掩模版的规划

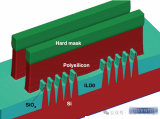

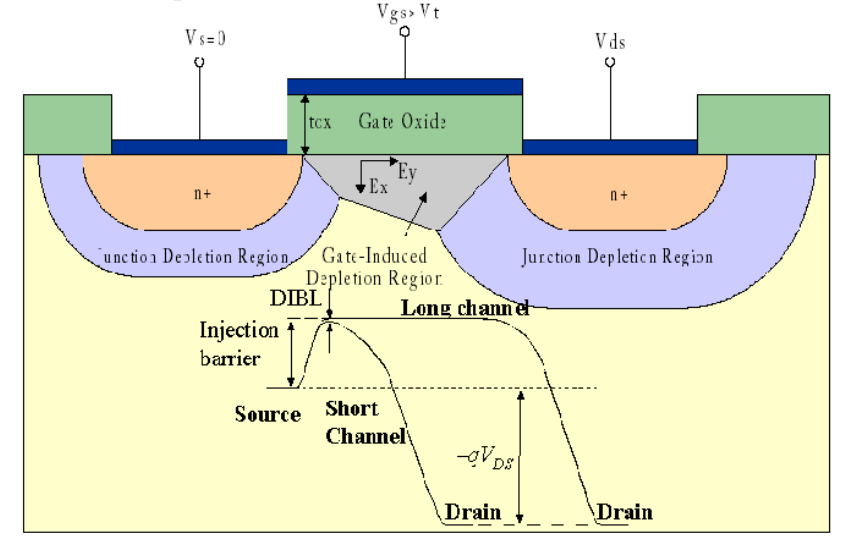

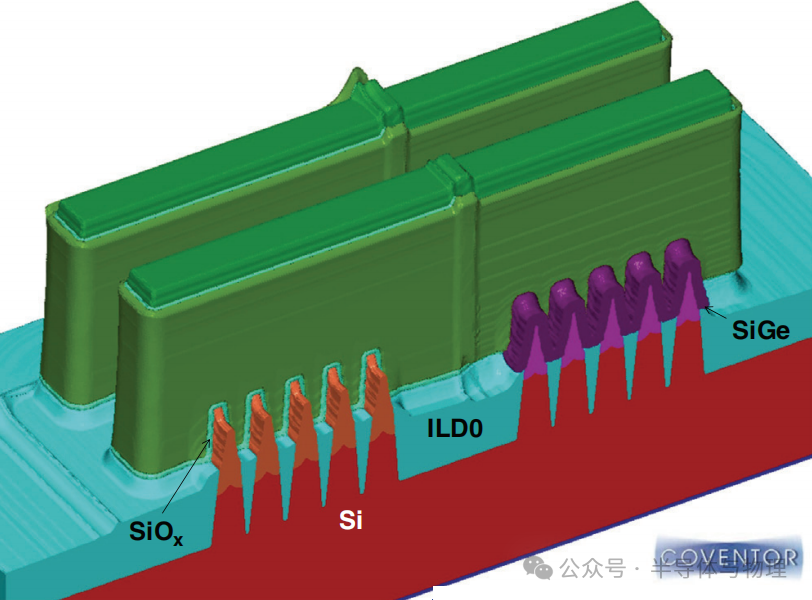

体硅FinFET和SOI FinFET的差异

Cadence UCIe IP在Samsung Foundry的5nm汽车工艺上实现流片成功

曝三星已量产第四代4nm芯片

FinFet Process Flow-源漏极是怎样形成的

FinFet Process Flow—哑栅极的形成

消息称台积电3nm、5nm和CoWoS工艺涨价,即日起效!

台积电产能爆棚:3nm与5nm工艺供不应求

AI芯片驱动台积电Q3财报亮眼!3nm和5nm营收飙涨,毛利率高达57.8%

所谓的7nm芯片上没有一个图形是7nm的

Platform 中的多项工具已通过TSMC最新版5nm FinFET 和 7nm FinFET Plus 工艺的认证

Platform 中的多项工具已通过TSMC最新版5nm FinFET 和 7nm FinFET Plus 工艺的认证

评论