最近网上因为光刻机的事情,网上又是一阵热闹。好多人又开始讨论起28nm/7nm的事情了有意无意之间,我也看了不少网上关于国产自主7nm工艺的文章。不过这些文章里更多是抒情和遐想,却很少有人针对技术本身做过深入解释和探讨当然,关于国产7nm工艺技术的具体来源细节,我其实了解也不多,也不方便公开讨论。但至少我觉得有必要写些文字给非半导体制造行业的人士讲解一下,一般意义上所谓的7nm工艺到底是怎么回事

首先简单明确一个事实:正如我文章标题所言,7nm工艺其实只是一个等效的说法,实际上7nm芯片上所有层的最小线宽都远远大于7nm

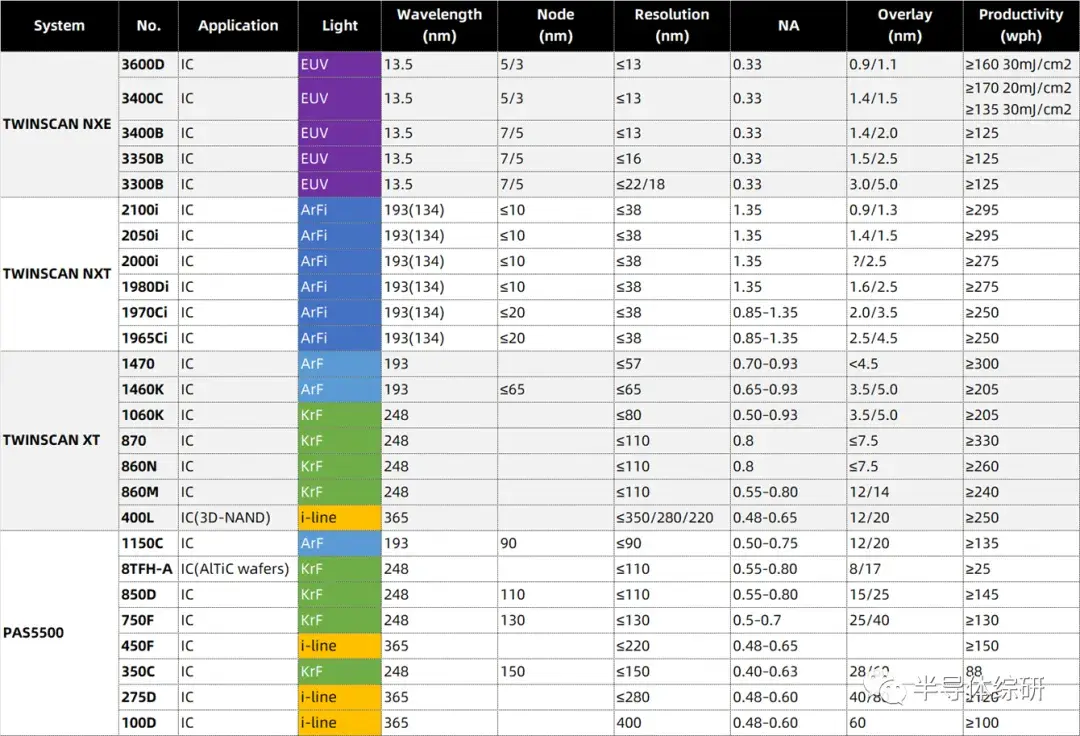

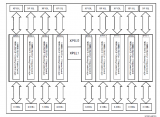

上图是我整理的ASML目前在售的各类光刻机的型号及技术指标清单。从表中可见,最先进的DUV光刻机 TWINSACAN NXT 2100i的最高分辨率只有38nm;而EUV光刻机 3600D的分辨率也只有13nm在晶圆厂的实际生产过程中,无论是用DUV加多重曝光或者是EUV(在7nm~5nm工艺中,EUV都只是单次曝光)都无法达到7nm的分辨率/CD值(半间距)

当初FinFET工艺被采用后,虽然实际上图形的线宽/分辨率并没有大幅度提高,但由于晶体管的结构发生重大变化以后,其整体尺寸是明显微缩了。这就使得我们能够在单位面积的晶圆上容纳更多数量的晶体管。从效果的角度上,开发者将其对比原有平面晶体管的密度来换算出一个名义上的等效线宽:也就是我们一般所谓的14nm、7nm...从20nm开始,所有晶体管都开始采用FinFET工艺后(3nm开始有了GAA等新技术),这个线宽就都完全是等效出来的了

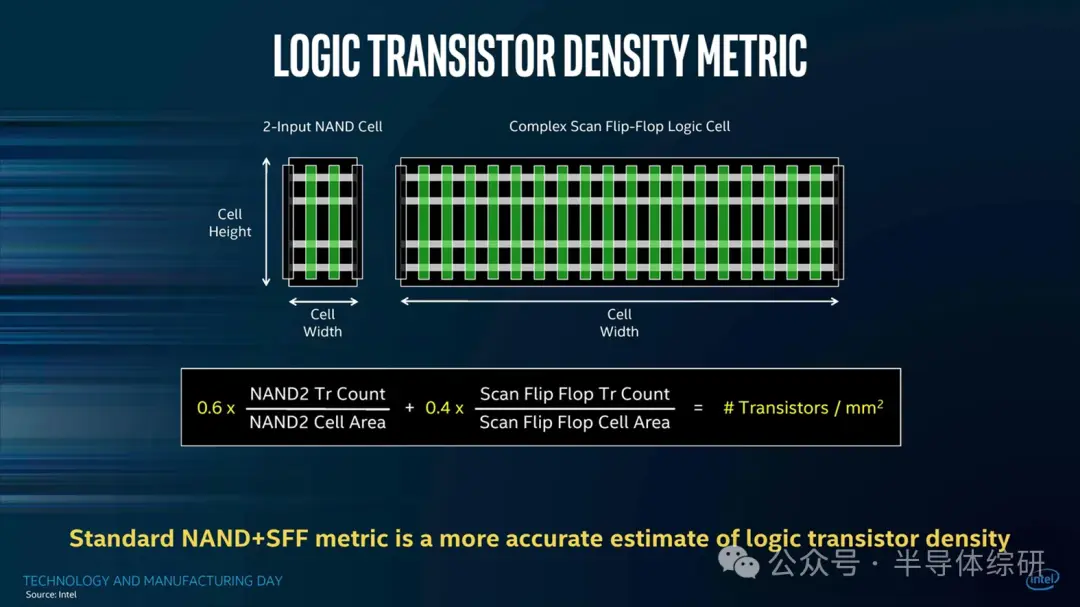

下图是Intel官方资料里晶体管密度的标准算法。通过晶体管密度就可以等效换算工艺节点的nm数了

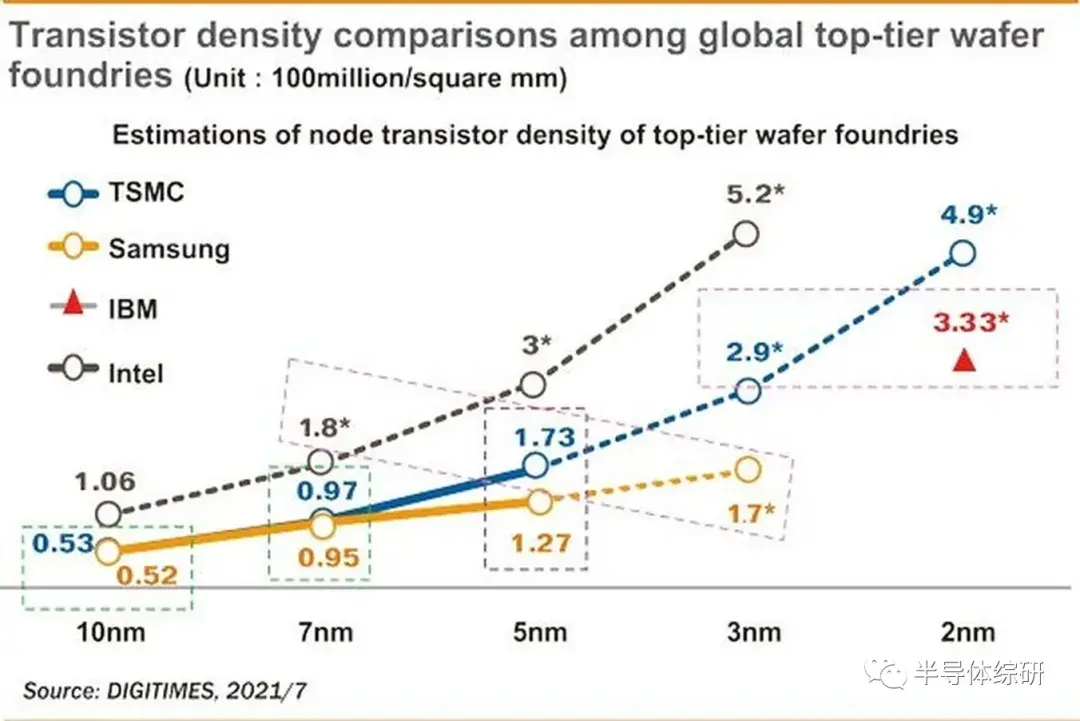

不过这个等效的计算方式各家也有不同依据,导致其中也有大量水分和猫腻。从下图可见,不同厂家所谓的同一工艺节点上,实际晶体管密度都不一样

以7nm为例,TSMC和三星的晶体管密度都分别只有每平方毫米0.97和0.95亿个晶体管,而英特尔的7nm则达到1.8亿个。所以不是晶圆制造领域的专业认识很容易被这些标称线宽所迷惑

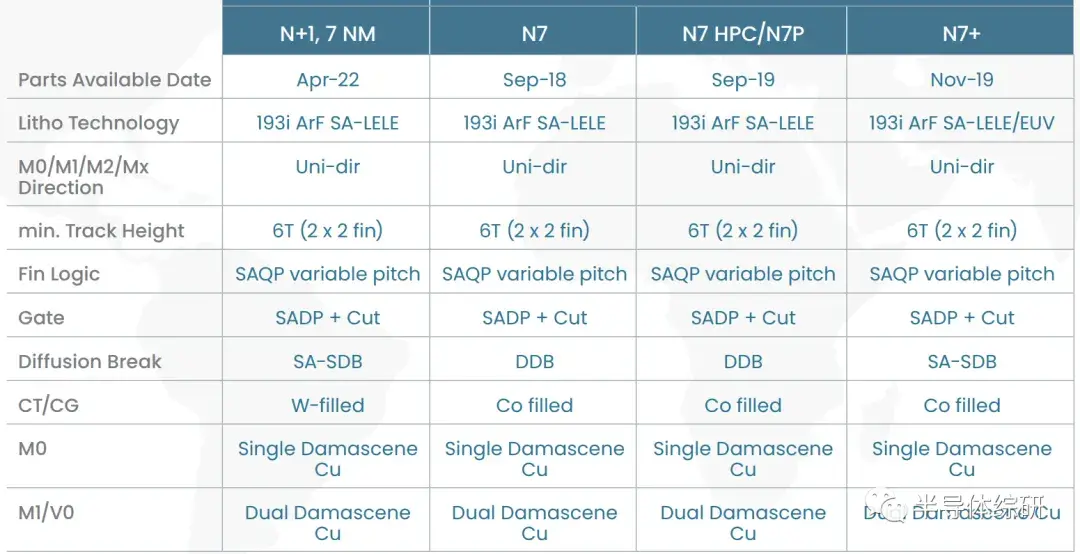

那行业内的人是用什么指标来具体衡量一个工艺的实际情况呢?大家不妨看看下图中,Techinsight做的两家晶圆厂7nm工艺技术的参数对比:

来源:半导体综研

-

芯片

+关注

关注

460文章

52616浏览量

442623 -

晶体管

+关注

关注

77文章

10029浏览量

142119 -

7nm

+关注

关注

0文章

267浏览量

35910

发布评论请先 登录

一文详解Advanced IO wizard异步模式

基于AMD Versal器件实现PCIe5 DMA功能

Inphi借助Cadence技术完成7nm全芯片扁平化设计流片

IBM Spectrum LSF如何助力半导体企业应对AI时代的高性能芯片需求

三星在4nm逻辑芯片上实现40%以上的测试良率

北京市最值得去的十家半导体芯片公司

精密几何测量技术在电子芯片制造中的重要性

所谓的7nm芯片上没有一个图形是7nm的

所谓的7nm芯片上没有一个图形是7nm的

评论