本文主要介绍FinFet Process Flow—哑栅极的形成。

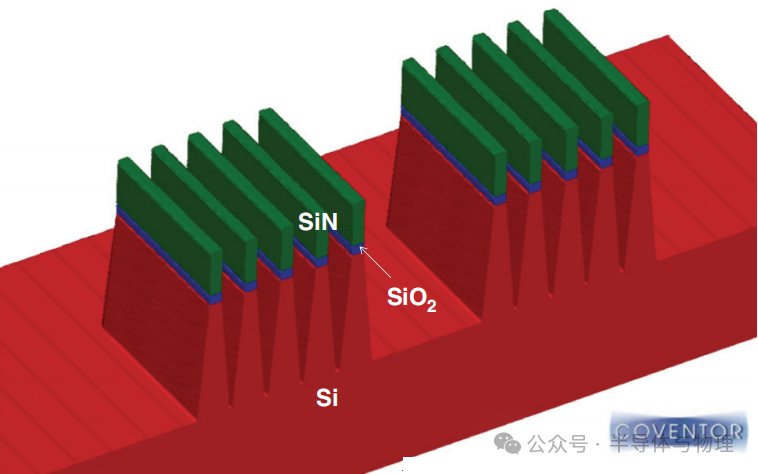

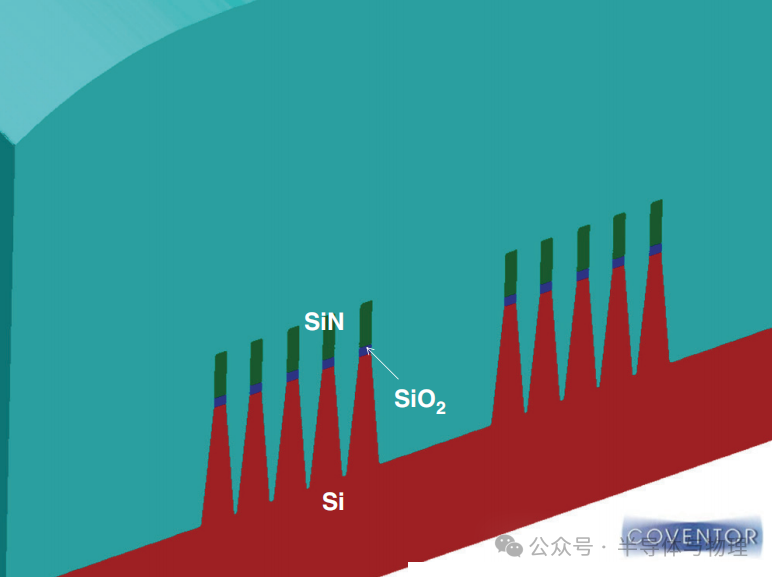

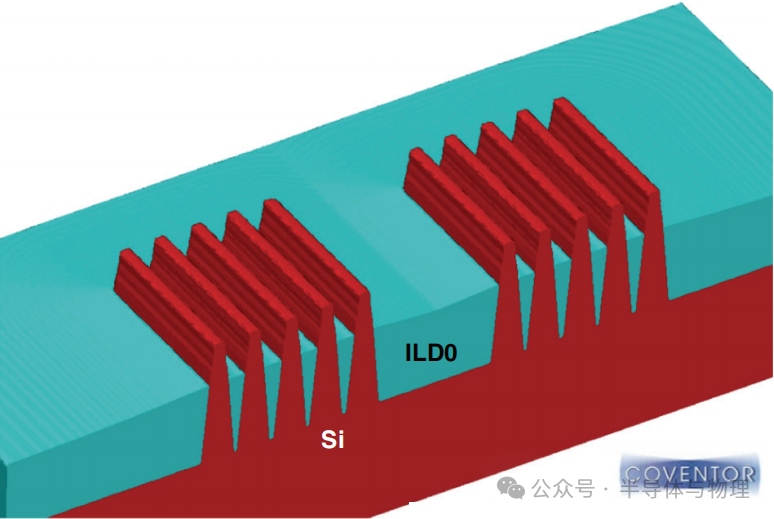

鳍片(Fin)的形成及其重要性

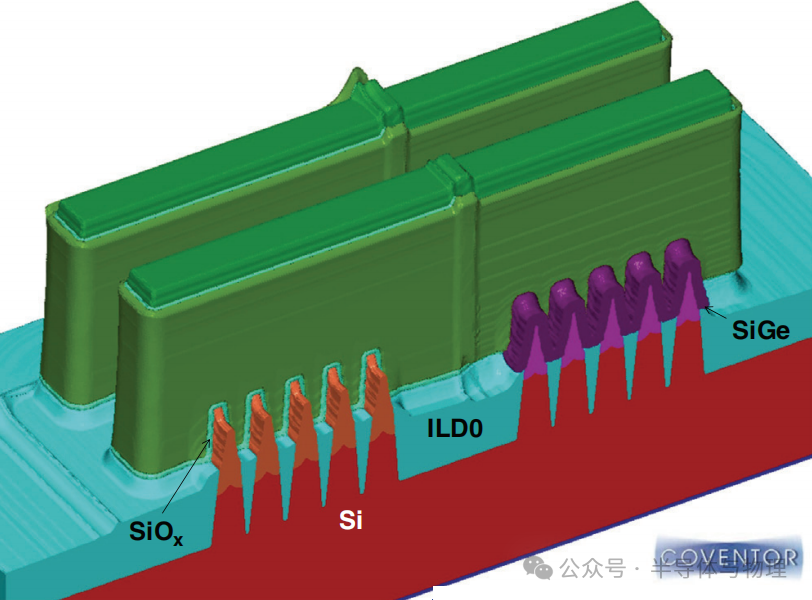

鳍片是FinFET器件三维结构的关键组成部分,它类似于鱼鳍的形状,因此得名。鳍片的高度直接决定了FinFET的栅极宽度,这对于控制电流流动至关重要。在22nm及以下技术节点中,由于鳍片尺寸非常小,通常通过SADP(Self-Aligned Double Patterning)或SAQP(Self-Aligned Quadruple Patterning)等图案化技术来实现。

初步处理与ILD层沉积

ILD层沉积

随后,在清洁后的晶圆上沉积一层ILD(Inter Layer Dielectric)一般使用SiO2 Coat。ILD的主要作用是在鳍片之间提供电气隔离,并作为后续CMP(化学机械抛光)过程中的填充材料。选择适当的ILD材料对于确保良好的电学性能和平坦度非常重要。

ILD CMP

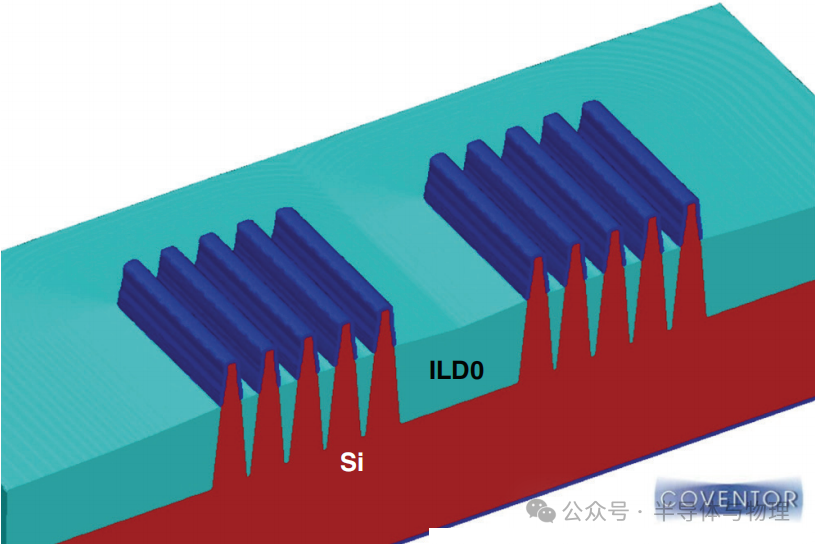

接下来进行的是ILD CMP,即使用氮化硅(SiN)作为终点检测材料来进行化学机械抛光。CMP的目标是使ILD层表面变得非常平坦,以便于后续的图案化和蚀刻操作。CMP过程中必须精确控制抛光量,以避免过度侵蚀下面的关键结构。

移除SiN和垫氧化层

CMP完成后,需要移除覆盖在鳍片上的氮化硅硬掩膜以及垫氧化层。这个步骤通常通过湿法蚀刻完成,它不仅清除了这些临时保护层,还暴露出鳍片顶部的硅表面,为后续的掺杂做准备。

牺牲氧化层生长与阱区掺杂

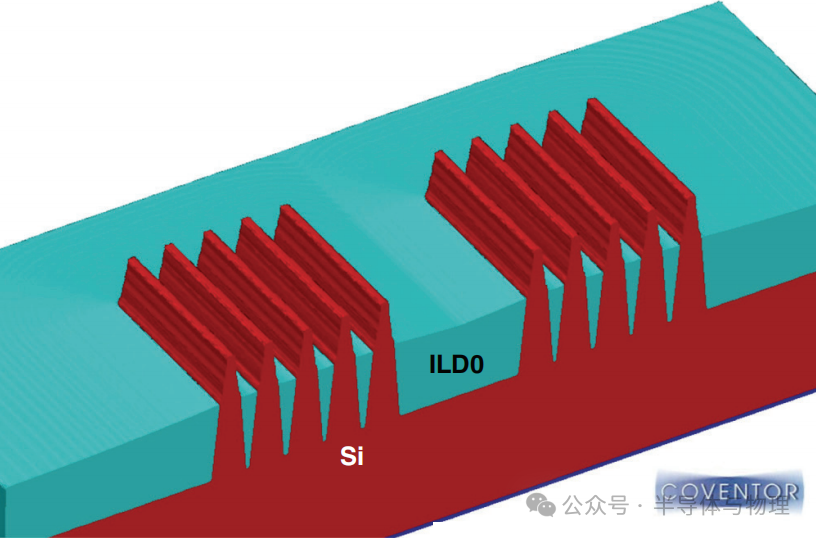

牺牲氧化层生长

紧接着,在鳍片表面生长一层薄的牺牲氧化层。该层用于后续的阱区掺杂过程中保护鳍片免受直接损伤。此外,牺牲氧化层还可以帮助定义掺杂区域的边界,提高掺杂精度。

阱区掺杂

应用一个阱区植入掩模,并执行离子注入以形成通道和基板之间的隔离阱。这个步骤是为了创建p型或n型阱区,从而为PMOS和NMOS器件分别提供适当的背景掺杂。之后,移除牺牲氧化层并清洗晶圆,确保没有残留物影响后续工艺。

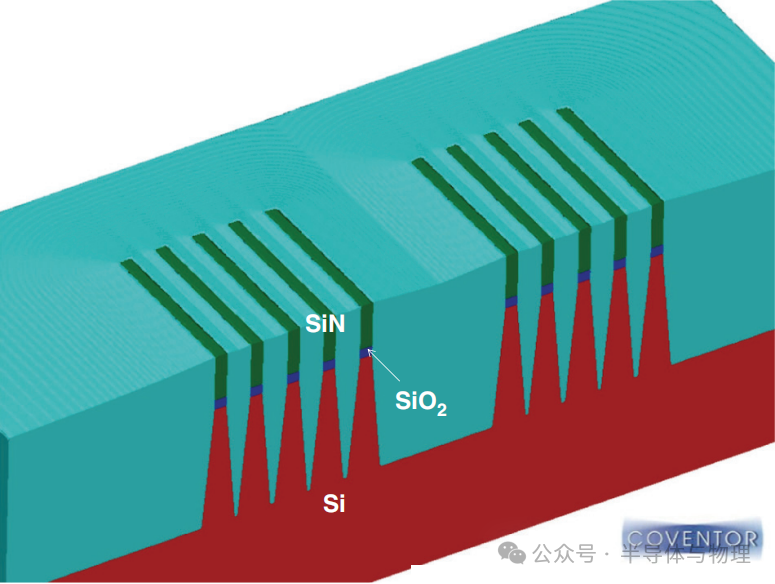

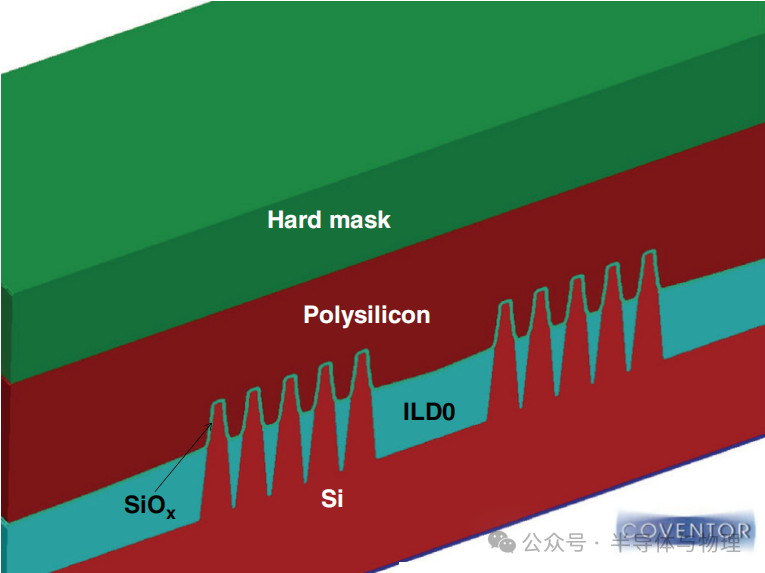

哑栅极结构形成

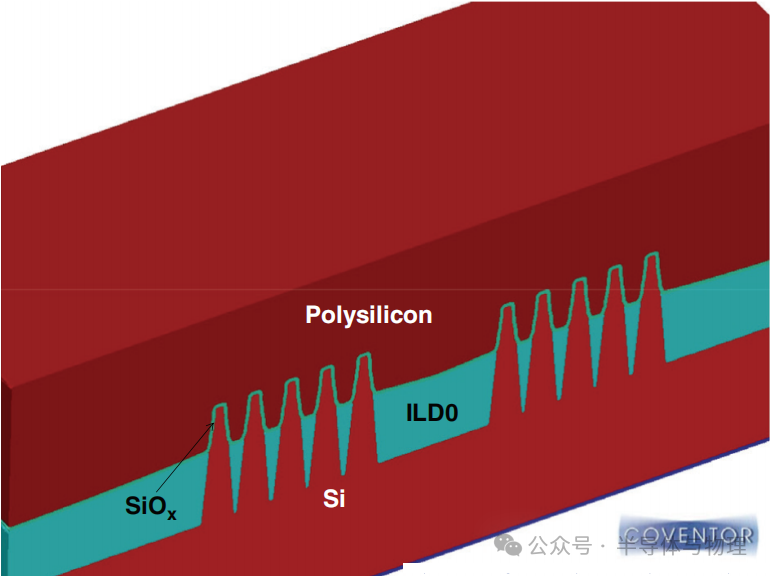

哑栅极氧化层沉积

为了构建临时的栅极结构,先在晶圆上沉积一层哑栅极氧化层。这层氧化物将作为后续多晶硅沉积和平坦化的基础。

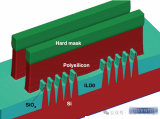

多晶硅沉积与CMP

然后,在整个晶圆表面沉积一层多晶硅,并通过CMP使其平坦化。多晶硅层将充当临时栅极材料,直到最终的高k金属栅极替换它为止。CMP过程中要保证多晶硅层厚度均匀,以支持后续的图案化步骤。

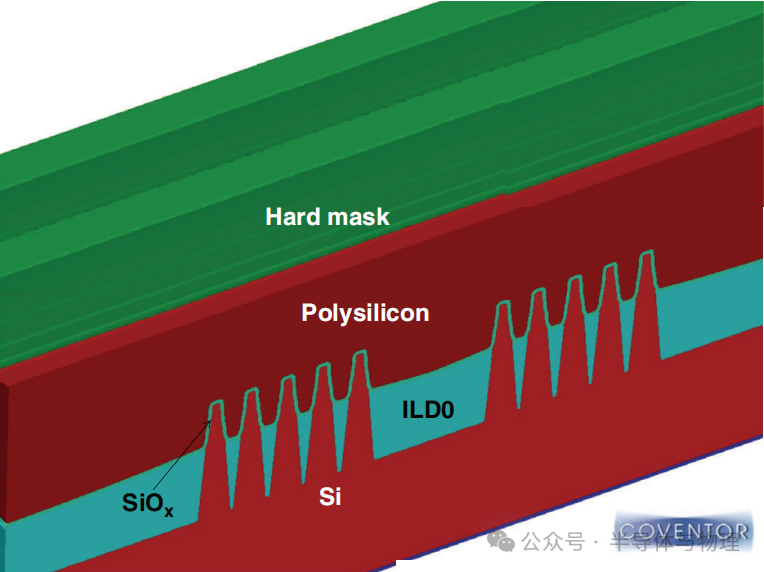

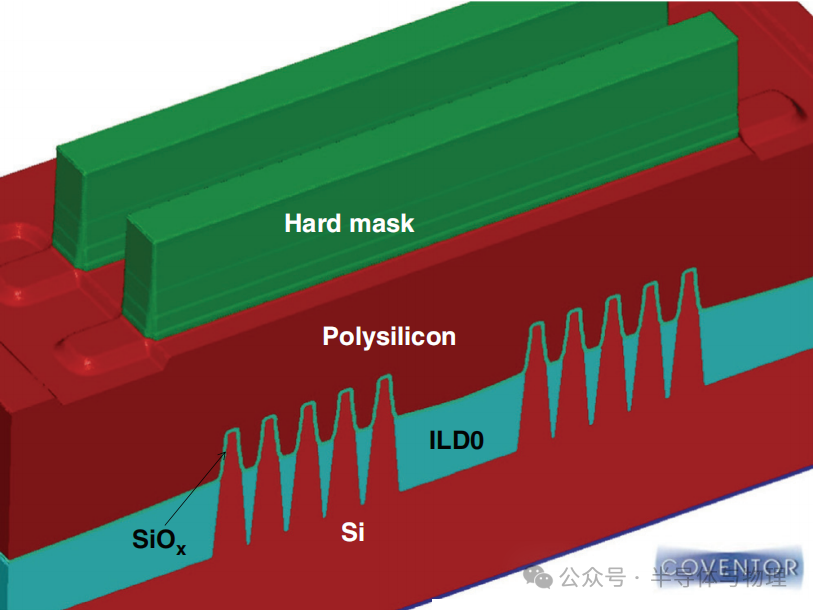

硬掩膜沉积

接着,在多晶硅层上沉积一层硬掩膜(HM),用于指导后续的栅极图案化。根据技术节点的不同,如果栅极间距大于80nm,则可以使用单次193nm浸没式光刻来形成线-空图案;而对于更小的栅极间距,则需要采用如SADP或SAQP等倍增技术。硬掩膜的选择和沉积条件对于后续图案化的精度至关重要。

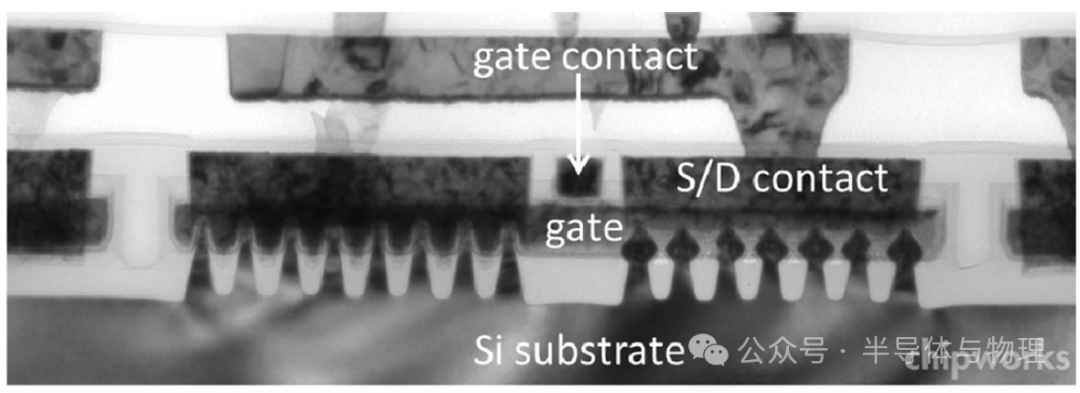

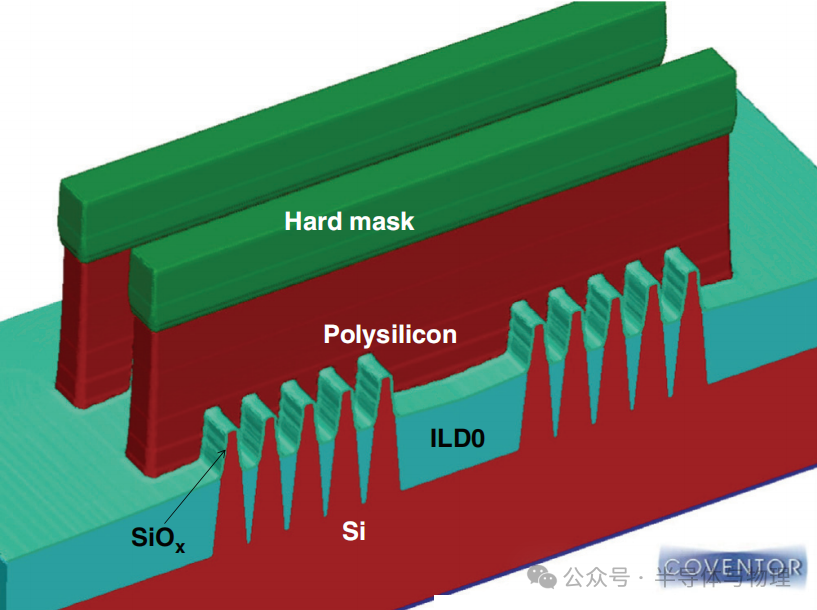

栅极图案化

应用栅极掩模以在光刻胶中形成线-空图案。经过硬掩膜蚀刻、光刻胶剥离和清洁后,再施加切割掩模并通过蚀刻切断硬掩膜线条图案。最后,利用形成的硬掩膜图案蚀刻多晶硅,从而创建出设计好的哑栅极结构。

参考文献

[1]Bellingham, Washington, USA : SPIE, [2016] | Includes bibliographical references and index.

[2]Maurya, Ravindra Kumar, and Brinda Bhowmick. "Review of FinFET devices and perspective on circuit design challenges."Silicon14.11 (2022): 5783-5791.

-

栅极

+关注

关注

1文章

185浏览量

21398 -

FinFET

+关注

关注

12文章

257浏览量

91288

原文标题:FinFet Process Flow-哑栅极的形成

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

FLOW Digital Infrastructure宣布在东京市中心新建数据中心

体硅FinFET和SOI FinFET的差异

软通动力与Qualsen(高勘技术)达成战略合作,打造通信行业“哑资源”智能管理新模式

晶体管栅极结构形成

AMD Versal自适应SoC器件Advanced Flow概览(下)

AMD Versal自适应SoC器件Advanced Flow概览(上)

U50的AMD Vivado Design Tool flow设置

如何实现“哑”设备与运维人员的“对话”

FinFet Process Flow—哑栅极的形成

FinFet Process Flow—哑栅极的形成

评论