概述

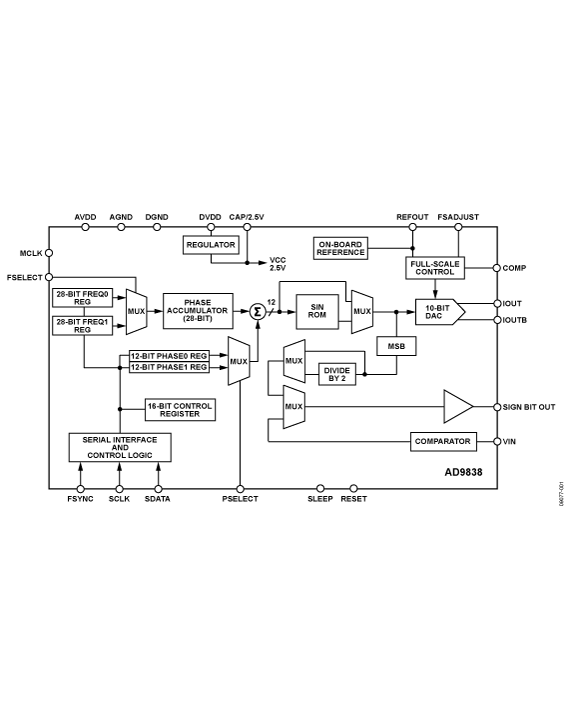

AD9838是一款低功耗DDS器件,能够产生高性能正弦波和三角波输出。其片内还集成一个比较器,支持产生方波以用于时钟发生。当供电电压为2.3 V时,其功耗仅为11 mW,非常适合对功耗敏感的应用。

AD9838提供相位调制和频率调制功能。频率寄存器为28位;时钟速率为16 MHz时,可以实现0.06 Hz的分辨率;而时钟速率为5 MHz时,则可以实现0.02 Hz的分辨率。配置频率和相位调制的方法是通过串行接口加载寄存器,然后通过软件或FSELECT/PSELECT引脚切换寄存器。

AD9838通过一个3线串行接口写入数据。该串行接口能够以最高40 MHz的时钟速率工作,并且与DSP和微控制器标准兼容。

该器件采用2.3 V至5.5 V电源供电。模拟和数字部分彼此独立,可以采用不同的电源供电;例如,AVDD可以是5 V,而DVDD可以是3 V。

AD9838具有关断引脚(SLEEP),支持从外部控制关断模式。器件中不用的部分可以关断,以将功耗降至低点。例如,在产生时钟输出时,可以关断DAC。

AD9838采用20引脚LFCSP_WQ封装。

数据表:*附件:AD9838 11mW功耗、2.3V至5.5V的完整DDS技术手册.pdf

应用

特性

- 2.3 V至5.5 V电源供电

- MCLK速率:16 MHz(B级),5 MHz(A级)

- 输出频率高达8 MHz

- 正弦波/三角波/方波输出

- 片上集成比较器

- 3线SPI接口

- 扩展温度范围:?40°C至+125°C

- 关断选项

- 当供电电压为2.3 V时,功耗为11 mW

- 20引脚LFCSP封装

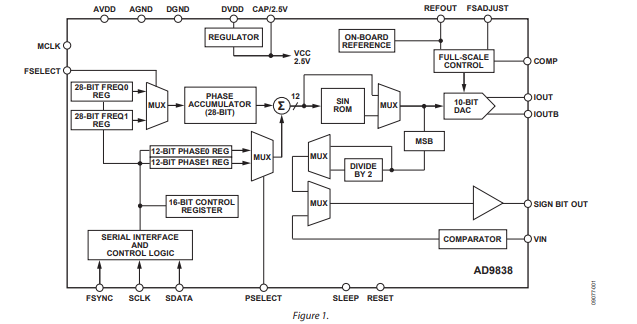

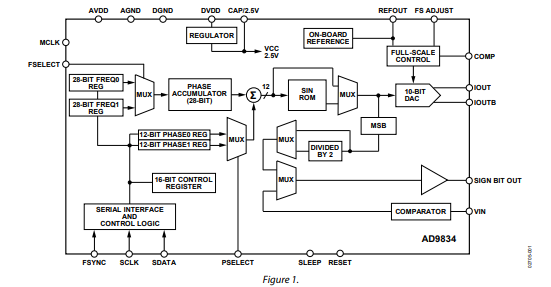

框图

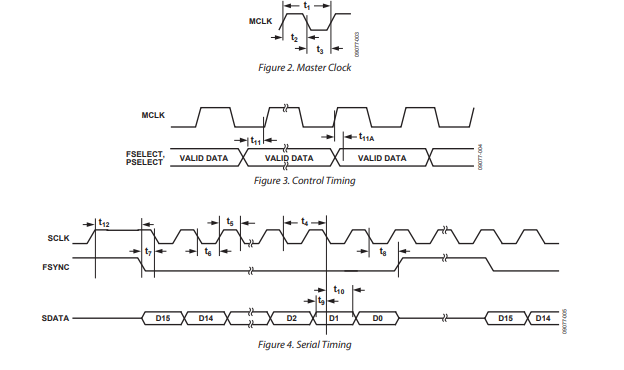

时序图

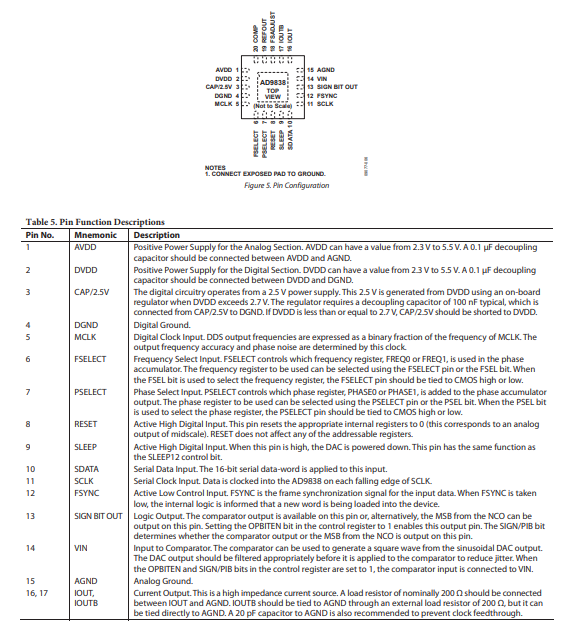

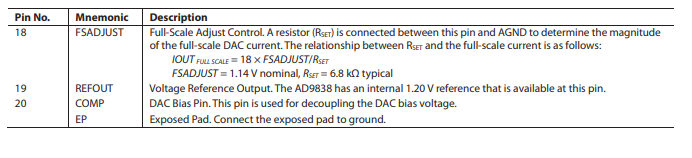

引脚配置描述

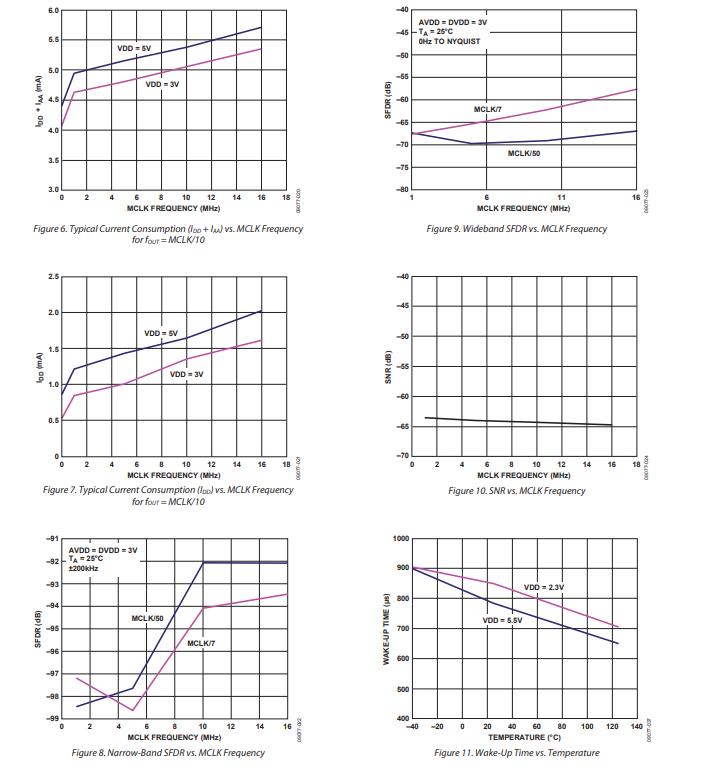

典型性能特征

应用信息

AD9838提供的多种输出选项,使其适用于广泛的应用场景,包括调制应用。AD9838可用于执行简单的调制方式,如频率转换键控(FSK)。更为复杂的调制方案,如高斯最小移频键控(GMSK)和正交相移键控(QPSK),也能通过AD9838来实现。

在FSK应用中,AD9838的两个频率寄存器会被加载不同的值。其中一个频率代表频移空间频率,另一个则代表标记频率。通过使用数字数据流中的FSELECT引脚,AD9838可在这两个频率之间对载波频率进行调制。

AD9838配备两个相位寄存器,这使得该器件能够实现相移键控(PSK)。在PSK调制中,当调制器的最低有效位(LSB)输入为高电平时,载波频率的相位会发生相应的改变。

AD9838同样适用于信号发生器应用。利用板载比较器,该器件可用于生成方波。

鉴于其低电流消耗特性,该器件也适用于可将其用作本地振荡器的应用场景。

接地与布局

承载AD9838的印刷电路板在设计时,应确保模拟部分和数字部分相互分离并限定在特定区域内。这有助于实现接地层的分离,而这是一种普遍认为能为接地平面提供最佳屏蔽效果的技术。数字接地平面和模拟接地平面应仅在一处连接。对于AD9838而言,是唯一需要进行AGND(模拟地)到DGND(数字地)连接的器件,其AGND引脚和DGND引脚应进行连接。如果在一个系统中,多个器件都需要AGND到DGND的连接,那么连接点应仅设置一个,并且应尽可能在靠近AD9838的位置建立稳定的接地路径。

应避免在器件下方布设数字线路,因为这些线路会引入噪声。模拟接地平面应在AD9838下方铺设,以防止噪声耦合。为AD9838供电的电源线应尽可能宽,以便降低阻抗,并减少电源线上的尖峰噪声。像时钟信号这类快速开关信号,应使用数字接地进行屏蔽,以避免其向电路板的其他部分辐射噪声。

要防止数字信号与模拟信号交叉。电路板两侧的走线应相互垂直,以减少馈通效应。在双层板中,微带线技术通常是最佳选择,但并非总是可行,因为电路板的另一侧往往要专门用于接地平面,而信号则布置在另一侧。

良好的去耦至关重要。AD9838的模拟电源和数字电源相互独立,分别引出,以尽量减少模拟部分与数字部分之间的耦合。所有模拟电源和数字电源都应进行去耦处理,将AGND和DGND分别与0.1 μF陶瓷电容并联10 μF钽电容 。为实现最佳的去耦性能,这些电容应尽可能靠近器件放置,理想情况是紧贴器件。

在使用同一电源为AD9838的AVDD(模拟电源)引脚和DVDD(数字电源)引脚供电的系统中,建议采用系统电源旁路。推荐在AVDD引脚处采用模拟电源去耦,在DGND引脚与DVDD引脚之间采用数字电源去耦。

比较器的正常运行需要合理的布局策略。布局时必须尽量减少Vs引脚与SIGN BIT OUT引脚之间的寄生电容。例如,在多层电路板中,Vs信号可连接到顶层,而SIGN BIT OUT引脚可连接到底层。通过这种方式,可在Vs与SIGN BIT OUT引脚之间的电源层和接地层提供隔离。

与微处理器接口

AD9838具有标准串行接口,可使其直接与多个微处理器连接。该器件使用外部串行时钟将数据或控制信息写入内部。串行时钟的频率最高可达40 MHz。串行时钟可以是连续的,也可根据需要空闲或保持低电平。每次向AD9838写入数据时,FSYNC(帧同步)信号都会被拉低,并保持低电平状态,直至16位数据写入完成。FSYNC信号用于将加载到AD9838中的16位信息成帧。

-

时钟

+关注

关注

11文章

1909浏览量

133476 -

DDS

+关注

关注

22文章

676浏览量

154790 -

AD9838

+关注

关注

0文章

6浏览量

8117

发布评论请先 登录

ADS112U04在2.3V~3.3V之间的IDCA的精度是怎么样的?

AD9838没有输入下限是指时钟可以很低

2.3V至5.5V的LMX2306/16/26频率合成器

AD9838和AD9837:直接数字频率合成IC

AD9838,pdf (2.3V至5.5V的完整DDS器件)

11毫瓦功率2.3V到5.5V完整的数字显示示波器ad9838数据表

AD9838 11 mW功耗、2.3 V至5.5 V的完整DDS

UG-269:评估AD9837低功耗8.5 mW、2.3 V至5.5 V可编程波形发生器

AD9834 20 mW功耗、2.3 V至5.5 V、75 MHz完整DDS技术手册

AD9838 11mW功耗、2.3V至5.5V的完整DDS技术手册

AD9838 11mW功耗、2.3V至5.5V的完整DDS技术手册

评论