概述

AD8343是一款高性能、宽带有源混频器,具有极低交调失真,所有端口均具有宽带宽,非常适合要求严格的发射应用或接收通道应用。

AD8343的典型变频增益为7 dB。集成的LO驱动器以低LO驱动电平,支持50 Ω差分输入阻抗,有助于将外部元件数降至较少。

开发差分输入可以直接与差分滤波器接口,或通过平衡-不平衡变换器(变压器)驱动,由单端源提供平衡驱动。

开集差分输出可以用来驱动差分中频信号接口,或通过匹配网络或变压器转换为单端信号。以VPOS电源电压为中心时,输出摆幅为±1 V。

LO驱动器电路的典型功耗为15 mA。可利用两个外部电阻来设置混频器内核电流,以达到要求的性能,总电流为20 mA至60 mA。采用5 V单电源供电时,相应的功耗为100 mW至300 mW。

AD8343采用ADI公司的高性能25 GHz硅双极性IC工艺制造,提供14引脚TSSOP封装,工作温度范围为?40°C至+85°C,同时提供配置齐全的评估板。

数据表:*附件:AD8343 DC至2.5 GHz 、高IP3有源混频器技术手册.pdf

应用

特性

- 高性能有源混频器

- 宽带操作,频率最高达2.5 GHz

- 转换增益:7 dB

- 输入IP3:16.5 dBm

- LO驱动:–10 dBm

- 噪声系数:14 dB

- 输入P1dB:2.8 dBm

- 差分LO、IF和RF端口

- 50 Ω LO输入阻抗

- 单电源供电:5 V(50 mA,典型值)

- 省电模式:20 ?A(典型值)

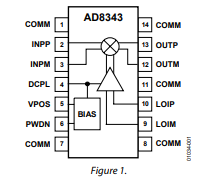

框图

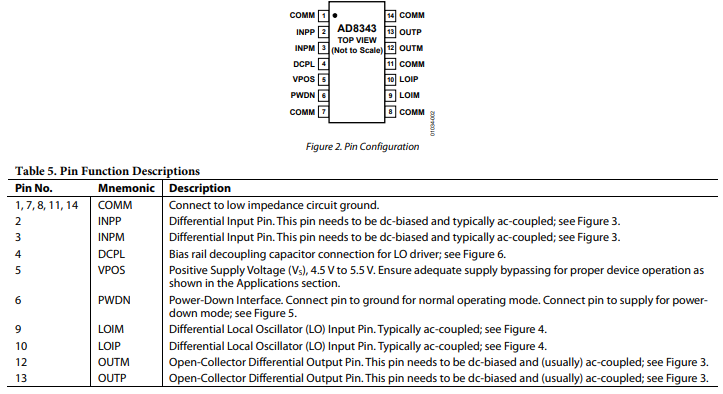

引脚配置描述

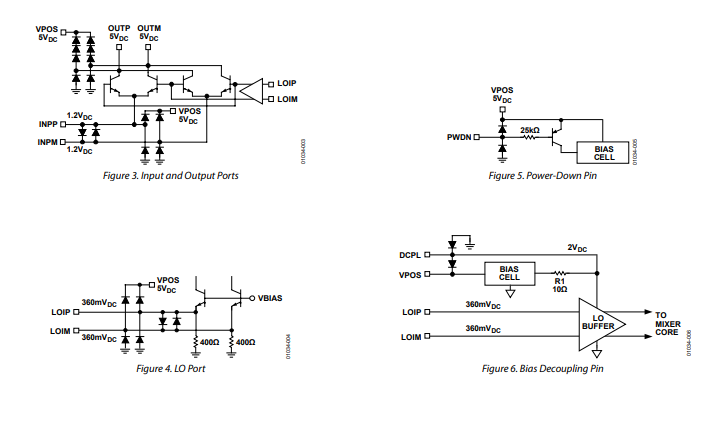

简化接口示意图

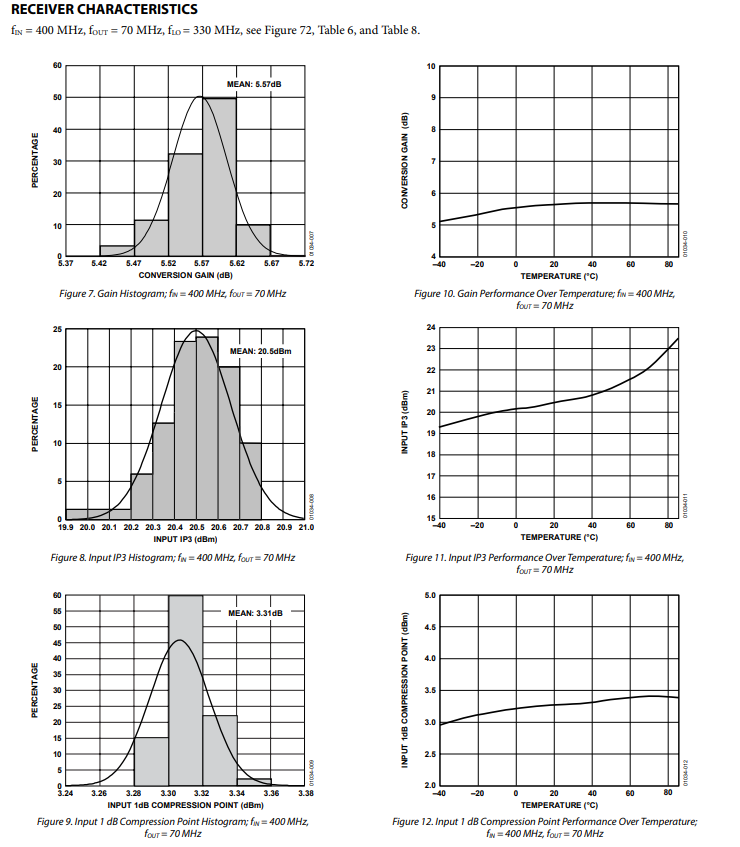

典型性能特征

电路描述

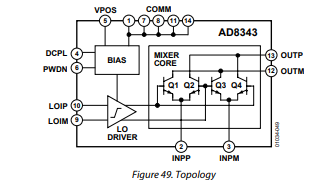

AD8343 是一款适用于高截点应用的混频器。其信号路径完全为差分且直流耦合,能够在宽频率范围内实现高性能运行。功能模块的基本框图见图 49。偏置单元为本地振荡器(LO)驱动器和核心提供与绝对温度成比例(PTAT)的偏置。LO 驱动器由三级限幅差分放大器组成,能为混频器核心的基极提供极快速(近乎方波)的驱动。

AD8343 核心采用标准架构,通过施加信号输入来激励单元中的晶体管(见图 49 和图 55)。基极由限幅的内部 LO 信号驱动,该信号引导晶体管在输出端之间交替切换,从而使信号与 LO 方波进行周期性极性反转,实现乘法运算。

为说明此功能,当 LOIP 为正时,Q1 和 Q4 导通,Q2 和 Q3 截止。在此状态下,Q1 将 I_{INSP} 连接至 OUTP,Q4 将 I_{INSM} 连接至 OUTM。当 LOIP 为负时,晶体管角色反转,I_{INSM} 连接至 OUTP,I_{INSP} 连接至 OUTM。通过共基极晶体管放大器对实现隔离和增益,可在任何瞬间保证信号通过。

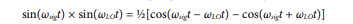

乘法运算会产生频率混频,理想的乘法器可构成出色的混频器。该原理可用以下三角函数恒等式表示:

这表明两个不同频率的正弦波相乘,结果是一对频率等于两相乘频率之和与差的正弦波。

遗憾的是,由于线性度不佳以及添加噪声,模拟乘法器在实际应用中通常并非理想的混频器,这在试图提高线性度时尤为明显。但本章节中的混频器通过使信号周期性地反转极性来解决此问题。在此类混频器中,频率转换是信号与 LO 频率处的方波相乘的结果。由于方波除基频外还包含奇次谐波,信号会被 LO 的每个频率分量有效地相乘。混频器输出为

等。LO 谐波产生的分量幅度随谐波阶数增加而减小,因为方波谐波的幅度会随谐波阶数增加而减小。

图 50 展示了此过程的一个示例。该图第一部分显示一个 800MHz 的正弦波代表输入信号,第二部分是一个 600MHz 的方波代表 LO 信号,第三部分展示了输出变换的时域表示,第四部分展示了频域表示。频谱中最强的两条线是由 LO 基频乘法产生的和频与差频。较弱的谱线是信号与 LO 方波各谐波相乘的结果。

应用

下变频混频器

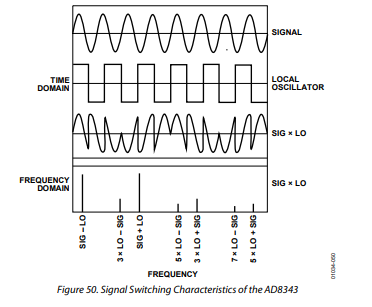

典型的下变频应用如图 69 所示,这是一个与 DC 电路相连的接收混频器。单端输入通过 1:1 传输线巴伦转换为差分信号,输入匹配网络位于巴伦和输入引脚之间。LO 信号通过一个 2:1 匝数比变压器传输到本地振荡器引脚,-12dB 至 -3dB 的电平通过第二个 1:1 巴伦传输到差分输出阻抗。

中频输出通过 4:1(阻抗比)变压器获取,该变压器可将 200Ω 差分负载反射到集电极。这种输出耦合方式具有较宽的带宽,不过在某些情况下,用户可能希望在集电极处添加谐振槽路电路,以提供一定的中频选择性。与输出变压器中心抽头串联的铁氧体磁珠(FB)可解决共模稳定性问题。

在此电路中,PWDWN 引脚接地,使混频器处于工作状态。DCPI 引脚通过约 0.1μF 的电容接地。不将 DCPI 引脚接地会使器件输出产生较高的噪声电平。

R1A 和 R1B 将核心偏置电流设置为每侧 18.5mA。L1A 和 L1B 提供所需的射频扼流圈,以避免信号分流,Z2A 和 Z2B 构成匹配网络,用于匹配 AD8343 的差分输入阻抗与变压器的差分输出阻抗。

AD8343 的本地振荡器引脚和 IO 引脚设计用于与巴伦和 1:1 巴伦配合工作。宽带模式下,每侧核心电流设置为 18mA。Z1、Z1A、Z2A 和 Z2B 构成匹配网络,旨在将 AD8343 的差分输出阻抗匹配到巴伦的差分输入阻抗。假设输出频率足够高,器件的输入阻抗远小于偏置电阻值,这样可使输入偏置电流消除,且对增益或互调失真几乎没有影响。

在此示例中,输出信号通过差分匹配网络获取,计算 Z2 和 Z2A/Z2B,然后通过 1:1 巴伦和隔直电容连接到单端输出。

假设输出频率足够高,对 AD8343 输出进行共轭匹配是理想的,这样可使器件输出与巴伦差分输入之间实现共轭匹配。

此电路通过并联方式为输出晶体管集电极提供偏置电流,因为没有方便的中心抽头。铁氧体磁珠与输出偏置电感串联,可提供一些阻尼,有助于避免这种输出巴伦可能出现的常见模式振荡。这种振荡会给输入电路带来负担,可能导致输入电路出现过稳定性故障,在宽频率范围内呈现感性阻抗。

PWDWN 引脚接地,使混频器处于工作状态。DCPI 引脚必须通过约 0.1μF 的电容接地,以抑制内部偏置电路产生的噪声。

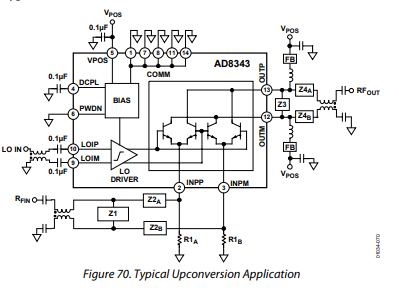

上变频混频器

典型的上变频应用如图 70 所示,这是一个单端输入到差分转换的上变频应用。两种配置均通过 1:1 传输线巴伦实现。

-

混频器

+关注

关注

10文章

847浏览量

47537 -

变频

+关注

关注

1文章

460浏览量

34702 -

有源

+关注

关注

0文章

150浏览量

23123

发布评论请先 登录

请问AD8343的S参数仿真的外围电路怎样设计?

DC1983A,使用LTC5510,1 MHz至6 GHz宽带高线性有源混频器的演示板

AD8343 DC至2.5 GHz 、高IP3有源混频器

HMC485AMS8GE:高IP3 GaAs MMIC I/Q混频器,带集成LO放大器,1.7至2.4 GHz初步数据表

高性能宽带有源混频器AD8343ARUZ 概述

聊聊混频器IP3的测量以及测试误差的来源分析

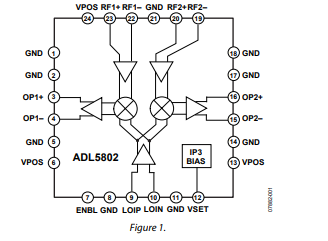

ADL5802双通道、高IP3、100MHz ~ 6GHz有源混频器技术手册

AD8343 DC至2.5 GHz 、高IP3有源混频器技术手册

AD8343 DC至2.5 GHz 、高IP3有源混频器技术手册

评论