本文深入解析两类应力的形成机制,揭秘从工艺优化(如LPCVD参数调控)到材料设计的全链条应对策略,并探讨如何将热应力“化敌为友”,为高可靠性MEMS器件的研发提供关键理论支撑。

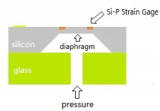

残余应力一直是MEMS技术发展中的一个重要问题,MEMS 器件中的残余应力会对器件的性能以及可靠性产生重要影响。根据其产生的原因,一般可将残余应力分为本征应力和热失配应力两大类。本征应力的成因比较复杂,主要是由于晶格失配引起的,而热失配应力是由于不同材料的热膨胀系数差异引起的。

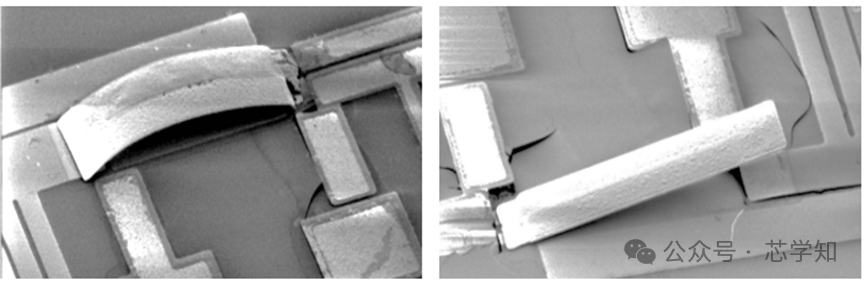

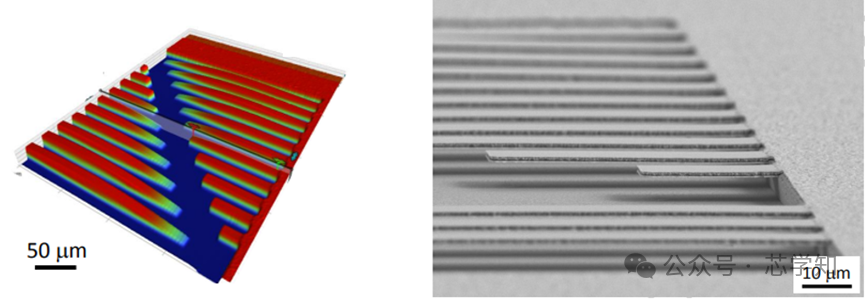

图 应力失配悬臂梁SEM

什么是本征应力?

本征应力又称内应力,是指在室温和零外加负载的情况下,材料自身内部存在的应力,分为压应力和张应力。在MEMS薄膜材料中,表现尤为突出,当内应力在薄膜材料厚度方向分布不均匀时,会产生应力梯度。当应力梯度不足以抵抗薄膜自身的弹性模量时,薄膜会产生变形,从而带动衬底产生翘曲或薄膜与衬底分离而破裂。除了单层膜存在应力梯度,复合膜的组合应力更加值得关注。在MEMS器件中,有大量的悬膜和悬臂梁为复合膜结构,此类复合膜结构设计的关键点为对膜层的应力匹配和补偿。

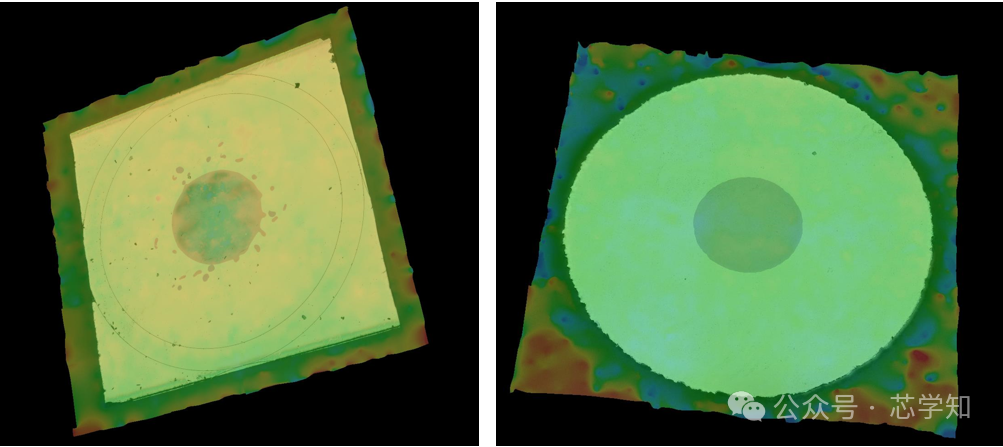

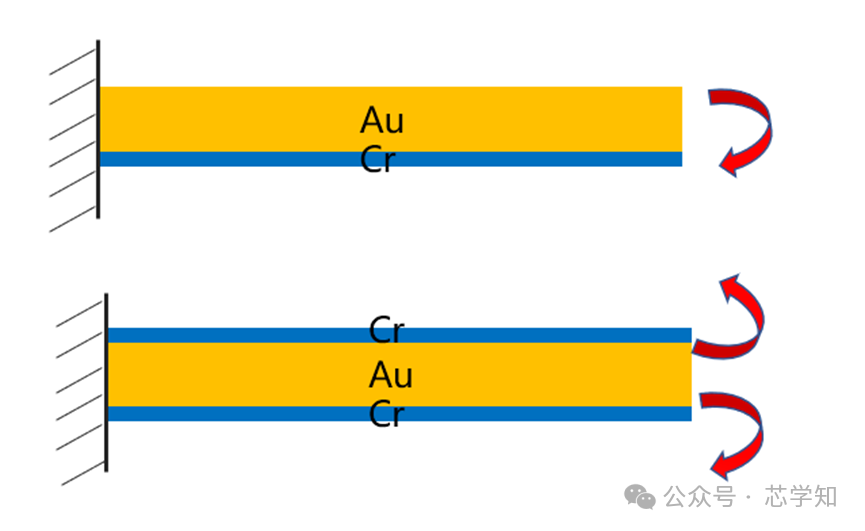

图 本征应力引起的膜层变形:非应力匹配膜层和应力匹配膜层

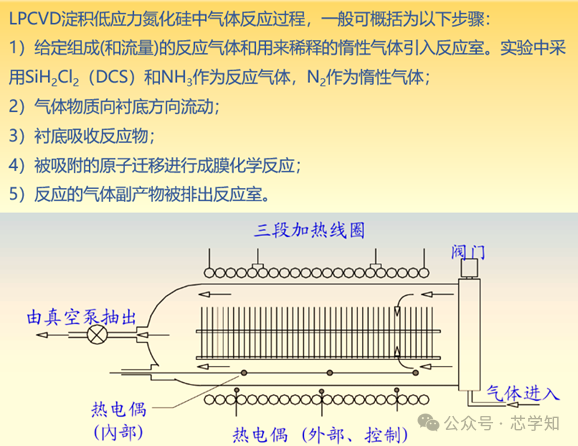

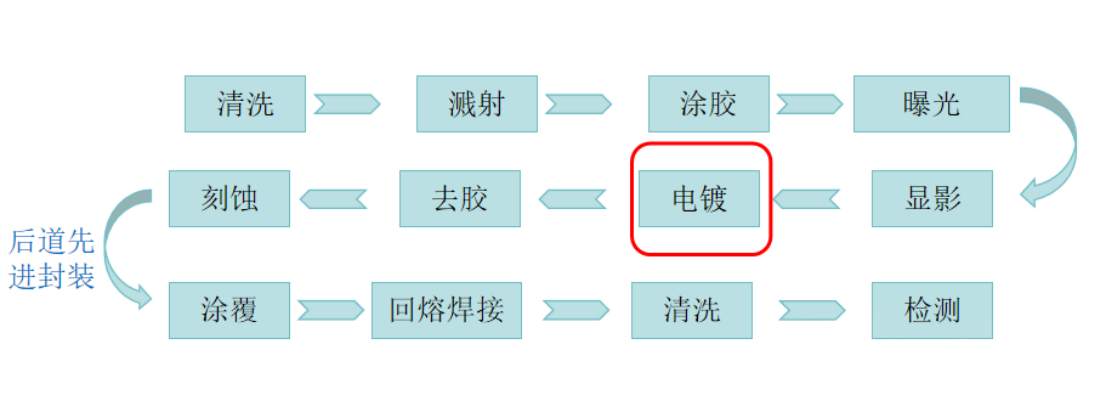

本征应力的产生主要是源于沉积薄膜的过程中,成膜的方法、温度、压强和速率等因素引起内部晶格失配,例如金属金(Au)薄膜采用蒸镀成膜比磁控溅射成膜具有更低的本征应力。在MEMS常用的材料中,几乎不存在本征应力为零的材料。因此,在材料制备工艺中,更多的关注点在如何制备出更低应力的薄膜。采用低压化学气象沉积(LPCVD)制备的氮化硅薄膜,通过控制温度、压强、反应气体比例和反应时间等,制备低应力SiNx薄膜需要保证富硅,即高DCS/NH3比。值得注意的是,LPCVD炉管入气口和出气口与炉管中心温度存在差异,导致同一炉SiNx薄膜应力出现大的波动,应提高中心温度降低片间应力差异。

图 低应力氮化硅制备工艺

什么是热应力?

热应力又称热失配,是指不同材料由于热膨胀系数的差异引起的界面应力。产生热应力,必须满足2个条件,第一是有热膨胀系数差异的两种材料,第二是有温度变化。热应力在MEMS器件和使用过程中不可避免,若在MEMS器件制备和使用过程中,温度变化引起的热应力导致器件或者膜层的非弹性变形(塑性变形),则会造成器件制备的失败和使用的可靠性问题。因此,我们在MEMS制备工艺过程中,热预算是随着工艺的进程逐步降低的,高温工艺一般只出现在最前道。

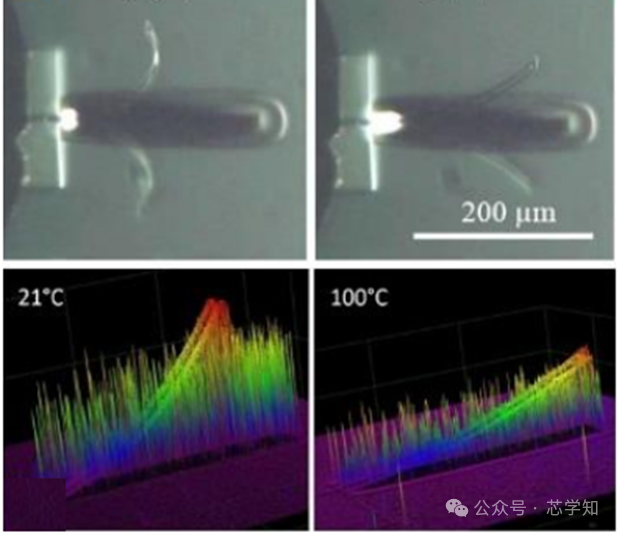

相较于本征应力,热应力在某些方面是可以化敌为友的。在MEMS热敏感执行器中,基于膜层之间的热膨胀系数差来实现悬臂梁的驱动。在双层膜形成的MEMS热驱动器中,温度升高,悬臂梁会向热膨胀系数小的一侧弯曲,当温度回降,悬臂梁回到原位。

图 热执行器(引用doi:0.1088/1361-6439/ab1633/meta)

如何实现MEMS工艺过程中的应力匹配?

MEMS工艺设计过程中,最重要的一个设计就是应力的匹配。可以说,没有合理的膜层应力匹配,制备出的MEMS器件99%是失效的。以金属悬臂梁为例,讨论应力匹配的方法。选取的材料为Cr和Au,采用磁控溅射制备的Cr薄膜,本征应力为1000MPa,热膨胀系数为4.9 e-6/°C;采用磁控溅射制备的Au薄膜,本征应力为200MPa,热膨胀系数为14.1 e-6/°C。

图 应力匹配模型示意图

两层复合膜情况:

Cr薄膜在下层,Au薄膜在上层,考虑本征应力引起的应力梯度,复合膜向应力大的方向,即向下弯曲;考虑热应力,Cr的热膨胀系数小于Au的,复合膜向热膨胀系数小的方向,即向下弯曲。实际工艺过程中Cr常作为Au的黏附层使用,通过分析发现本征应力和热应力都会使复合膜层变形,这对于器件的制备是非常不利的。解决方案一般为尽量降低Cr的成膜内应力和厚度,增加Au的厚度,以抵抗变形。

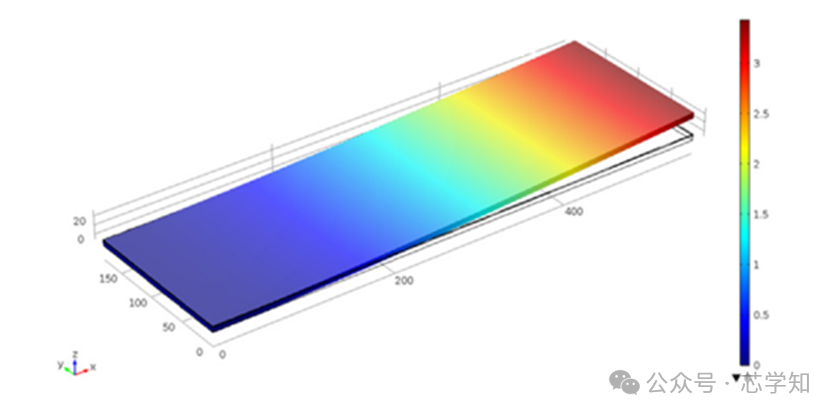

图 应力匹配力学仿真

三层复合膜情况:

Cr薄膜在下层,Au薄膜在中层,Cr在上层,即形成三明治结构。考虑本征应力梯度,复合膜向应力大的方向弯曲,即由中间Cr层同时向上下Au层弯曲,这样就实现了本征应力抵消。考虑热应力,Cr的热膨胀系数小于Au的,复合膜向热膨胀系数小的方向,即由中间Cr层同时向上下Au层弯曲,这样也实现了热应力的补偿。这里唯一要考虑的是,三明治结构,上下层应尽可能做到厚度相同,才能更好的实现本征应力和热应力的同时补偿。

图 Au-TiW双层膜应力匹配仿真和SEM(引用10.1016/j.matdes.2016.06.003)

在实际的工艺设计和制造过程中,对于复合膜的使用,通过以上分析,我们明显看到奇数层组合对应力的补偿是优于偶数层的。在MEMS器件的膜层设计中,尤其涉及同时存在正负应力的情况,应考虑的是尽可能降低单层膜的应力,在所有膜层低应力的情况下,去做应力补偿和匹配是器件设计和制造成功的关键。

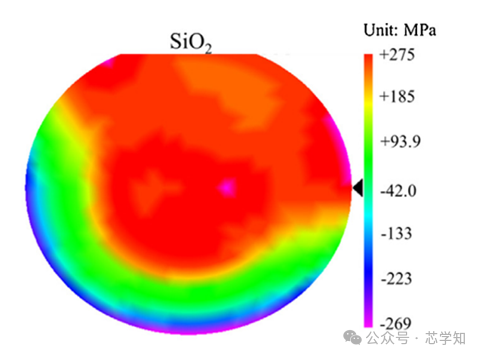

图 单层膜应力仪测试数据

-

mems

+关注

关注

129文章

4181浏览量

194700 -

热应力

+关注

关注

0文章

11浏览量

10850

原文标题:MEMS工艺制造过程中的头号大敌

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

晶圆制造中的退火工艺详解

MEMS制造中玻璃的刻蚀方法

MEMS制造领域中光刻Overlay的概念

制造误差归零:SMA 接口尺寸对工艺严苛要求揭秘

揭秘半导体电镀工艺

PanDao:光学设计中的制造风险管理

最全最详尽的半导体制造技术资料,涵盖晶圆工艺到后端封测

TRCX应用:显示面板工艺裕量分析

芯片制造的7个前道工艺

MEMS工艺制造中的首要挑战:揭秘头号大敌

MEMS工艺制造中的首要挑战:揭秘头号大敌

评论