FPGA 通过查找表 (LUT) 实现逻辑功能。这些 LUT 类似于真值表或卡诺图 (Karnaugh map),FPGA 可以通过组合多个 LUT ,来实现几乎任何你所需的逻辑功能。

通常情况下,LUT 由其可处理的输入数来指定。例如,一个 4 输入 LUT 需要 16 位来存储这 4 个输入所有可能组合对应的输出值。而对于需要 4 个以上输入的逻辑,则需要进行 LUT 级联,但 LUT 级联会造成传播时延。

使用较大的 LUT 可以减少所需的 LUT 层数,从而提高性能,但对于简单的逻辑功能来说,LUT 过大同样可能会造成浪费。为了尽量减少浪费,可以对这些 LUT 进行拆分,如何拆分 LUT 会对设备的整体利用率产生重要影响。

接下来就跟随小编一起,来探讨几种权衡取舍的方案。

查找表的实现

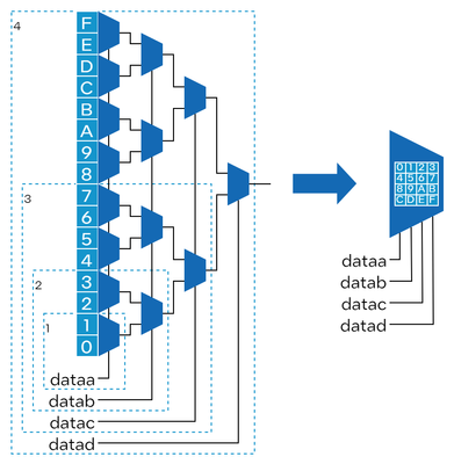

首先,让我们来看看通用 n 输入查找表的结构。查找表是一系列多路复用器,它们根据输入选择特定的存储位置,就像 1 位存储器。所需的存储位置数是 2 的输入数次幂,就像有 n 根地址引脚的存储器。

下图是一个 4 输入 LUT 的示例,其中较小的 LUT 用虚线边框表示。在下文中,我们将使用 4 输入 LUT 的简化表示法来继续进行探讨。

图 1. n 输入 LUT

增加输入位可以实现更加复杂的逻辑,但每增加一个输入位,所需的存储位和多路复用器的数量就会翻倍。在实现较为简单的逻辑时,这些额外的资源就会被浪费。为了尽量减少输入位的浪费,可以为中间多路复用器提供抽头 (tap)。

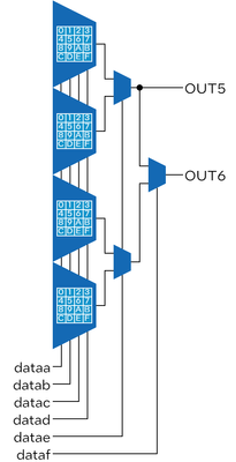

下图展示的是具有两个 5 输入 LUT 输出的 6 输入 LUT。通过这种简单的方法可以实现两个 5 输入 LUT,但局限性在于,两个 LUT 均由相同的 5 个输入控制。

图 2. 基本 6 输入 LUT

更优的方法

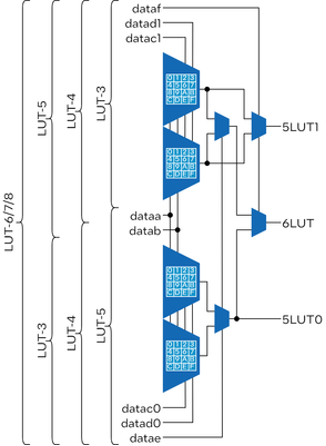

Agilex FPGA 采用了一种不同的方法,可以提高设备的利用率。如下图所示,Agilex FPGA 采用全新的 6 输入 LUT 结构,具有 8 个输入,称为自适应逻辑模块 (ALM)。部分较小 LUT 的输入被独立出来,以提供更高的灵活性。借助这些额外输入,就可将依赖于不同信号的较小逻辑功能进行组合。

下图展示了一些不同的 LUT 组合方式。

图 3. Agilex FPGA ALM

当 datac0 和 datad0 分别连接到与 datac1 和 datad1 相同的信号时,这一模块就实现了传统的 6 输入 LUT,但将其进行单独使用时,还能实现一些 7 输入和 8 输入逻辑功能。

这些额外的 7 输入和 8 输入配置,再加上所有的 3 输入、4 输入和 5 输入 LUT 配置,使得这种实现方式更加灵活,也提高了设备利用率。

对设备利用率的影响

这些优势究竟有何重要作用呢?要回答这个问题,我们需要一个指标来反映所实现的逻辑数。理想的情况是使用一个常见的函数作为参考,比如处理器内核,而且最好是一个大家熟悉并可以自由使用的处理器,例如 RISC-V 处理器。单个内核通常不足以将 FPGA 填满,因此需要一系列此类处理器,而且处理器应足够小,以便进行细粒度比较。此外,还需要一个脚本将其进行综合。然而,由于所需条件较多,专业难度较高,这很难实现。

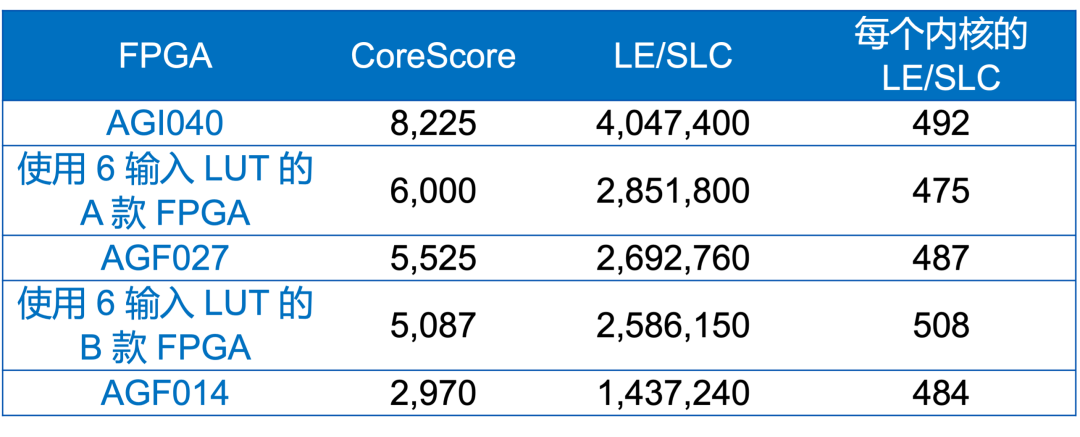

CoreScore 是专为 FPGA 及其综合/布局布线工具设计的基准评测体系。它能够测试特定 FPGA 中可以容纳的 SERV 内核数。SERV 是一种屡获殊荣的位串行 RISC-V 内核,外形非常小巧。这就提供了一个独立于供应商的衡量指标,用于体现 FPGA 的逻辑容量。

既然我们已经确定了一个用于比较的指标,那就让我们更深入地看看每种实现方式的逻辑容量。

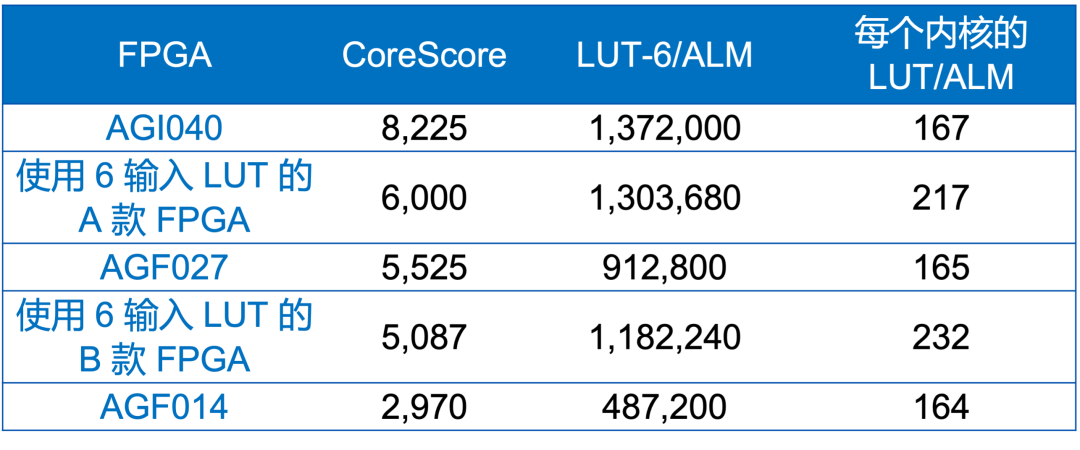

我们选择了A、B 两款使用基本 6 输入 LUT 和提供可选 5 输入 LUT 输出的 FPGA 产品与使用上文所述的 8 输入 ALM 配置的 Agilex 7 设备进行了对比。

根据 CoreScore.store 的结果可见,每个内核需要超过 210 个基本可拆分 6 输入 LUT,而 Agilex ALM 使用的 8 输入配置只需要不到 170 个。

如果我们比较逻辑单元 (LE)/系统逻辑单元 (SLC) 的用量,情况则会不同。所有设备都需要约 490 LE/SLC +/-5%。这并非偶然,而是因为这些 FPGA 产品均针对其逻辑使用了比例因子,以便更准确地反映其逻辑容量。

这些数据表明,逻辑单元和系统逻辑单元是衡量FPGA容量的有效指标。数据还显示,与传统的 6 输入结构相比,尽管查找表位数相同,Agilex FPGA 中使用的 8 输入 ALM 能够以更少的实例实现更多的逻辑。

这表明,6 输入结构浪费了更多的位数,因此需要更多的实例才能实现相同的功能。这些额外的实例将在芯片上占用更多面积,并在系统中增加功耗,这是您在为新设计选择 FPGA 时需要考虑的因素。Agilex ALM 还可支持特定的 7 输入和 8 输入功能,在 6 输入 LUT 配置中则需要两层逻辑来实现这种功能,这不但会消耗额外的 LUT,还会造成严重的时序损失。

FPGA 设备非常复杂,针对您的应用找到合适的设备并非易事。逻辑单元和系统逻辑单元等指标非常有参考价值,但也需要考虑设备附带的其他功能和工具,以及所采用的逻辑结构的底层架构。

ALM 是 Agilex FPGA 的基本构建模块,旨在以更少的资源实现更多的功能,从而实现更好的系统优化。本文提供了一些其他资源的链接,以便您参考。此后,如您需寻找合适的 FPGA,请务必查看 CoreScore。

-

FPGA

+关注

关注

1646文章

22091浏览量

620399 -

英特尔

+关注

关注

61文章

10210浏览量

175369 -

复用器

+关注

关注

1文章

779浏览量

29153 -

LUT

+关注

关注

0文章

50浏览量

12881

原文标题:解密逻辑单元与 CoreScore 得分的关系

文章出处:【微信号:英特尔FPGA,微信公众号:英特尔FPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Cyclone IV 器件的逻辑单元和逻辑阵列模块

如何在LUT和逻辑元件之间以及逻辑元件和逻辑单元之间进行交换

请问“逻辑单元”的意思是什么?

是否可以使用逻辑单元的verilog代码?

数字逻辑功能单元

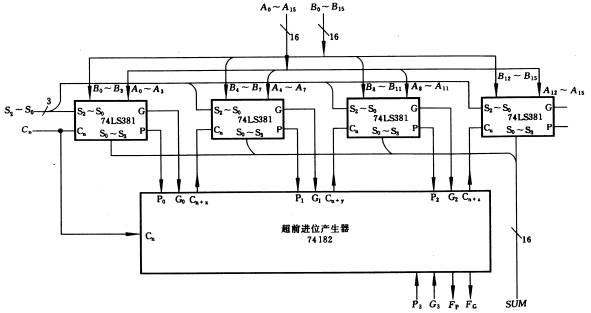

多功能算术/逻辑运算单元(ALU) ,什么是多功能算术/逻辑

基于单元相邻关系的重构区域构造方法

可配置逻辑单元(CLC)

解密逻辑单元与CoreScore得分的关系

解密逻辑单元与CoreScore得分的关系

评论