近日,新思科技(Synopsys)宣布了一项重大的技术突破,成功推出了1.6纳米背面电源布线项目。这一技术将成为未来万亿晶体管芯片制造过程中的关键所在。

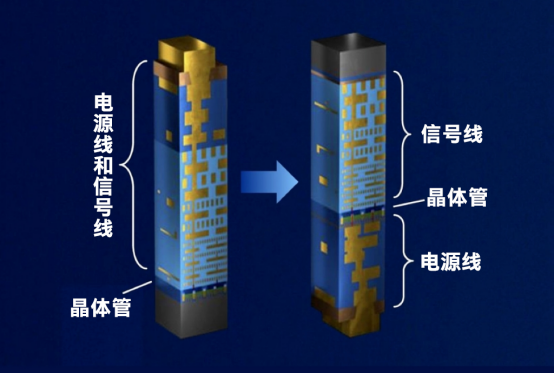

据了解,新思科技与台积电正在携手合作,共同开发适用于台积电A16 1.6纳米工艺的背面布线功能。这项技术的核心在于解决万亿晶体管设计中所面临的电源分配和信号布线问题。随着芯片集成度的不断提高,传统的布线方式已经难以满足日益复杂的设计需求,而1.6纳米背面布线技术的出现,无疑为这一难题提供了全新的解决方案。

为了确保设计团队能够高效地进行物理验证,并顺利过渡到台积电N2 2纳米技术,新思科技还提供了互操作工艺设计工具包(iPDK)以及IC Validator物理验证运行集。这些工具将帮助设计团队应对日益复杂的物理验证规则,从而提高设计效率和质量。

在万亿晶体管多芯片设计中,功率管理是一个至关重要的因素。新思科技的1.6纳米背面布线技术不仅优化了电源分配,还提高了信号传输的稳定性和效率,从而确保了芯片在高性能运行下的稳定性和可靠性。

随着技术的不断进步,新思科技与台积电的这一合作无疑将为全球芯片制造业带来全新的发展机遇。我们有理由相信,在不久的将来,万亿晶体管芯片将成为现实,并为人类社会带来更加便捷、高效的科技体验。

-

芯片设计

+关注

关注

15文章

1091浏览量

55726 -

晶体管

+关注

关注

77文章

10029浏览量

142179 -

新思科技

+关注

关注

5文章

872浏览量

51658

发布评论请先 登录

3D集成赛道加速!混合键合技术开启晶体管万亿时代

硅肖特基二极管芯片 skyworksinc

晶体管架构的演变过程

新思科技携手微软借助AI技术加速芯片设计

下一代高速芯片晶体管解制造问题解决了!

晶体管电路设计(下)

英特尔IEDM 2024大晒封装、晶体管、互连等领域技术突破

新思科技发布1.6纳米背面布线技术,助力万亿晶体管芯片发展

新思科技发布1.6纳米背面布线技术,助力万亿晶体管芯片发展

评论