共读好书

王磊,金祖伟,吴士娟,聂要要,钱晶晶,曹纯红

(中科芯集成电路有限公司)

摘要:

基于焊点预测仿真软件 Surface Evolver 对不同焊盘设计的球栅阵列( BGA ) 封装焊点的回流形态进行预测。模拟不同回流焊的冷却速率与焊盘设计对焊点的残余应力和基板翘曲的影响。根据正交试验和灰色关联分析法对结果进行分析优化。结果表明,优化后的焊点芯片侧的残余应力降低了 17.9%,PCB 侧的残余应力降低了 17.1%,其翘曲值为 68.867 μm。

1 引言

随着封装技术的发展,芯片封装逐渐向复杂、高密度的 2.5D、3D 封装发展。系统级封装(SiP)在传统封装的基础上,提升功能密度,缩短互连长度,进行系统重构,在一定程度上缓解了芯片集成的压力。然而随着集成度的增加,芯片的尺寸、引脚数量都在增加,设计难度提高,工艺成品良率降低,导致潜在的工艺制程风险增加 [1-2] 。球栅阵列(BGA)封装的焊点在保证SiP 互连电性能的前提下,也承担着机械可靠性的功能。由于焊点、基板、PCB 这一互连结构之间的热膨胀系数(CTE)存在差异,工艺过程中的热应力会导致BGA焊点产生较大的残余应力以及基板翘曲等问题 [3] 。

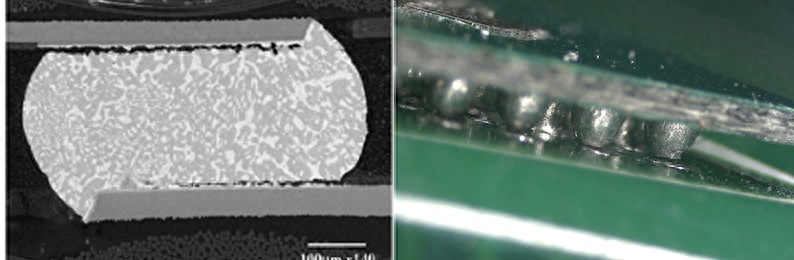

对此,胡少华 [4] 研究了在不同回流冷却速率下焊点结构对封装残余应力的影响。田文超等 [5] 研究了陶瓷封装阵列焊点的结构参数对焊点回流焊应力应变的影响。GE 和 NJOKU 等 [6-7] 研究了焊点高度对芯片长期可靠性的影响。张浩敏等 [8] 研究了残余应力对 BGA焊点可靠性的影响。以上研究结果表明,焊点高度、焊盘直径、回流冷却速率对焊点的残余应力均有显著影响,同时较大的残余应力容易导致器件的焊盘坑裂。

本文针对不同的焊盘设计参数,采用 SurfaceEvolver 软件对 BGA 焊点进行形态预测。同时以 40×40 面阵列 BGA 焊点的 SiP 封装为研究对象,分析其芯片侧、PCB 侧的焊盘设计与回流冷却速率对焊点回流残余应力以及基板翘曲的影响。用正交试验和灰色关联法进行优化设计,找出最优参数组合进行验证,为提高大尺寸阵列 SiP 封装的设计优化提供数据参考。

2 SiP 封装模型建立

2.1 BGA 焊点形态预测

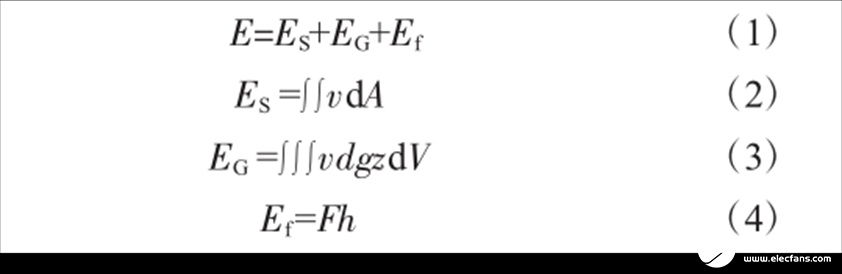

根据热力学基本定律,自然界中任何封闭系统的存在总符合能量最小原理。因此在回流稳态后,熔融的 BGA 焊点(液相)与对流热空气(气相)和上下基板焊盘(固相)组成的系统处于能量最小的状态。单个BGA 焊点的系统能量 E 是表面势能 E S 、焊点自身重力势能 E G 和外力作用势能 E f 之和,即

式中 v 为焊点表面张力,A 为焊点的自由表面积,d 为BGA 焊点密度,g 为重力加速度,z 为焊点高度坐标,V为焊点体积,F 为作用在 BGA 焊点上的压力,h 为焊点高度。

表面势能总和 I 以泛函数形态描述为:

式中 λ 是拉格朗日乘子,V 0 为焊点的初始体积。式(5)中被积函数满足欧拉-拉格朗日方程时,可得泛函极值,利用变分问题的数值解法可求解钎料的平衡形态 [9] 。

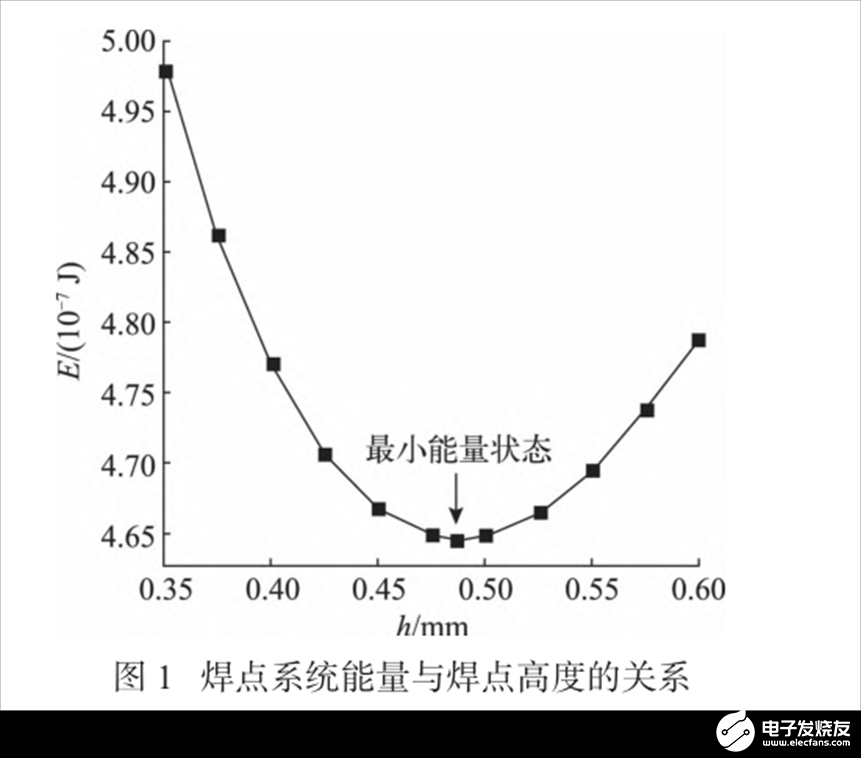

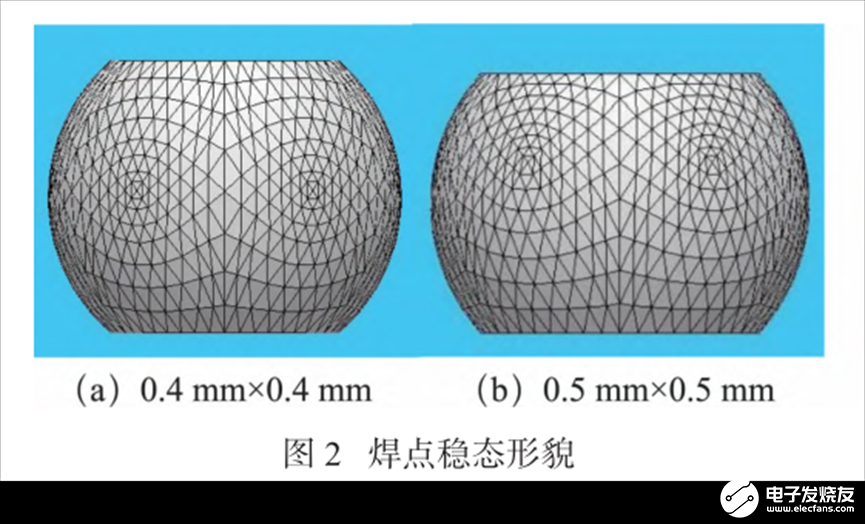

根据上述模型,采用 Surface Evolver 求解出焊点稳态形貌。本文采用 SAC305 无铅焊点材料,其密度为7.3 g/cm 3 。BGA 的焊点间距为 1 mm 时,植球直径为0.6mm,芯片侧与PCB侧的焊盘直径分别选择 0.4mm、0.45 mm、0.5 mm 和 0.55 mm。

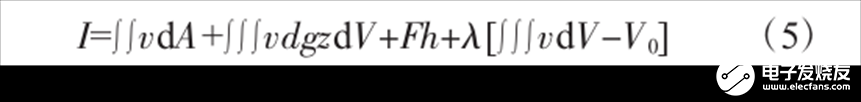

考虑到不同尺寸的焊盘在同一工艺下的锡量存在差异,最终形貌的焊点尺寸会不同。根据 IPC-7525A漏模板设计标准选择 BGA 钢网开孔比例以及锡膏厚度,避免选择较大数值(容易导致实际表面贴装过程中的焊接异常)。选择厚度为 0.13 mm 的钢网,开孔面积为 90%的 BGA 焊盘,树脂的质量分数为 50%的锡膏,计算出不同焊盘设计条件下的焊点体积。当焊点体积和焊盘尺寸固定时,不同高度下的焊点系统能量与焊点高度的关系如图 1 所示,其整体呈抛物线变化,选取不同参数组合下焊点系统能量曲线最低点时的平衡焊点高度 H,焊点形态的预测尺寸如表 1 所示。根据其尺寸参数拟合出的焊点稳态形貌如图 2 所示。

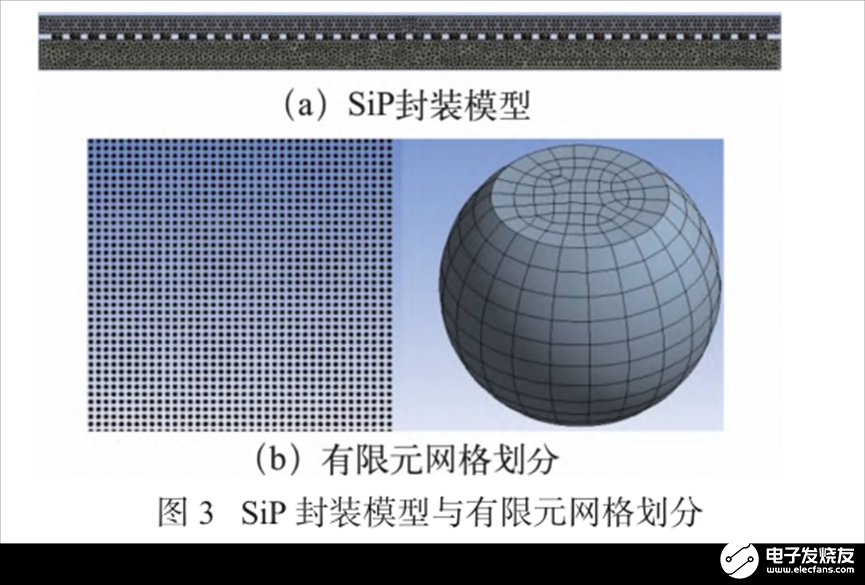

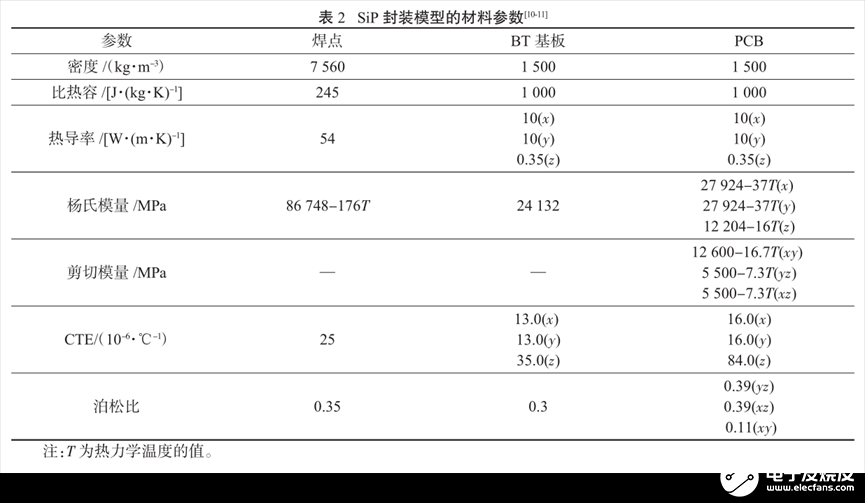

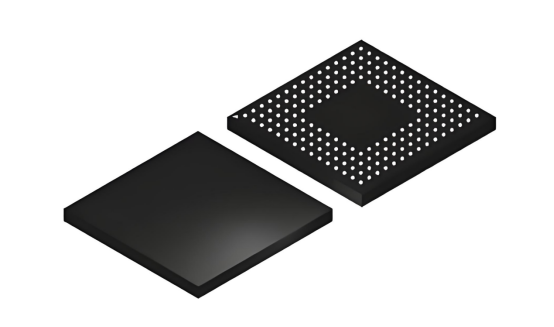

2.2 仿真模型

参考阵列为 40×40、pin 间距为 1 mm 的 SiP 芯片封装结构,芯片基板尺寸为 41 mm×41 mm×1 mm,建立有限元分析模型,将模型简化为 1/4 模型进行仿真计算,SiP 封装模型与有限元网格划分如图 3 所示。焊点采用无铅焊料,对局部焊点加密网格,采用 Anand

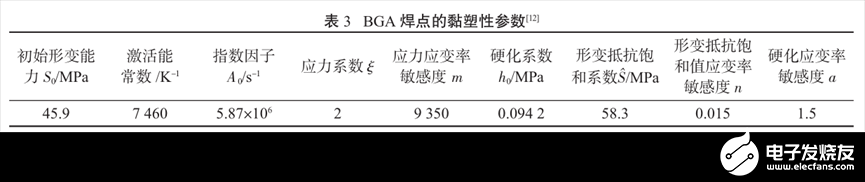

黏塑性网格单元,SiP 封装模型的材料参数如表 2 所示,其中 x、y、z 表示坐标轴,xy、yz、xz 表示 2 个坐标轴形成的面 [10-11] 。BGA 焊点的黏塑性参数如表 3 所示 [12] 。

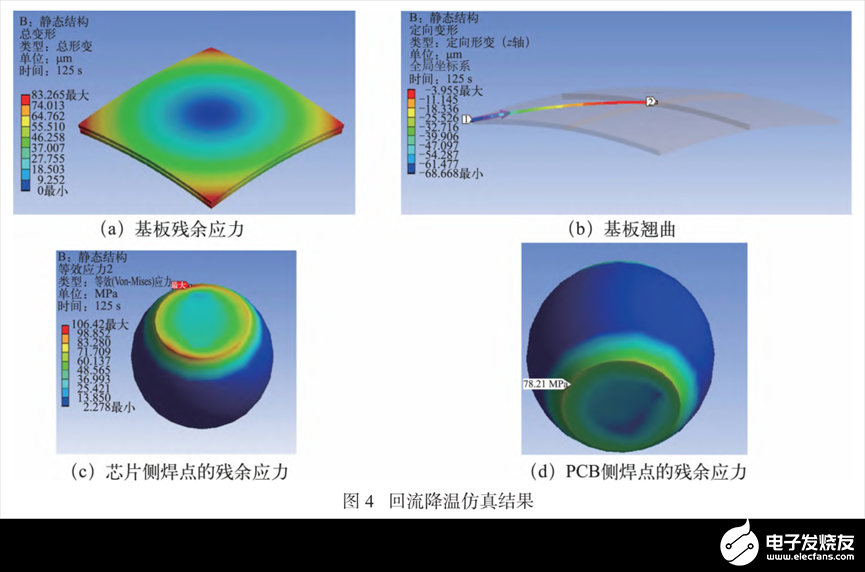

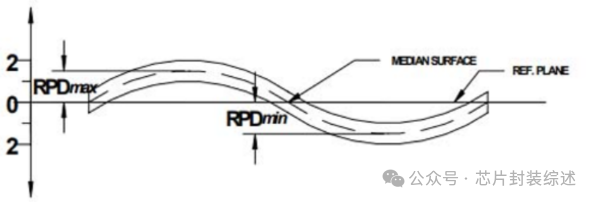

3 残余应力与翘曲仿真

在 ANSYS workbench 仿真模块中建立回流焊仿真分析模型。考虑到在回流冷却过程中,焊点从液态逐渐固化,其应力会随温度变化。为了参考不同参数组合条件下残余应力和翘曲的变化,以 150 ℃作为零应力参考温度,设置环境温度为 25 ℃。芯片侧焊盘直径为 0.4 mm,PCB 侧焊盘直径为 0.4 mm,在冷却速率为 1 ℃·s -1 的条件下,SiP 基板的形变分布与 z 轴对角线的翘曲值如图 4(a)(b)所示。由于 PCB 在 z 轴方向的 CTE 大于 BT 基板,在回流冷却过程中,PCB 的收缩比例较大,产生的应力差使芯片基板向 PCB 侧弯曲变形,最终呈现出哭脸型(芯片边缘低于中心)翘曲,其翘曲值为 68.668 μm。此时四角位置的形变量最大。

芯片侧焊点的残余应力为 106.42 MPa,如图 4(c)所示。PCB 侧焊点的残余应力为 78.21 MPa,如图 4(d) 所示。芯片侧焊点的残余应力大于 PCB 侧焊点。

4 正交试验分析

4.1 确立变量因素与优化目标

将 BGA 焊点在回流过程中的残余应力以及翘曲值作为优化目标,选取BGA焊点芯片侧的焊盘直径D 1 、PCB 侧的焊盘直径 D 2 以及冷却速率 S 作为设计变量。

4.2 正交试验设计

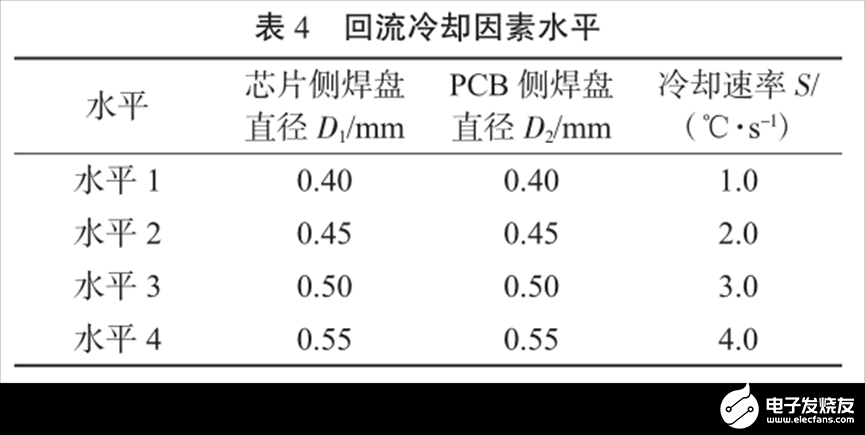

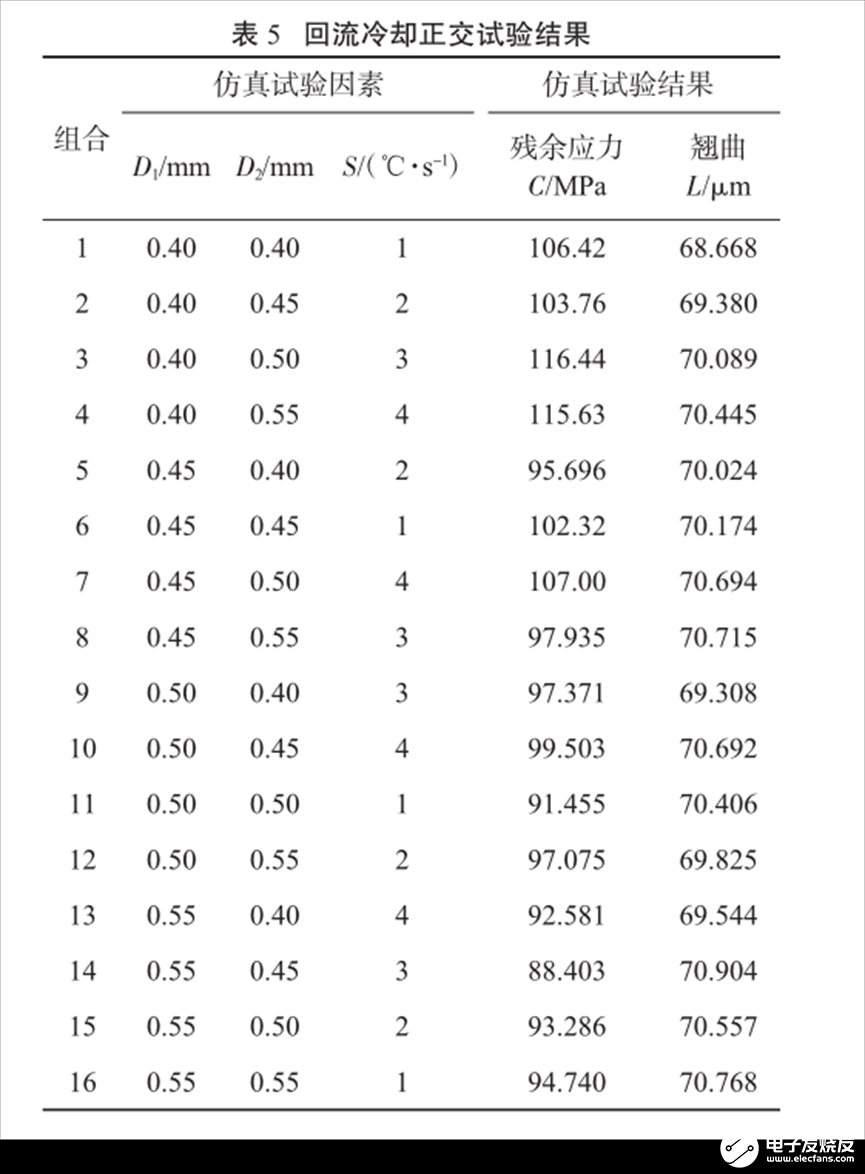

为了得出回流冷却过程中 BGA 焊点残余应力与翘曲值的最优组合,需要进行大量的组合试验。为了减少试验的工作量,同时得到各影响因子的影响程度,采用正交试验法来优化分析方案。每个因素选取 4个水平,利用芯片侧焊盘直径和 PCB 侧焊盘直径的组合在表 1 里找到其焊点的体积和高度,据此设计出回流冷却因素水平(见表 4)。

采用 L 16 (4 3 )正交表,再结合表 1 的焊点形态预测尺寸建立仿真模型,计算出回流冷却过程中焊点的残余应力以及基板翘曲值。得到的 16 组回流冷却正交试验结果如表 5 所示。

5 残余应力与翘曲的灰色关联分析

由于 L 16 (4 3 )正交表的试验设计只确定了 16 组已知的白色系统组合,仍然有 48 组黑色系统组合未知,这就构成了已知和未知的灰色系统。对于双优化目标的水平组合,常规的试验设计优化分析无法满足,因此引入灰色关联分析法。2 个目标随不同因素水平变化的关联性量度称为关联度。当 2 个因素的变化区域一致时关联度高,反之则低,因此灰色关联分析方法会根据不同因素水平之间的灰色关联度来衡量其数值关系 [13] 。

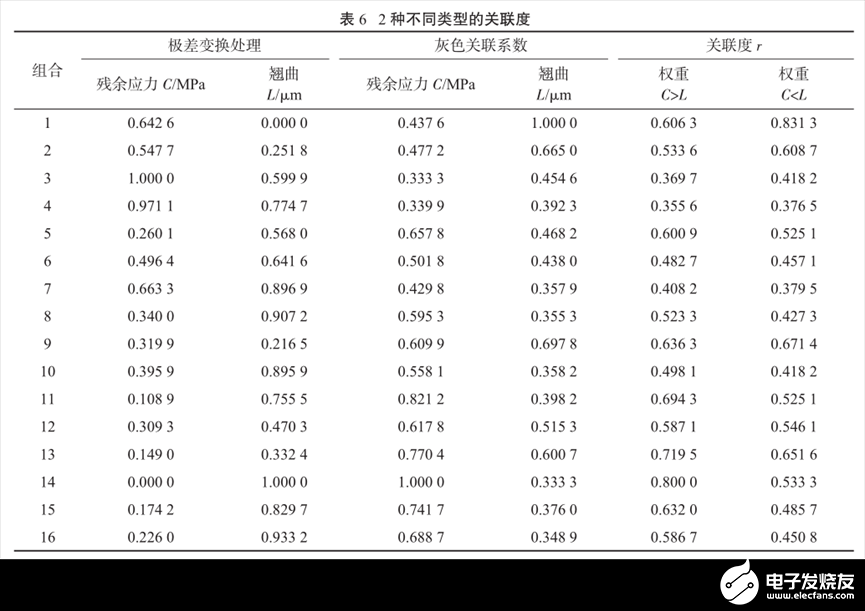

5.1 残余应力与翘曲的灰色关联系数

由于系统中数值的物理意义不同,为防止小数值序列被大数值掩盖,统一对序列进行规范化处理。常见的处理方法有均值化法、初值化法和极差变换法,此处采用极差变换法对残余应力和翘曲值进行规范化处理。参考序列和规范化序列分辨系数取一般值 0.5进行灰色关联系数计算。灰色关联系数越大,表明残余应力与翘曲值贴合程度越大 [9] 。

5.2 残余应力与翘曲最优解的确定

在回流冷却过程中,优化 BGA 焊点的残余应力与 BT 基板的翘曲值有助于提高芯片的可靠性,其中焊点的残余应力值与基板的翘曲值越小越好,但 2 个目标优化的权重比是个主观因子,长期可靠性条件下的残余应力权重大于翘曲值,工艺管控中的翘曲值权重大于残余应力,因此 2 种不同类型的关联度如表 6所示。

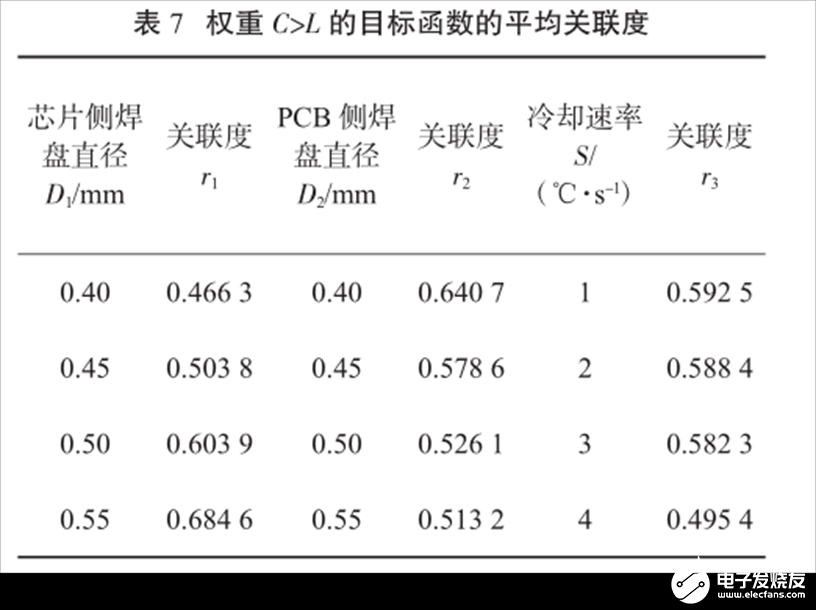

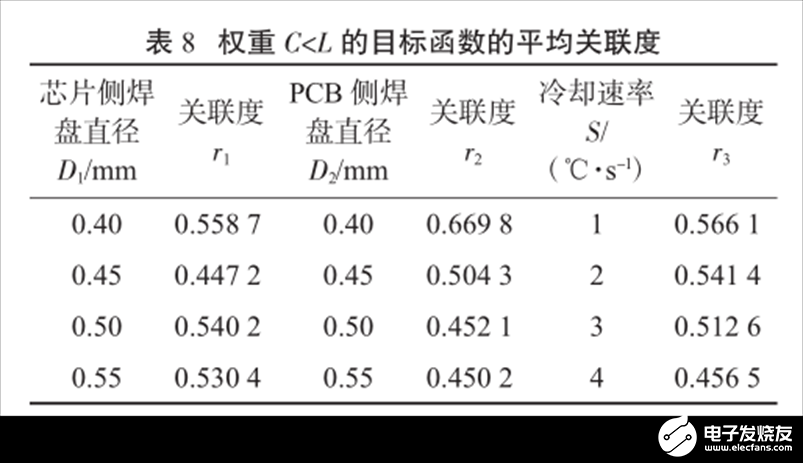

确定 BGA 最优参数组合前需计算出不同参数水平的平均关联度,灰色关联度的定义表明,平均关联度越大越接近最优解,通过计算得出目标函数的平均关联度 [9] 。其中残余应力权重大于翘曲值的目标函数的平均关联度如表 7 所示,其最优参数组合为D 14 D 21 S 1 ,即芯片侧焊盘直径 D 1 选第 4 组数据 0.55 mm,PCB 侧焊盘直径 D 2 选第 1 组数据 0.4 mm,冷却速率 S选第 1 组数据 1 ℃·s -1 。翘曲值权重大于残余应力的平均关联度如表 8 所示,可以得出最优参数组合为D 11 D 21 S 1 ,即芯片侧焊盘直径 D 1 为 0.4 mm,PCB 侧焊盘直径 D 2 为 0.4 mm,冷却速率 S 为1 ℃·s -1 。

5.3 焊点残余应力与翘曲的最优参数组合仿真验证

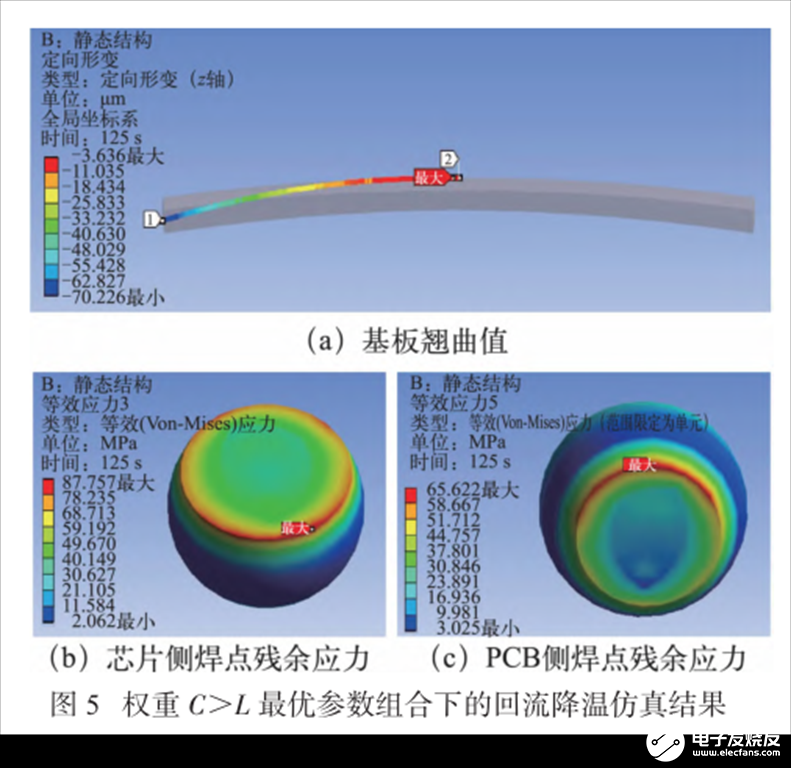

已经分析得出翘曲值权重大于残余应力的最优参数组合为 D 11 D 21 S 1 (仿真结果见图 4),残余应力权重大于翘曲值的最优参数组合为 D 14 D 21 S 1 ,为了验证灰色关联分析的准确性,采用 D 14 D 21 S 1 的参数组合进行仿真验证。参数组合 D 14 D 21 S 1 的仿真结果如图 5 所示,其芯片侧残余应力为 87.757 MPa,PCB 侧残余应力为65.622 MPa,基板翘曲值为 70.226 μm。

5.4 焊点残余应力与翘曲优化综合仿真验证

残余应力权重大于翘曲值时的参数组合 D 14 D 21 S 1有一定的降低残余应力的效果,但同时翘曲值会增加。同理参数组合 D 11 D 21 S 1 的翘曲值权重大于残余应力,会导致其残余应力增加,翘曲值降低。综合 2 种组合结果,修改芯片侧和 PCB 侧的焊盘尺寸有助于优化残余应力和翘曲值。

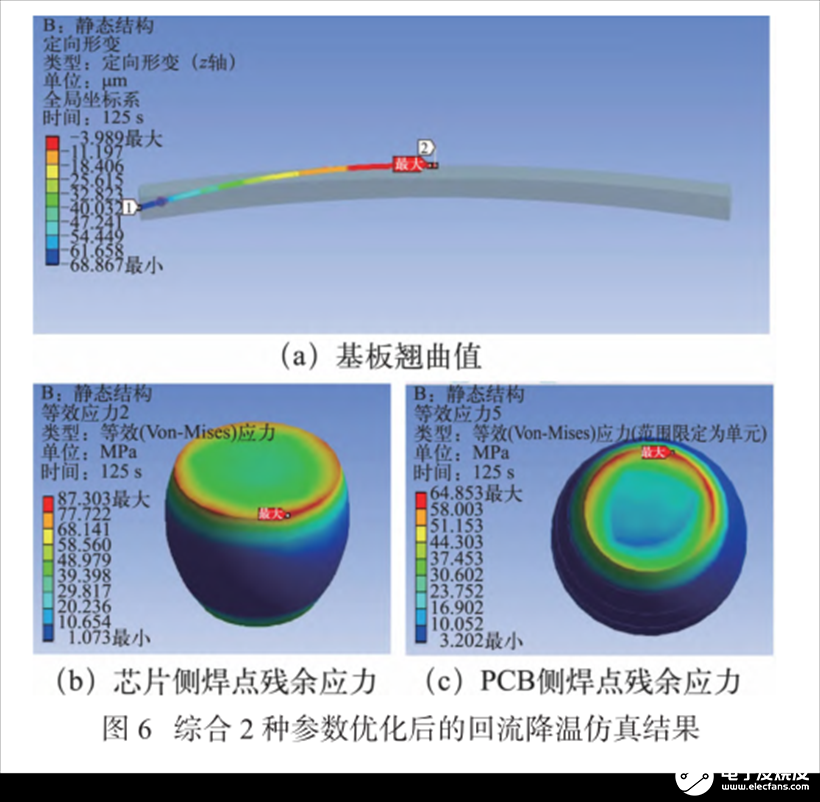

若同时优化 2 种参数,可将其组合,以 D 11 D 21 S 1 组合为主降低翘曲值,四角位置残余应力较大的焊点均采用非功能焊点,采用 D 14 D 21 S 1 组合的焊点尺寸参数。综合 2 种参数优化后的回流降温仿真结果如图 6 所示,其翘曲值为 68.867 μm,芯片侧残余应力为87.303 MPa,比初始值下降了 17.9%,PCB 侧残余应力为 64.853 MPa,比初始值下降了 17.1%。相比 D 11 D 21 S 1组合,其翘曲值比初始值 68.668 μm 略大,但残余应力明显降低,该组合综合考虑了翘曲值与残余应力,实现了设计优化。

6 结论

本文通过仿真软件 Surface Evolver 对不同焊盘设计的 BGA 焊点的回流形态进行预测,研究了焊盘设计与冷却速率对焊点的残余应力和基板翘曲值的影响,总结出以下结论:

(1)可通过灰度分析法分析回流降温速率,回流降温速率的增加对基板翘曲和焊点残余应力有一定的优化作用,可以指导工艺进行参数调整;

(2)调整芯片和 PCB 的焊盘设计可以优化基板翘曲和焊点残余应力,可以通过设计降低工艺中的翘曲不良,减少残余应力引起的焊点早期失效;

(3)不同产品对于翘曲和残余应力的要求不同,可以有针对性地进行芯片侧和 PCB 侧的焊盘设计来降低翘曲和残余应力或者对两者进行综合优化。

审核编辑 黄宇

-

芯片

+关注

关注

460文章

52749浏览量

444503 -

SiP

+关注

关注

5文章

529浏览量

106705 -

封装

+关注

关注

128文章

8852浏览量

145969 -

焊点

+关注

关注

0文章

138浏览量

13124

发布评论请先 登录

印刷电路板(PCB)翘曲问题及其检测技术

PCB翘曲不用愁!| 鑫金晖压板烘箱专治电路板卷翘异常,高效节能热压整平

电路板专用便携式应力测试仪DL-1000-32C

PCB 裸板烘干除潮要求及形变(平面度)如何控制?

一种低翘曲扇出重构方案

芯片封装中的焊点图案设计

SIP封装技术:引领电子封装新革命!

BGA封装器件焊点抗剪强度测试全解析,应用推拉力机

PCB板弯板翘的原因及改善措施

机械应力和热应力下的BGA焊点可靠性

电子制造中的翘曲难题:PCB板整平方法综述

SiP 封装的焊点形态对残余应力与翘曲的影响

SiP 封装的焊点形态对残余应力与翘曲的影响

评论