很多同学听说过“短线”不用端接电阻匹配阻抗,或者是短PCB走线不用控阻抗,为什么短线不用控阻抗?多短的线才算短线呢?

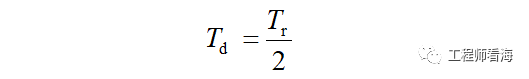

先抛出临界长度的概念,由于信号传输的时间和长度成正比,因此在信号完整性中常用时间表示长度,临界长度就是信号上升沿时间的一半,即

临界长度与反射是什么关系呢?

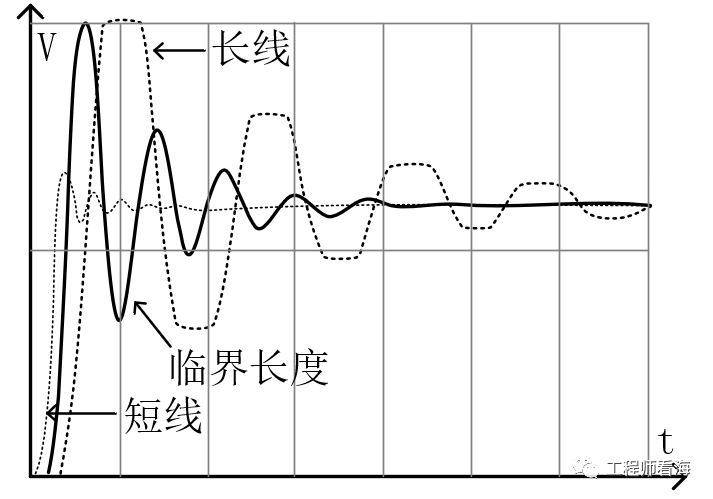

比如一个信号的上升沿是100ps,那么临界长度是50ps,我们分别看看下图中走线长度小于临界长度、等于临界长度和大于临界长度三种长度的走线情况下负载开路状态下反射波形,一个最明显的特征是临界长度时,反射波形刚好达到最大值,走线小于临界长度时反射比较小,达不到最大值;走线大于临界长度时达到最大值并持续了下来。

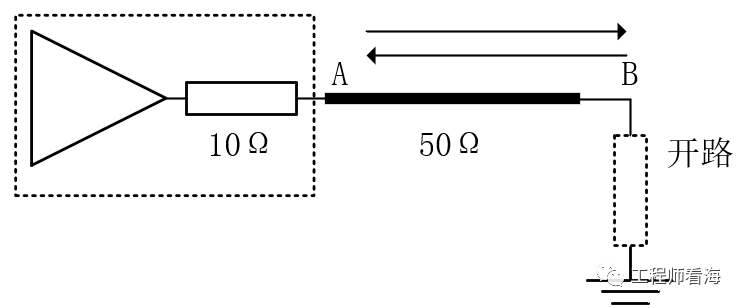

我们可以简单点理解这个现象,如果传输线很短,而信号上升沿又很长,信号从A点出来后经传输线到的B点并发生正反射,反射回A的信号又发生负反射向B端传播,与此同时缓慢的上升沿也向B传播,B点的电压还没有来得及到达最大值,就被反射回B的负电压拉低了。因此,走线很短时,信号反射达不到最大值,宏观来看就是B端的信号反射现象很小。

而临界长度就是反射信号刚刚达到最大值的分水岭,当传输线长度小于临界长度时,振铃达不到最大值,因此哪怕是短线也是存在反射的,只是振铃小,走线越短振铃越小。

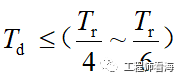

那么多长的短线才算短呢?其实这个没有统一的要求,得看系统能容忍多大的噪声,工程中一般使用

作为参考,认为小于该长度的走线可以放宽对端接电阻控制阻抗的要求,当然具体问题还要具体分析。

—— The End——

审核编辑 :李倩

-

pcb

+关注

关注

4372文章

23550浏览量

411931 -

阻抗

+关注

关注

17文章

975浏览量

47660 -

信号完整性

+关注

关注

68文章

1459浏览量

96978

原文标题:信号完整性之:多长的PCB走线不用控阻抗?

文章出处:【微信号:玩转单片机与嵌入式,微信公众号:玩转单片机与嵌入式】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

别蒙我,PCB板上这几对高速走线怎么看我都觉得一样!

揭秘PCB阻抗控制:如何影响你的电子设备性能?

PCB制板厂加工问题很大啊,高速PCB传输线阻抗一直往上跑

PCB Layout中的三种走线策略

PCB走线,盲目拉线,拉了也是白拉!

揭秘PCB走线设计黑洞:仿真视角下挑战,工程师与PCB设计师必看!

从驱动端到串联电阻之间的这一段走线应该走成多少阻抗呢?

PCB走线与电磁兼容:如何巧妙平衡与协同

技术资讯 I 如何使用 Allegro X PCB Editor 优化RF布线和阻抗

多长的PCB走线不用控阻抗?

多长的PCB走线不用控阻抗?

评论