从PC时代走向移动与AI时代,芯片的架构也从以CPU为中心走向了以数据为中心。AI带来的考验不仅包括芯片算力,也包括内存带宽。纵使DDR和GDDR速率较高,在不少AI算法和神经网络上,却屡屡遇上内存带宽上的限制,主打大带宽的HBM也就顺势成了数据中心、HPC等高性能芯片中首选的DRAM方案。

当下JEDEC还没有给出HBM3标准的最终定稿,但参与了标准制定工作的IP厂商们已经纷纷做好了准备工作。不久前,Rambus就率先公布了支持HBM3的内存子系统,近日,新思科技也公布了业界首个完整HBM3 IP与验证方案。

IP厂商先行

早在今年初,SK海力士就对HBM3内存产品的性能给出了前瞻,称其带宽大于665 GB/s,I/O速度大于5.2Gbps,不过这只是一个过渡的性能。同在今年,IP厂商公布的数据进一步拉高了上限。比如Rambus公布HBM3内存子系统中,I/O速度高达8.4Gbps,内存带宽最高可至1.075TB/s。

今年6月,台湾创意电子发布了基于台积电CoWoS技术的AI/HPC/网络平台,搭载了的HBM3控制器与PHY IP,I/O速度最高达到7.2Gbps。创意电子还在申请一项中介层布线专利,支持任何角度的锯齿形布线,可将HBM3 IP拆分至两个SoC上使用。

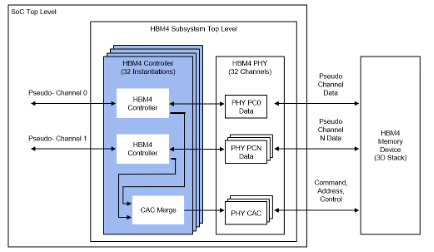

新思科技公布的完整HBM3 IP方案为2.5D多晶片封装系统提供了控制器、PHY和验证IP,称设计者可在SoC中用到低功耗更大带宽的内存。新思的DesignWare HBM3控制器与PHY IP基于经芯片验证过的HBM2E IP打造,而HBM3 PHY IP基于5nm制程打造,每个引脚的速率可达7200 Mbps,内存带宽最高可提升至921GB/s。

封装加成

以上还只是单层HBM的数据,通过2.5D封装堆叠2层或者4层后,内存带宽也将成倍突破。以英伟达的A100加速器为例,英伟达首发的80GB版本采用了4层HBM2达到了1.6TB/s的带宽,之后推出了5层HBM2E的版本,进一步将带宽提高至2TB/s。而这样的带宽表现,只需2层HBM3即可实现,四五层的配置更是远超市面上已有的内存规格。

此外,逻辑+HBM的方法已经不新鲜了,已经有不少GPU和服务器芯片都采用了类似的设计。然而随着晶圆厂不断在2.5D封装技术上发力,单个芯片上HBM的数量也在增加。比如上文中提到的台积电CoWoS技术,可在SoC芯片中集成4个以上的HBM,英伟达的P100就集成了4个HBM2,而NEC的Sx-Aurora向量处理器则集成了6个HBM2。

三星也在开发下一代的I-Cube 2.5D封装技术,除了支持集成4到6个HBM以外,也在开发两个逻辑晶片+8个HBM的I-Cube 8方案。类似的2.5D封装技术还有英特尔的EMIB,但不过HBM主要用于其Agilex FPGA。

结语

目前美光、三星、SK海力士等内存厂商都已经在纷纷跟进这一新的DRAM标准,SoC设计厂商Socionext与新思合作,在其多晶片的设计中引入HBM3,除了必定支持的x86架构外,Arm的Neoverse N2平台也已计划了对HBM3的支持,SiFive的RISC-V SoC也加入了HBM3 IP。但即便JEDEC没有“卡壳”,在年末的关头发布了HBM3正式标准,我们也可能要等到2022年下半年才能见到HBM3相关产品的面世。

大家都已经在不少高性能芯片上见到了HBM2/2E的身影,尤其是数据中心应用,比如英伟达的Tesla P100/V100、AMD的Radeon Instinct MI25、英特尔的Nervana神经网络处理器以及谷歌的TPU v2等等。

消费级应用却似乎正在与HBM渐行渐远,过去还有AMD的Radeon RxVega64/Vega 56以及英特尔的KabyLake-G这样利用了HBM的图形产品,再高一级也有英伟达的Quaddro GP100/GV100和AMD的Radeon Pro WX这样的专业绘图GPU。

如今这些产品都用回了GDDR DRAM,毕竟消费级应用目前尚未出现带宽瓶颈,速率和成本反倒才是芯片制造商最看重的,而HBM3在优点上提及了更大带宽更高的功效,却并没有降低成本。

当下JEDEC还没有给出HBM3标准的最终定稿,但参与了标准制定工作的IP厂商们已经纷纷做好了准备工作。不久前,Rambus就率先公布了支持HBM3的内存子系统,近日,新思科技也公布了业界首个完整HBM3 IP与验证方案。

IP厂商先行

早在今年初,SK海力士就对HBM3内存产品的性能给出了前瞻,称其带宽大于665 GB/s,I/O速度大于5.2Gbps,不过这只是一个过渡的性能。同在今年,IP厂商公布的数据进一步拉高了上限。比如Rambus公布HBM3内存子系统中,I/O速度高达8.4Gbps,内存带宽最高可至1.075TB/s。

今年6月,台湾创意电子发布了基于台积电CoWoS技术的AI/HPC/网络平台,搭载了的HBM3控制器与PHY IP,I/O速度最高达到7.2Gbps。创意电子还在申请一项中介层布线专利,支持任何角度的锯齿形布线,可将HBM3 IP拆分至两个SoC上使用。

新思科技公布的完整HBM3 IP方案为2.5D多晶片封装系统提供了控制器、PHY和验证IP,称设计者可在SoC中用到低功耗更大带宽的内存。新思的DesignWare HBM3控制器与PHY IP基于经芯片验证过的HBM2E IP打造,而HBM3 PHY IP基于5nm制程打造,每个引脚的速率可达7200 Mbps,内存带宽最高可提升至921GB/s。

封装加成

以上还只是单层HBM的数据,通过2.5D封装堆叠2层或者4层后,内存带宽也将成倍突破。以英伟达的A100加速器为例,英伟达首发的80GB版本采用了4层HBM2达到了1.6TB/s的带宽,之后推出了5层HBM2E的版本,进一步将带宽提高至2TB/s。而这样的带宽表现,只需2层HBM3即可实现,四五层的配置更是远超市面上已有的内存规格。

此外,逻辑+HBM的方法已经不新鲜了,已经有不少GPU和服务器芯片都采用了类似的设计。然而随着晶圆厂不断在2.5D封装技术上发力,单个芯片上HBM的数量也在增加。比如上文中提到的台积电CoWoS技术,可在SoC芯片中集成4个以上的HBM,英伟达的P100就集成了4个HBM2,而NEC的Sx-Aurora向量处理器则集成了6个HBM2。

三星也在开发下一代的I-Cube 2.5D封装技术,除了支持集成4到6个HBM以外,也在开发两个逻辑晶片+8个HBM的I-Cube 8方案。类似的2.5D封装技术还有英特尔的EMIB,但不过HBM主要用于其Agilex FPGA。

结语

目前美光、三星、SK海力士等内存厂商都已经在纷纷跟进这一新的DRAM标准,SoC设计厂商Socionext与新思合作,在其多晶片的设计中引入HBM3,除了必定支持的x86架构外,Arm的Neoverse N2平台也已计划了对HBM3的支持,SiFive的RISC-V SoC也加入了HBM3 IP。但即便JEDEC没有“卡壳”,在年末的关头发布了HBM3正式标准,我们也可能要等到2022年下半年才能见到HBM3相关产品的面世。

大家都已经在不少高性能芯片上见到了HBM2/2E的身影,尤其是数据中心应用,比如英伟达的Tesla P100/V100、AMD的Radeon Instinct MI25、英特尔的Nervana神经网络处理器以及谷歌的TPU v2等等。

消费级应用却似乎正在与HBM渐行渐远,过去还有AMD的Radeon RxVega64/Vega 56以及英特尔的KabyLake-G这样利用了HBM的图形产品,再高一级也有英伟达的Quaddro GP100/GV100和AMD的Radeon Pro WX这样的专业绘图GPU。

如今这些产品都用回了GDDR DRAM,毕竟消费级应用目前尚未出现带宽瓶颈,速率和成本反倒才是芯片制造商最看重的,而HBM3在优点上提及了更大带宽更高的功效,却并没有降低成本。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

内存

+关注

关注

8文章

3133浏览量

75450 -

HBM

+关注

关注

2文章

416浏览量

15315 -

HBM3

+关注

关注

0文章

74浏览量

349

发布评论请先 登录

相关推荐

热点推荐

风景独好?12层HBM3E量产,16层HBM3E在研,产业链涌动

电子发烧友网报道(文/黄晶晶)在早前的报道中,对于HBM产能是否即将过剩,业界有不同的声音,但丝毫未影响存储芯片厂商对HBM产品升级的步伐。 ? 三大厂商12 层HBM3E 进展 ? 9月26日SK

专网卡提速秘籍:APN优化全揭秘

的专网卡瞬间“满血复活”。 开发板到手,咔咔开箱组装,刷软件跑demo,一番行云流水,看似万事俱备,却偏偏无法联网?你是不是也曾碰到过类似情况。 ? 此时,建议先从以下几点排查检测:? 确认SIM卡是否欠费; 天线是否连接正常; 使用的卡是否是专网卡,

揭秘专网卡APN密码:从参数到实战的终极攻略

落地的终极联网方案。 开发板到手,咔咔开箱组装,刷软件跑demo,一番行云流水,看似万事俱备,却偏偏无法联网?你是不是也曾碰到过类似情况。 ? 此时,建议先从以下几点排查检测:? 确认SIM卡是否欠费; 天线是否连接正常; 使用的卡

三星在4nm逻辑芯片上实现40%以上的测试良率

三星电子在 HBM3 时期遭遇了重大挫折,将 70% 的 HBM 内存市场份额拱手送给主要竞争对手 SK 海力士,更是近年来首度让出了第一大 DRAM 原厂的宝座。这迫使三星在 HBM4 上采用

发表于 04-18 10:52

三星与英伟达高层会晤,商讨HBM3E供应

其高带宽存储器HBM3E产品中的初始缺陷问题,并就三星第五代HBM3E产品向英伟达供应的相关事宜进行了深入讨论。 此次高层会晤引发了外界的广泛关注。据推测,三星8层HBM3E产品的质量认证工作已接近尾声,这标志着三星即将正式迈入

三星电子将供应改良版HBM3E芯片

三星电子在近期举行的业绩电话会议中,透露了其高带宽内存(HBM)的最新发展动态。据悉,该公司的第五代HBM3E产品已在2024年第三季度实现大规模生产和销售,并在第四季度成功向多家GPU厂商及数据中心供货。与上一代HBM3相比,

AWG电缆线规的标准定义

AWG(American wire gauge)电缆线规的标准定义如下: 一、基本概念 AWG是美国线规的简称,是一种区分导线直径的标准,也被称为Brown & Sharpe线规。这种标准化线规系统

蔚来与万事达卡签署战略合作协议

近日,蔚来与万事达卡在上海签署战略合作协议。蔚来联合创始人、总裁秦力洪,万事达卡全球执行副总裁兼大中华区总裁常青出席签约仪式。蔚来商业资源管理副总裁胡崖音与万事达卡中国区零售和商业总经理张昊代表双方签约。

蔚来与万事达卡达成战略合作

近日,蔚来与全球知名支付品牌万事达卡在上海正式签署了战略合作协议。此次合作标志着双方在用户增值服务、支付创新、数据服务与咨询、联合营销以及ESG(环境、社会和公司治理)等多个领域将展开全方位、多层次

芯片的HBM静电都有哪些测试标准,各标准之间有没有差异

知道,芯片的静电测试标准主要有HBM,MM和CDM,通过前面文章,我们知道了如下两点信息。 1.上面三种测试标准,MM现在只是可选项,不做强制要求,参考文章: 芯片规格书里的静电指标为什么很少看到机器模型(MM)了 2.芯片的静

SK海力士发布HBM3e 16hi产品

在近日举办的SK AI Summit 2024活动中,SK hynix(SK海力士)透露了一项令人瞩目的新产品计划。据悉,该公司正在积极开发HBM3e 16hi产品,这款产品的每颗HBM芯片容量高达48GB,将为用户带来前所未有的存储体验。

Rambus宣布推出业界首款HBM4控制器IP,加速下一代AI工作负载

基于一百多项HBM成功设计案例,确保芯片一次流片成功 在低延迟下提供超过HBM3两倍的吞吐量,满足生成式AI和高性能计算(HPC)工作负载的需求 扩展了业界领先的高性能内存解决方案的半导体IP

发表于 11-13 15:36

?853次阅读

SK海力士推出48GB 16层HBM3E产品

近日在一次科技展览上,SK海力士惊艳亮相,展出了全球首款48GB 16层HBM3E(High Bandwidth Memory 3E)产品。这一突破性产品不仅展示了SK海力士在高端存储技术领域

三星或将HBM产能目标下调至每月17万颗

据业内人士透露,三星电子已对其2025年底的高带宽内存(HBM)最大产能目标进行了调整,下调幅度超过10%,从原先计划的每月20万颗减至17万颗。这一变动主要归因于向主要客户的量产供应遭遇延迟,导致三星对其尖端的

万能断路器欠压线圈的工作原理是什么

万能断路器欠压线圈的工作原理主要基于电磁感应和磁性材料的特性。以下是对其工作原理的解释: 一、基本组成 万能断路器中的欠压线圈,也称为欠电压

HBM3万事俱备,只欠标准定稿

HBM3万事俱备,只欠标准定稿

评论