摘 要: 传统的8PSK频偏估计方法通常需要上百个符号完成,其优点在于能够实现较大的载波频偏补偿,但是同步时间较长,不适用于短时突发通信条件下的快速载波频偏估计。特别是在低信噪比下,更是很难达到快速锁定的目的。基于在低信噪比条件下,数据包长度有限的短时突发通信,提出了一种8PSK快速载波同步的方法,并在FPGA上得到实现。经验证,该方法实现简洁有效,硬件开销小,同步时间短。

0 引言

8PSK在卫星通信、数据链电台等领域有广泛应用。而未预差分编码的8PSK只适合相干解调,接收机通常需要对发送载波的初始相位以及收发端之间的载波频偏进行估计,然后通过跟踪环路将残余频偏补偿回去,从而达到正确解调的目的。传统方法的初相和频偏估计以及跟踪过程往往通过上百个符号完成,其优点在于能够对较大的载波频偏进行补偿,但是跟踪时间长,不适用于短包突发通信,而且在通常情况下硬件开销较大[1-2]。

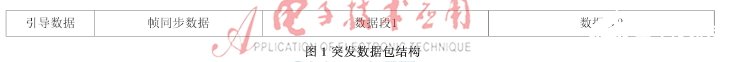

突发数据包结构中(如图1所示),每包中用于信号捕获以及载波初值估计与跟踪的引导数据长度一般只有几十个符号。每个突发数据包都需要完成载波同步与跟踪,且由于引导数据很短,需要快速完成同步。通过实际仿真发现,在低信噪比下快速同步极易出现载波失锁或锁相环带入过调量而造成相位误差,从而人为地增加了信号的相位噪声。因此,在短包突发通信中,较难解决快速同步与信号跟踪稳定的矛盾。

本文在数据包长度有限的突发通信[3]模式下,为了实现信号的快速捕获、载波快速同步、载波平稳跟踪以及在极低信噪比条件下正确解调,提出了一款8PSK的载波同步新方法。该方法设计简洁,实现模块化设计。下文分别从同步模型、同步新方法、MATLAB仿真比较和FPGA实现对其做说明。

1 载波同步模型

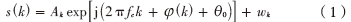

用于载波频偏估计的8PSK[4]接收信号可以表示为:

式中,k=0,1,2,。。.,7;Ak为幅度;fc为待估计的载波频率偏差;missing image file为调制相位;θ0为未知的载波相位;wk为加性高斯白噪声。

基于传统载波同步的接收端[5]模型如图2所示。

在低信噪比时,由于I、Q[6]两路相位噪声较大,使用单一的载波同步环路会导致在有限的引导数据长度下锁定慢,或载波环路系数调整后即便能较为快速锁定,也会极易再次失锁。既要载波同步锁定时间不能过慢,又不能在锁定后过调而导致失锁,仅使用一个载波同步环路无法满足数据链突发通信包的要求。

2 载波同步新方法

根据数据链突发通信包的特点,本文提出一种分时段控制载波同步方法,如图3所示。其基本思想是:分时段给出控制信号,首先选择载波快速同步方法,实现较大频偏的快速纠偏;其次,选择载波慢同步[7]方法,利用FIFO中存储的引导数据和快速同步方法中获得的初步频偏预估计值,完成载波慢同步,实现载波的精确同步;最后,通过载波跟踪方法,实现载波的平稳跟踪,以达到在低信噪比条件下不易因相位噪声过大引起过调而同步失锁,同时也减小环路[8]滤波的锁定抖动造成不必要的误码。

2.1 载波快同步方法

下变频后得到I、Q两路基带信号,相乘后,得到鉴相信号为:

将此鉴相信号送入快同步环路进行同步锁定,快同步环路采用常规的Costas环设计,得到的频偏累加值产生频率控制字控制NCO,实现频率补偿,利用经过初步频率补偿后的本地载波,完成本地接收信号的下变频。载波快同步会很快实现较大频偏的纠偏,在低信噪比的条件下,为了得到更加准确的频偏估计值,往往需要通过计算快速锁定以后较长平稳时间内的平均值才能提供给载波慢同步使用,否则会造成慢同步的环路压力过大,不利于实现低信噪比下的可靠同步。鉴于此,在载波同步快速锁定后的平稳过程中,对快速同步8个符号长度的频率控制字求平均(总共1 024点),得到初步频偏预估计值missing image file。

2.2 载波慢同步方法

当信号完成初步的载波同步后,频偏已纠偏到极小的范围内,但是依然没有实现载波同步,特别是在极低信噪比的条件下,载波快同步往往更加不准确,且载波快同步的方法并不适用于8PSK信号[9],因此需要通过载波的慢同步继续完成载波的准确同步。

信号表示为极坐标形式:

对8PSK信号做M-th非线性变换消除调制,信号变为单频信号:

上式表示的信号处理方式实际上是对相位误差进行归一化处理。

在实现过程中,下变频I、Q两路信号通过CORDIC算法计算出当前相位值φ(k),将φ(k)进行式(4)处理后,得到归一化的相位误差值,将该值送入慢同步环路进行同步锁定,慢同步环路采用常规的Costas环设计,得到的频偏累加值产生频率控制字,并结合初步频偏预估计值missing image file,实现对NCO的控制,达到慢速锁定的目的。

短包突发通信要求载波的快速锁定,载波慢同步环路滤波器系数设置时,环路收敛的速度比载波快同步快一倍,能够实现较快锁定,但是同时造成的相位收敛后相位的震荡要稍微剧烈一些;与此同时,载波慢同步算法的残余频偏调整速率约为载波快同步算法的1/8,所以最终的效果是,载波慢同步相位的收敛速度要比载波快同步慢,而且收敛后相位的震荡更加剧烈,因此需要载波跟踪同步过程。

2.3 载波跟踪同步方法

在载波慢同步过程中,载波频偏值已经被完全消除掉,但是由于信号处于低信噪比的条件时,噪声对相位和环路滤波器的影响较大,如果之后不进行载波跟踪,极易造成信号的再次失锁,因此最后进入到载波跟踪状态,保证整包信号都能够实现在低信噪比的条件下锁定。

载波跟踪同步方法与载波慢同步的方法一致,不同之处是,载波跟踪状态下不再需要过快调整相位收敛,仅仅需要慢速跟踪即可,因此,需要调整环路滤波器的系数,使得载波跟踪过程中相位的摆动变小,减小对信号本身造成的影响。该处理在信噪比极低的情况下可尽可能地提高码元同步的准确度,即改善整个系统的误码率。

通过上述3个步骤的处理,能够实现低信噪比下8PSK的快速载波同步,从而实现短包突发通信的实时接收。

3 仿真结果

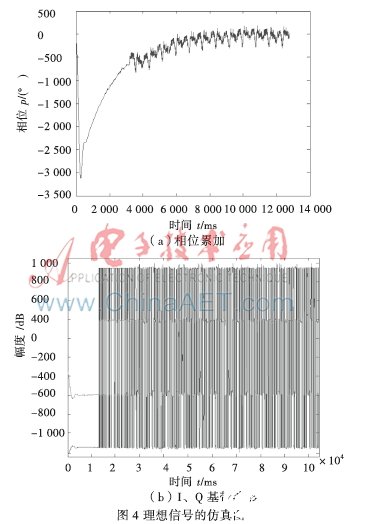

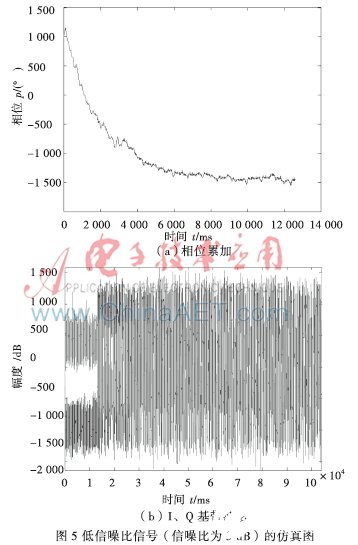

对产生1 kHz频偏的8PSK调制信号进行Matlab载波同步仿真。分别对理想信号和低信噪比信号(信噪比为5 dB)进行仿真,仿真结果如图4、图5所示。

仿真验证可得,在低信噪比条件下8PSK信号能实现快速同步及平稳跟踪。

4 载波同步FPGA实现

本方法采用以XC5VSX95T为核心的FPGA硬件系统[10]实现。模数芯片选用AD公司的AD9246BCPZ芯片,14位精度。研究和实验表明,系统运行良好。

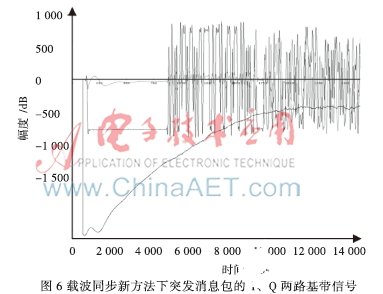

设定信号载波中心频率为24 MHz,采样速率为 32 MHz,短包突发通信的一包信号长度为400个符号,锁定后I、Q两路基带信号和调整值如图6所示。与图4比较,FPGA实现的结果与仿真结果一致。

5 结论

通过对该方法的仿真及硬件实现,并将该方法应用于实际工程中,充分验证了该载波同步新方法在低信噪比下收敛速度快、硬件资源耗用较少。

参考文献

[1] 李利,罗伟雄。软件接收机中DSB-SC信号载波同步的一种算法[J]。 电讯技术, 2002, 42(1): 143-150.

[2] 卢屹,张新军,张嘉俊,等。数字锁相环的参数设计及其应用[J]。 通信技术, 2001, 23(9):233-238.

[3] 彭岑,赵民建,郑雅敏.TCM-8PSK短包高速跳频接收机的快速载波同步[J]。 浙江大学学报(工学版), 2010,44(4):434-441.

[4] 朱彤。一种新的8DPSK调制解调方案[J]。 南京邮电学院学报, 1997,10(4):237-243.

[5] 付文君,王栓荣,吕娈,等。数字中频采样接收机的设计[C]。 中国空间科学学会空间探测专业委员会第十七次学术会议,2004. (下转第63页)

(上接第60页)

[6] 张双雄,周俊。 一种适用于宽带数据链的TCM编码新方法[J]。 电讯技术, 2011, 51(9): 356-362.

[7] 王静。 8PSK+TCM编码调制解调技术[D]。 南京:南京理工大学,2012.

[8] 苏伟,杜志秀。 8PSK-TCM在数据中继卫星通信信道上的应用研究[J]。 指挥技术学院学报, 1999, 10(4): 15-18.

[9] 朱彤。 一种新的8DPSK调制解调方案[J]。 南京邮电学院学报, 1997, 17(4): 49-53.

[10] 李滨滔,李春泉,戈志华。 基于FPGA的网格编码的设计与实现[J]。 科技广场, 2007, 18(3):144-151.

编辑:jq

-

FPGA

+关注

关注

1648文章

22120浏览量

621808 -

卫星通信

+关注

关注

12文章

779浏览量

39508 -

载波

+关注

关注

2文章

123浏览量

28758

发布评论请先 登录

基于一种低信噪比下8PSK的快速载波同步及FPGA实现

基于一种低信噪比下8PSK的快速载波同步及FPGA实现

评论