导言:这篇为PCIe要提及的时钟类型作个小铺垫,可以大致作一个了解,想深入了解可以参考更加细致的文献。

三种基本的I/O架构

1? 通用时钟(Common Clock)

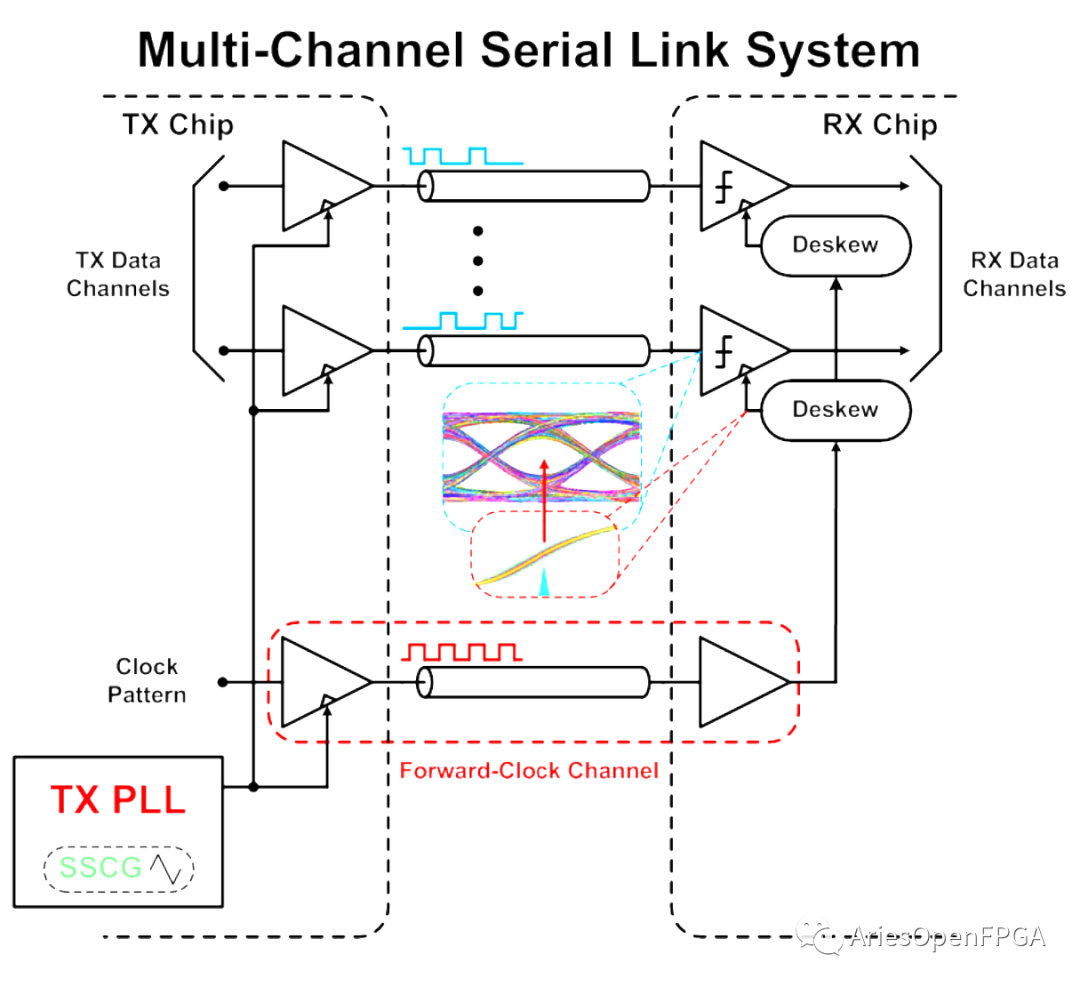

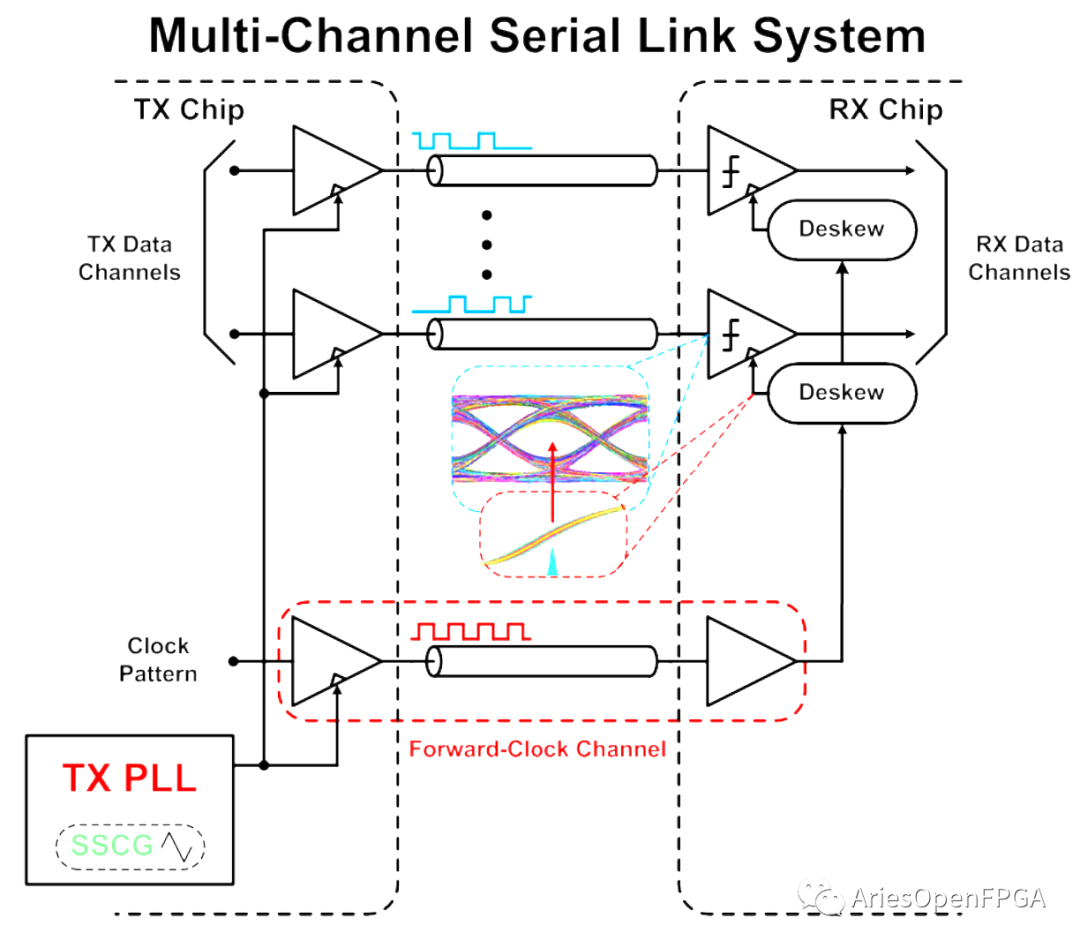

2? 前向时钟(Forward Clock)

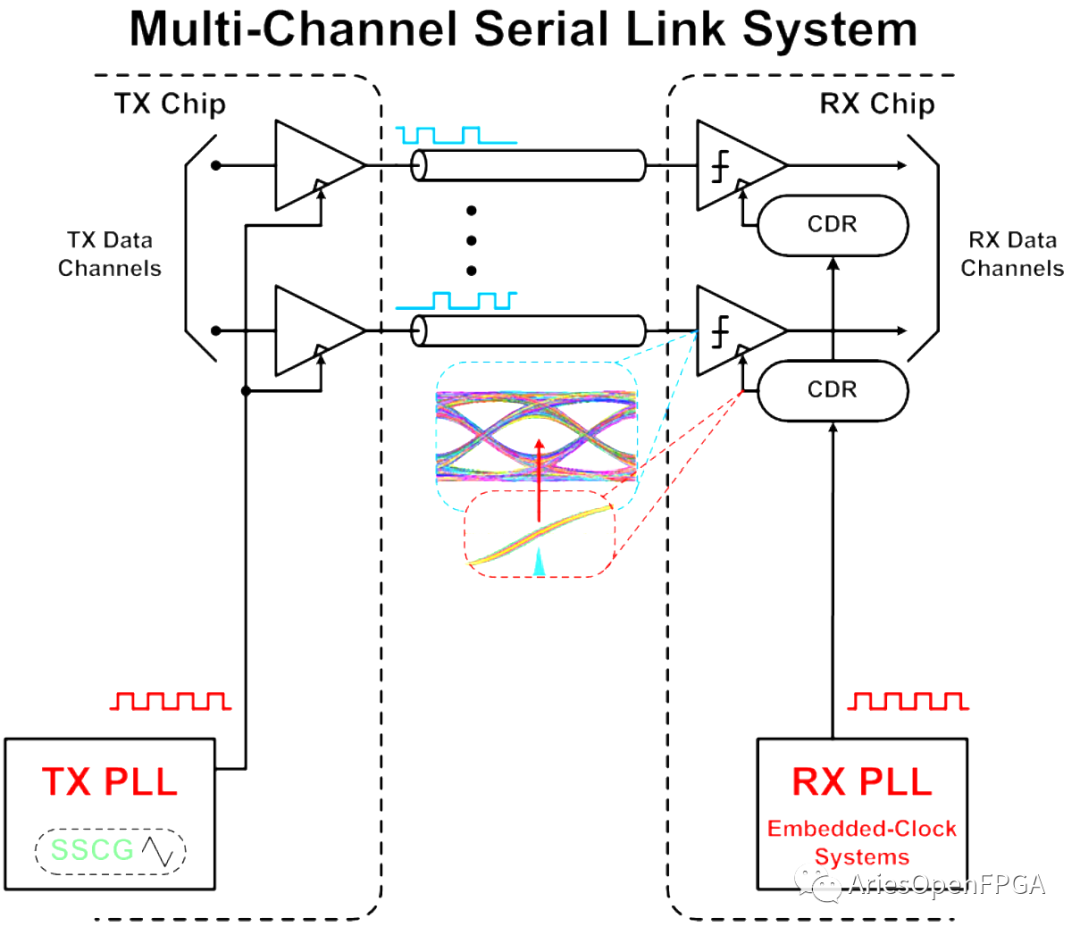

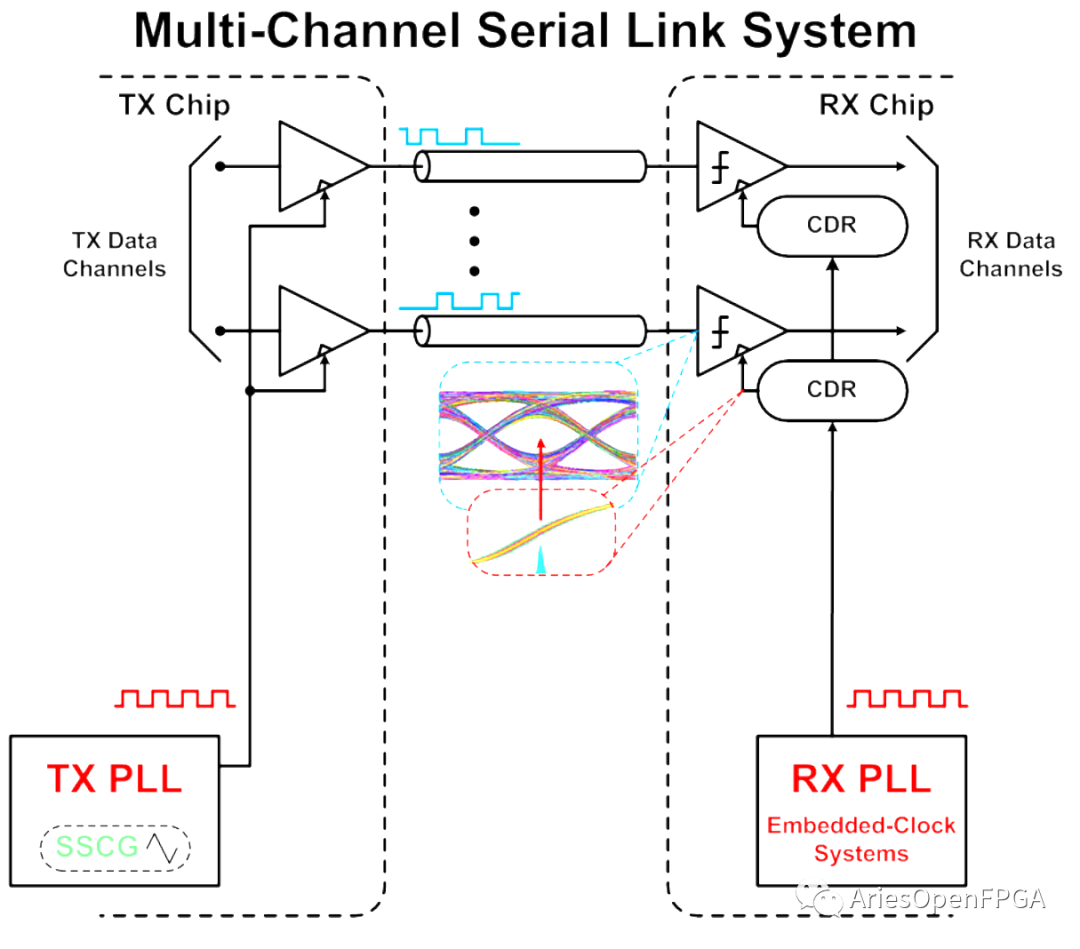

3? 嵌入时钟(Embedded Clock)

?这些I/O架构用于需要不同级别I/O带宽的各种应用

?处理器可能具有这些I/O类型中的一种或全部

?通常,相同的电路可用于仿真不同的I/O方案以重复使用设计

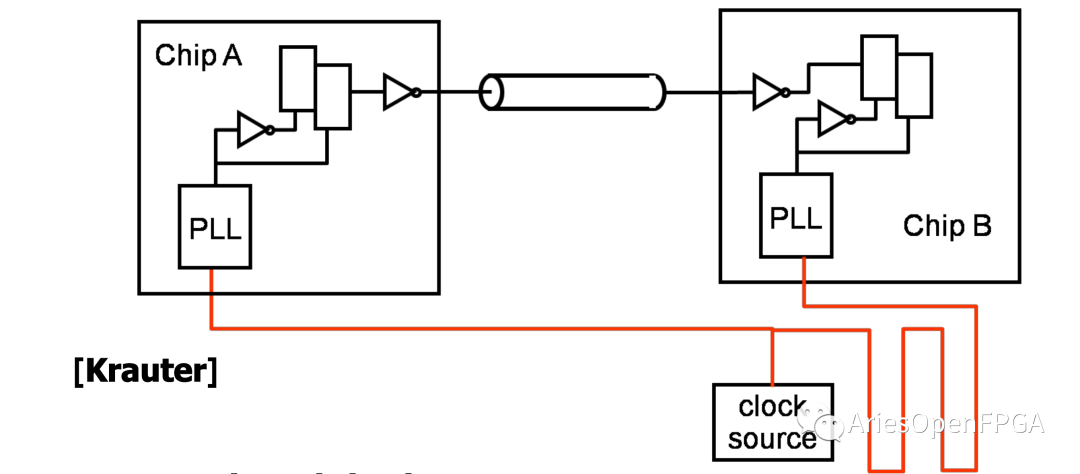

通用时钟的I/O架构

?在原始计算机系统中常见

?同步系统(Synchronous system)

?通用总线时钟控制芯片到芯片的传输

?需要等长的走线路径,以最大程度地减少时钟偏斜

?数据速率通常限制在0?100Mb(数据可能比较老)

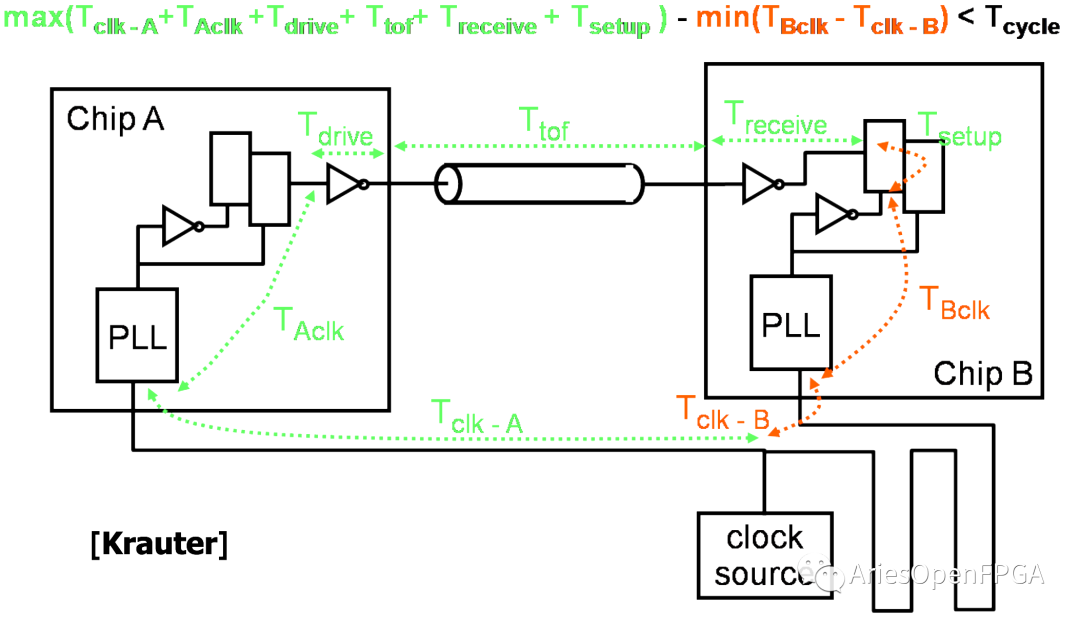

通用时钟I/O循环时间

通用时钟I/O限制

?难以控制时钟偏斜和传播延迟

?需要严格控制绝对延迟以满足给定的周期时间

?对芯片上电路和电路板布线路径中的延迟变化很敏感

?由于片上延迟和片外延迟之间的相关性低,难以补偿延迟变化

?虽然通常用于片上通信,但应用的速度受限

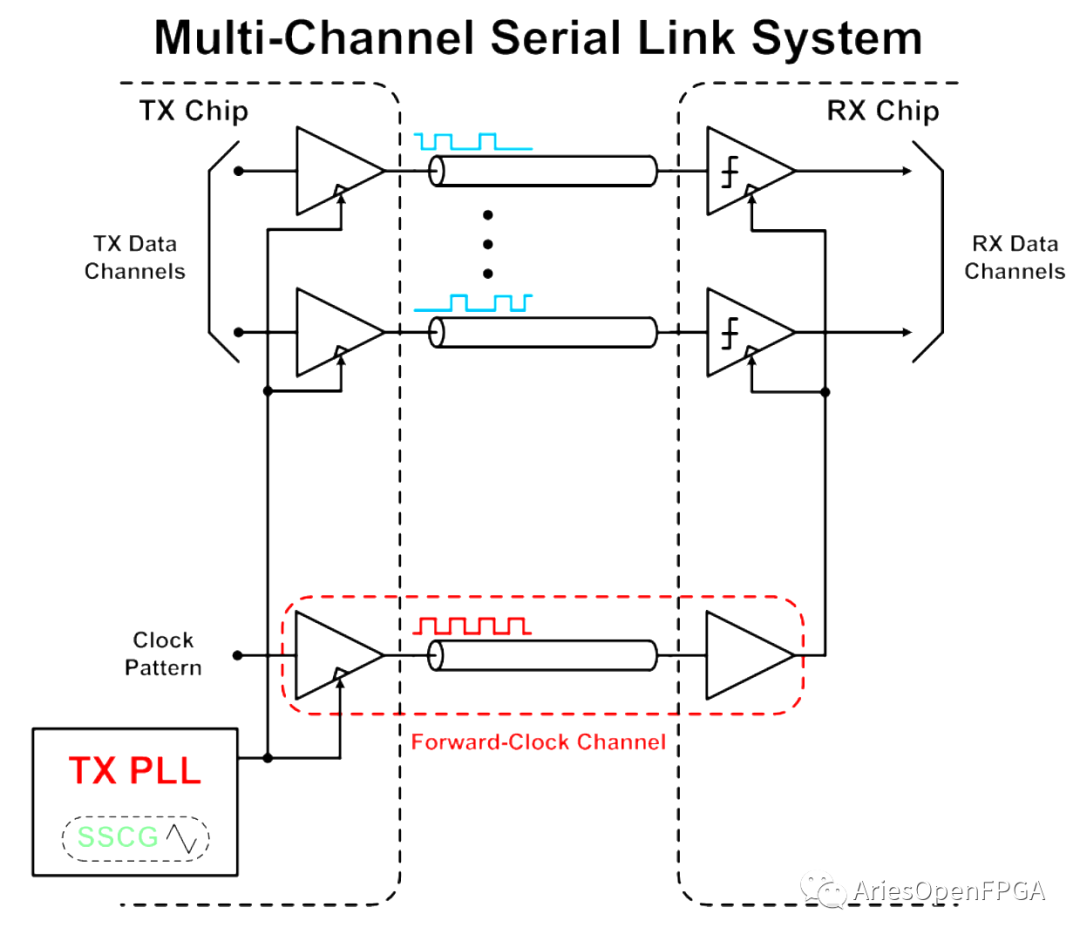

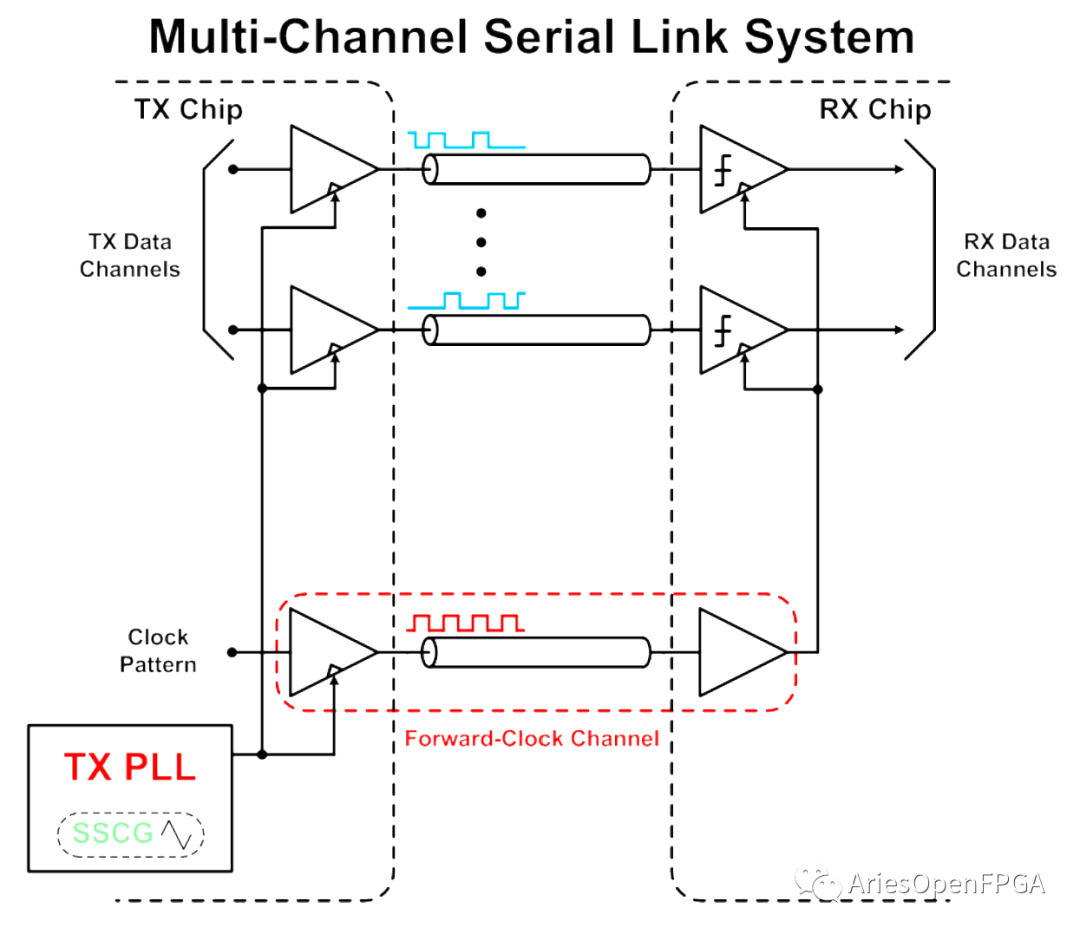

前向时钟I/O架构

?通常作为高速传输中,TX芯片到RX芯片的前向参考时钟

?同步系统(Mesochronous system)

?用于处理器内存接口和多处理器通信

?Hypertransport(HT总线)

?需要一个额外的时钟通道

?“相干”时钟可实现从低频到高频的抖动跟踪

?需要好的时钟接收放大器,因为前向时钟会被通道衰减

前向时钟I/O限制

?时钟偏斜会限制前向时钟I/O性能

?驱动能力和负荷失配

?互连长度不匹配

?低通通道导致抖动放大

?前向时钟的占空比变化

前向时钟I/O偏斜校正

?每通道偏移校正可显着提高数据速率

?采样时钟调整为输入数据眼的中心时钟

?实施

?延迟锁定环路和相位内插器

?注入锁定振荡器

?相位采集可以是

?基于BER的附加输入相位采样器

?基于相位检测器,并带有额外的输入相位采样器,定期打开电源

前向时钟I/O电路

?TX PLL

?TX时钟分配

?复制TX时钟驱动器

?通道

?前向时钟放大器

?RX时钟分配

?去偏斜电路

?DLL/PI

?注入锁定振荡器

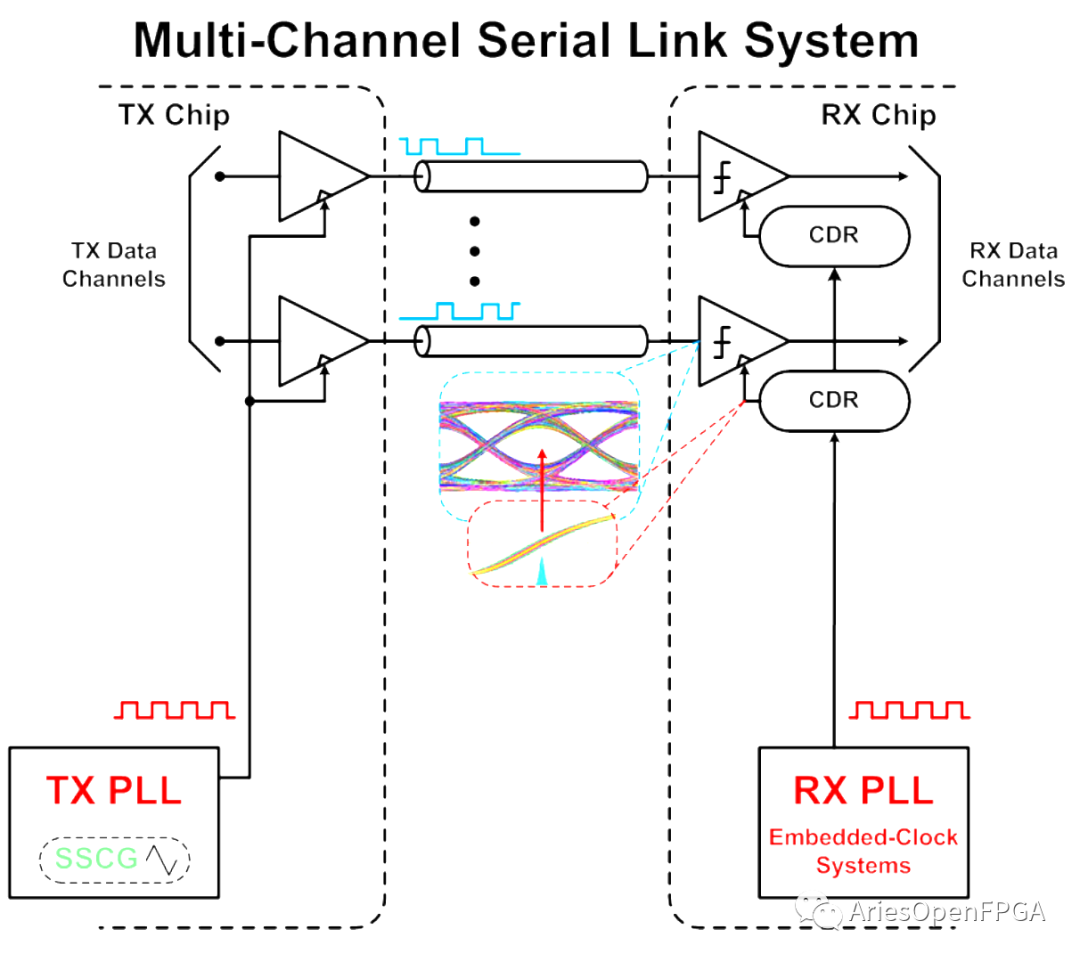

嵌入式时钟I/O架构

?可用于同步或准同步系统(mesochronousor plesiochronous systems)

?从输入数据流中提取时钟频率和最佳相位

?持续运行的相位检测

?CDR实施(应用)(CDR:clock and data recovery)

?基于每个通道的PLL

?双环带全局PLL或

?本地DLL/PI

?本地相位旋转器PLL

嵌入式时钟I/O限制

?抖动跟踪受CDR带宽限制(clock and data recovery)

?技术扩展允许具有更高带宽的CDR,从而可以实现更高的频率抖动跟踪

?一般而言,实现前向时钟需要更多的硬件(注:原文是,Generally more hardwarethan forward clockimplementations,我联系上下文自己翻译的,这里贴出来作为参考)

?额外的输入相位采样器

嵌入式时钟I/O电路

?TX PLL

?TX时钟分配

?CRD

?基于每个通道的PLL

?双环带全局PLL和

?本地DLL / PI

?本地相位旋转器PLL

?全局PLL需要将RX时钟分配给各个通道

原文标题:?I/O时钟架构

文章出处:【微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

时钟

+关注

关注

11文章

1909浏览量

133475 -

PCIe

+关注

关注

16文章

1365浏览量

85780

原文标题:?I/O时钟架构

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

介绍三种常见的MySQL高可用方案

nvme IP开发之PCIe下

CMOS,Bipolar,FET这三种工艺的优缺点是什么?

澜起科技发布面向新一代CPU平台的I/O集线器 (IOH) 芯片M88IO3020

I/O接口与I/O端口的区别

示波器的三种触发模式

什么是PID调节器的三种模式

I2S有左对齐,右对齐跟标准的I2S三种格式,那么这三种格式各有什么优点呢?

基本放大电路有哪三种

mosfet的三种工作状态及工作条件是什么

物联网中常见的I/O扩展电路设计方案_IIC I/O扩展芯片

PCIe中三种基本的I/O架构

PCIe中三种基本的I/O架构

评论