原创声明:

本原创教程由芯驿电子科技(上海)有限公司(ALINX)创作,版权归本公司所有,如需转载,需授权并注明出处。

适用于板卡型号:

AXU2CGA/AXU2CGB/AXU3EG/AXU4EV-E/AXU4EV-P/AXU5EV-E/AXU5EV-P /AXU9EG/AXU15EG

按键是FPGA设计当中最常用也是最简单的外设,本章通过按键检测实验,检测开发板的按键功能是否正常,并了解硬件描述语言和FPGA的具体关系,学习Vivado RTL ANALYSIS的使用。

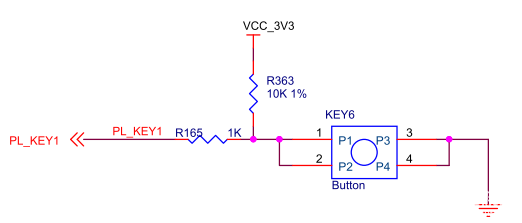

1.按键硬件电路

开发板按键部分电路

从图中可以看到,电路的按键松开时是高电平,按下时是低电平。

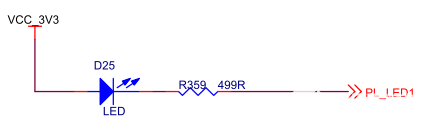

开发板LED部分电路

开发板LED部分电路

而LED部分,高电平灭,低电平亮

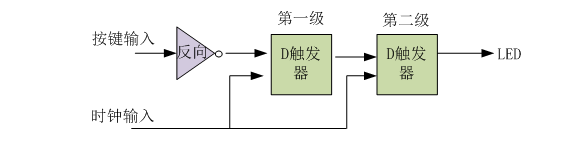

2. 程序设计

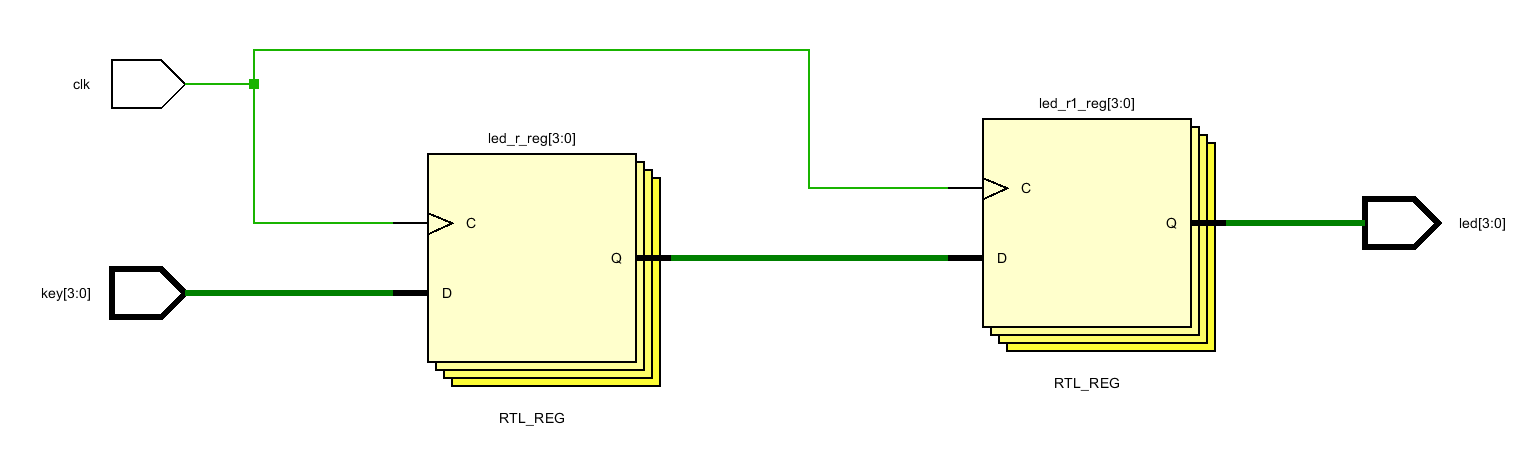

这个程序没有设计的很复杂,通过简单的硬件描述语言看透硬件描述语言和FPGA硬件的联系。首先我们将按键输入经过一个非门后再经过2组D触发器。经过D触发器的信号,会在D触发器时钟输入的上升沿锁存然后再送到输出。

在进行硬件描述语言编码之前,我们已经把硬件构建完成,这是一个正常的开发流程。有了硬件设计思路无论是通过画图还是通过Verilog HDL、VHDL都能完成设计,根据设计的复杂程序和对某种语言的熟悉程序来选择工具。

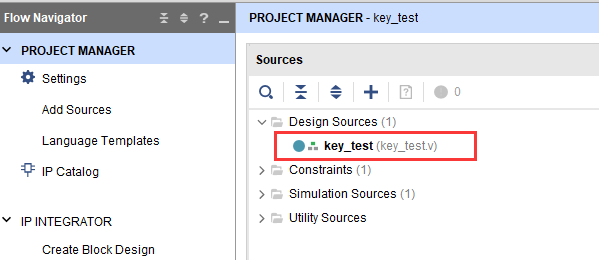

3. 创建Vivado工程

3.1 首先建立按键的测试工程,添加verilog测试代码,完成编译分配管脚等流程。

`timescale1ns/1psmodulekey_test( inputclk,//systemclock25Mhzonboard input[3:0]key,//inputfourkeysignal,whenthekeydown,thevalueis0 output[3:0]led//LEDdisplay,whenthesiganllow,LEDlighten);reg[3:0]led_r;//definethefirststageregister,generatefourDFlip-flop reg[3:0]led_r1;//definethesecondstageregister,generatefourDFlip-flopalways@(posedgeclk)begin led_r<=??key;//first?stage?latched?dataendalways@(posedge?clk)begin led_r1?<=?led_r;//second?stage?latched?dataendassign?led?=?led_r1;endmodule

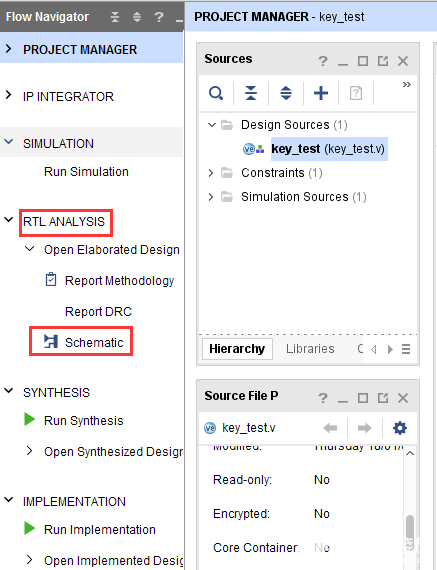

3.2 我们可以使用RTL ANALYSIS工具查看设计

3.3 分析RTL图,可以看出两级D触发器,和预期设计一致。

4. 板上验证

Bit文件下载到开发板以后,开发板上的"PL LED"处于亮状态,按键“PL KEY1”按下“PL LED1”灭。

-

FPGA

+关注

关注

1646文章

22097浏览量

620770 -

按键

+关注

关注

4文章

227浏览量

58169 -

Zynq

+关注

关注

10文章

617浏览量

48422 -

MPSoC

+关注

关注

0文章

202浏览量

24809 -

Vivado

+关注

关注

19文章

835浏览量

69168

发布评论请先 登录

璞致电子 UltraScale+ RFSoC 架构下的软件无线电旗舰开发平台

AMD Spartan UltraScale+ FPGA 开始量产出货

Xilinx Ultrascale系列FPGA的时钟资源与架构解析

AMD/Xilinx Zynq? UltraScale+ ? MPSoC ZCU102 评估套件

在米尔电子MPSOC实现12G SDI视频采集H.265压缩SGMII万兆以太网推流

九章云极DataCanvas公司与云南联通签署合作协议

扬帆出海!九章云极DataCanvas公司惊艳亮相迪拜GITEX Global 2024

在米尔电子MPSOC实现12G SDI视频采集H.265压缩SGMII万兆以太网推流

九章云极DataCanvas公司「算力包」产品璀璨亮相2024中国算力大会!

《DNK210使用指南 -CanMV版 V1.0》第九章 打印输出实验

九章云极DataCanvas算力包正式发布

使用TPS65086x PMIC为Xilinx Zynq UltraScale MPSoC供电

ALINX FPGA+GPU异架构视频图像处理开发平台介绍

第九章-PID整定方法 STM32PID驱动编码器 STM32PID控制电机转速

【ZYNQ Ultrascale+ MPSOC FPGA教程】第九章Vivado下按键实验

【ZYNQ Ultrascale+ MPSOC FPGA教程】第九章Vivado下按键实验

评论