现代单片机主要是采用CMOS工艺制成的。

01 MOS管

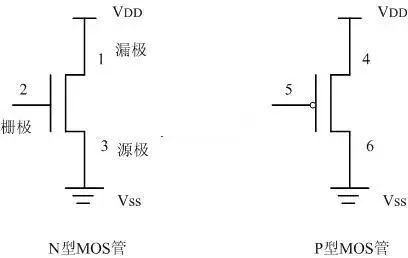

MOS管又分为两种类型:N型和P型。

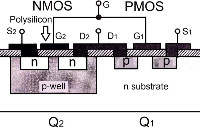

如下图所示:

以N型管为例,2端为控制端,称为“栅极”;3端通常接地,称为“源极”;源极电压记作Vss,1端接正电压,称为“漏极”,漏极电压记作VDD。要使1端与3端导通,栅极2上要加高电平。

对P型管,栅极、源极、漏极分别为5端、4端、6端。要使4端与6端导通,栅极5要加低电平。

在CMOS工艺制成的逻辑器件或单片机中,N型管与P型管往往是成对出现的。同时出现的这两个CMOS管,任何时候,只要一只导通,另一只则不导通(即“截止”或“关断”),所以称为“互补型CMOS管”。

02 CMOS逻辑电平

高速CMOS电路的电源电压VDD通常为+5V;Vss接地,是0V。 高电平视为逻辑“1”,电平值的范围为:VDD的65%~VDD(或者VDD-1.5V~VDD) 低电平视作逻辑“0”,要求不超过VDD的35%或0~1.5V。 +1.5V~+3.5V应看作不确定电平。在硬件设计中要避免出现不确定电平。 近年来,随着亚微米技术的发展,单片机的电源呈下降趋势。低电源电压有助于降低功耗。VDD为3.3V的CMOS器件已大量使用。在便携式应用中,VDD为2.7V,甚至1.8V的单片机也已经出现。将来电源电压还会继续下降,降到0.9V,但低于VDD的35%的电平视为逻辑“0”,高于VDD的65%的电平视为逻辑“1”的规律仍然是适用的。

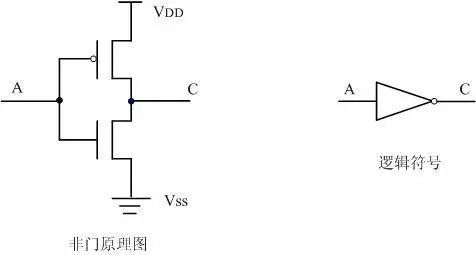

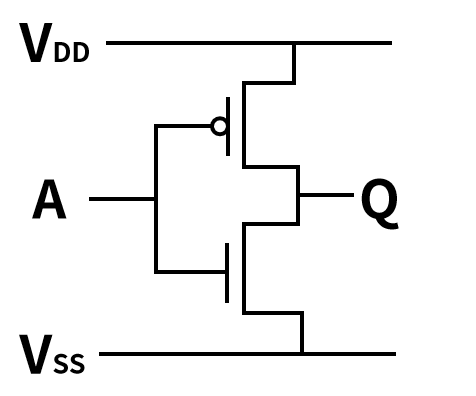

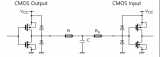

03 非门

非门(反向器)是最简单的门电路,由一对CMOS管组成。其工作原理如下:

A端为高电平时,P型管截止,N型管导通,输出端C的电平与Vss保持一致,输出低电平;A端为低电平时,P型管导通,N型管截止,输出端C的电平与VDD一致,输出高电平。

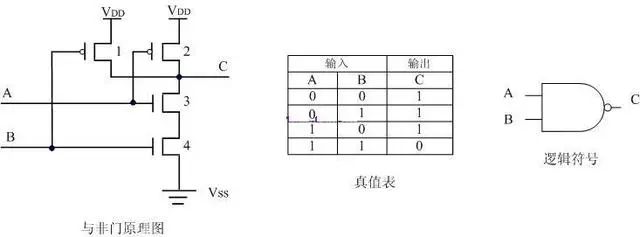

04 与非门

与非门工作原理:

①、A、B输入均为低电平时,1、2管导通,3、4管截止,C端电压与VDD一致,输出高电平。

②、A输入高电平,B输入低电平时,1、3管导通,2、4管截止,C端电位与1管的漏极保持一致,输出高电平。

③、A输入低电平,B输入高电平时,情况与②类似,亦输出高电平。

④、A、B输入均为高电平时,1、2管截止,3、4管导通,C端电压与地一致,输出低电平。

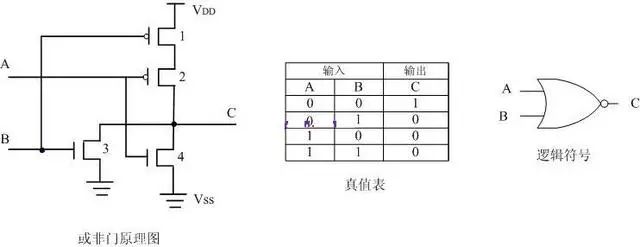

05 或非门

或非门工作原理:

①、A、B输入均为低电平时,1、2管导通,3、4管截止,C端电压与VDD一致,输出高电平。

②、A输入高电平,B输入低电平时,1、4管导通,2、3管截止,C端输出低电平。

③、A输入低电平,B输入高电平时,情况与②类似,亦输出低电平。

④、A、B输入均为高电平时,1、2管截止,3、4管导通,C端电压与地一致,输出低电平。

注:

将上述“与非”门、“或非”门逻辑符号的输出端的小圆圈去掉,就成了“与”门、“或”门的逻辑符号。而实现“与”、“或”功能的电路图则必须在输出端加上一个反向器,即加上一对CMOS管,因此,“与”门实际上比“与非”门复杂,延迟时间也长些,这一点在电路设计中要注意。

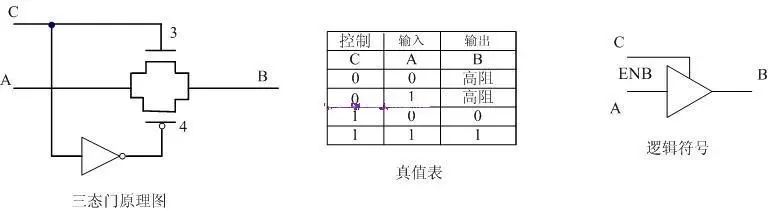

06 三态门

三态门的工作原理:

当控制端C为“1”时,N型管3导通,同时,C端电平通过反向器后成为低电平,使P型管4导通,输入端A的电平状况可以通过3、4管到达输出端B。

当控制端C为“0”时,3、4管都截止,输入端A的电平状况无法到达输出端B,输出端B呈现高电阻的状态,称为“高阻态”。

这个器件也称作“带控制端的传输门”。带有一定驱动能力的三态门也称作“缓冲器”,逻辑符号是一样的。

注:

从CMOS等效电路或者真值表、逻辑表达式上都可以看出,把“0”和“1”换个位置,“与非”门就变成了“或非”门。对于“1”有效的信号是“与非”关系,对于“0”有效的信号是“或非”关系。

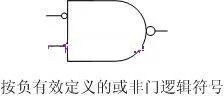

上述图中画的逻辑器件符号均是正逻辑下的输入、输出关系,即对“1”(高电平)有效而言。而单片机中的多数控制信号是按照负有效(低电平有效)定义的。例如片选信号CS(Chip Select),指该信号为“0”时具有字符标明的意义,即该信号为“0”表示该芯片被选中。因此,“或非”门的逻辑符号也可以画成下图。

07 组合逻辑电路

“与非”门、“或非”门等逻辑电路的不同组合可以得到各种组合逻辑电路,如译码器、解码器、多路开关等。

组合逻辑电路的实现可以使用现成的集成电路,也可以使用可编程逻辑器件,如PAL、GAL等实现。

责任编辑:lq

-

CMOS

+关注

关注

58文章

6056浏览量

239385 -

单片机

+关注

关注

6069文章

45095浏览量

654062 -

高电平

+关注

关注

6文章

208浏览量

22323

原文标题:5分钟弄懂!MOS管及简单CMOS逻辑电平电路

文章出处:【微信号:mcu168,微信公众号:硬件攻城狮】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

CMOS的逻辑门如何应用在电路中

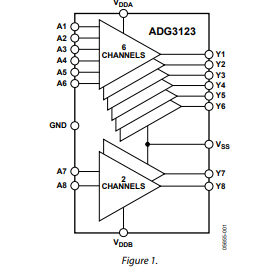

ADG3123 8通道CMOS逻辑转高压电平转换器技术手册

浮思特 | CMOS技术原理与应用:从晶体管结构到反相器设计

硬件基础篇——TTL与CMOS电平

CMOS逻辑IC是如何构成的

TTL电平与信号降噪技术的区别

使用TTL电平时的常见问题

TTL电平与CMOS电平的区别是什么

如何优化CMOS逻辑IC的性能

MOS管及简单CMOS逻辑电平电路

MOS管及简单CMOS逻辑电平电路

评论