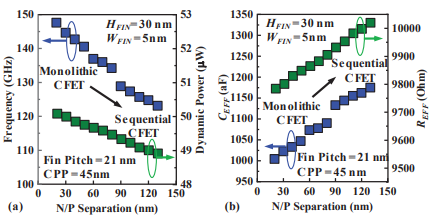

在去年六月举办的IEEE Symposium on VLSI Technology会议上,IMEC展示了基于N14工艺开发的单片集成CFET器件,由于N/P之间更加紧凑,相比较“顺序法”制备的CFET,“单片法”制备的CFET具有更低的寄生电阻(REF)和电容(CEFF),从而获得更高的性能增益。IMEC认为这一技术将会成1nm集成电路制造工艺的解决方案。

研究背景

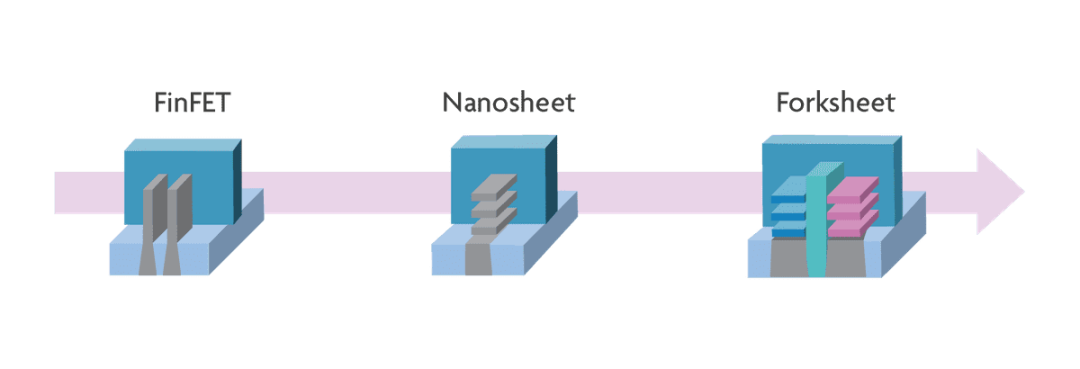

先进集成电路沿着摩尔定律发展,晶体管尺寸每隔一段时间就会缩小;但一种工艺结构总会接近其物理极限,当一种晶体管结构达到其缩小的物理极限,便需要新的器件结构以满足更高性能、更小晶体管的需求,例如平面CMOS工艺在28nm节点之后便转换为FinFET立体器件工艺;而当前FinFET走到5nm节点,GAA环栅晶体管也即将导入到三星和台积电产线。

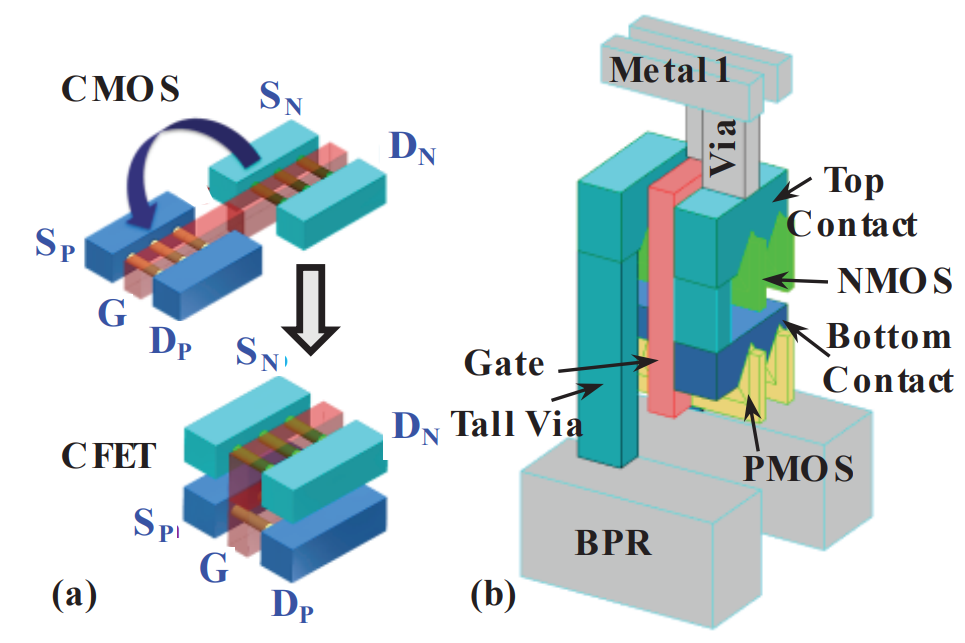

对于5nm以下的技术节点,目前已有多种晶体管结构的研究模型,其中最有前途的结构包括垂直堆叠的stacked Nanosheets结构、forksheets*结构以及CFET*结构,他们的共通点是先构建平面结构再构建垂直方向的结构。在CFET的制备工艺中,目前分为顺序集成(sequential Integration)与单片集成(monolithic integration),在“顺序法”中,nFET和pFET被制造在同一片晶圆上;而在“单片法”中,nFET和pFET在分离的晶圆上制造并进行“贴合”,从而可以针对该器件最佳化每个器件的制造流程。

基于比利时IMEC提出的这一技术路线,他们基于其开发的N14 FinFET工艺进行CFET的开发制备,通过“单片法”工艺在12吋晶圆上实现了样品的片上演示,并与“顺序法”的数据进行了对比。

相关成果以“First Monolithic Integration of 3D Complementary FET (CFET) on 300mm Wafers”为题发表于2020年6月举办的2020IEEE Symposium on VLSI Technology,并于12月公开,S.Subramanian, M. Hosseini等32名来自IMEC研究中心和以色列nova半导体公司的研究人员为本文共同作者。

从FinFET到Forksheet

*Forksheet,是IMEC提出的一种新兴器件架构,是Nanosheet的自然延伸。相比Nanosheet,其在沟道由叉形栅极结构控制,通过在栅极图案化之前在p和nMOS器件之间引入“介电墙”来实现的。该墙将p栅沟槽与n栅沟槽物理隔离,从而允许更紧密的n到p间距。

*CFET(完整名称Complementary FET),是将nMOS和pMOS纵向排列的一种新型晶体管结构,通过将Contact Poly Pitch(PP)做到最小,极大地缩小了CMOS和SRAM的面积。

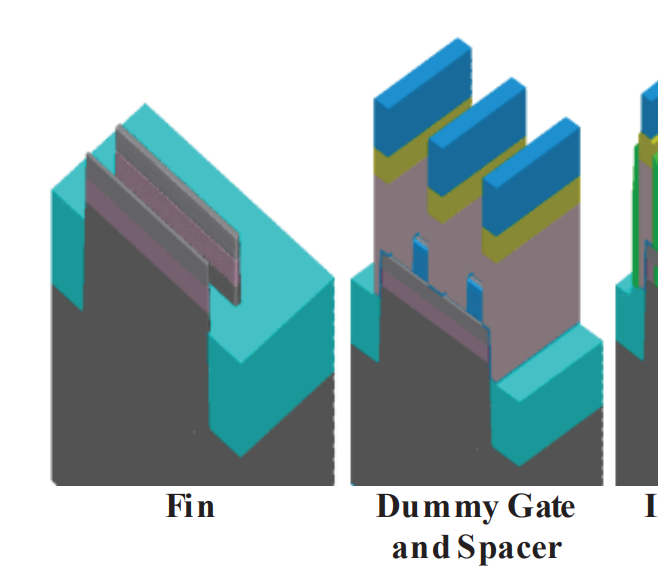

制备方法

IMEC团队首次在300mm晶圆上演示了在底部pMOS FinFET上构筑nMOS nanosheet的CFET制备工艺。由于N/P之间更加紧凑,相比较“顺序法”制备的CFET,“单片法”制备的CFETs具有更低的寄生电阻(REFF)和电容(CEFF),从而获得更高的性能增益。

CFET结构示意图

滑动查看:CFET制备工艺中的关键步骤

RO性能与寄生参数测试

滑动查看:制备过程中晶体管横截面的TEM形貌像

前景展望

本项研究是集成电路新工艺研发的一大重要成果,“单片法”CFET器件以更紧凑的空间提供了更佳的晶体管理论性能,被认为是1nm工艺上的重要技术路线之一,IMEC提出并局部验证了这一方向的实际性能表现,对于先进工艺的发展有着举足轻重的指导意义,新材料、新型器件结构以及多种路线混合(例如异质CFET),究竟哪一种解决方案会赢得晶圆制造厂的青睐并成为最终产品的答案,也很值得期待。

团队介绍

IMEC,全称:Interuniversity Microelectronics Centre,即比利时微电子研究中心,是一家成立于?1984?年的科技研发中心,?总部设在鲁汶。IMEC?的战略定位为纳米电子和数字技术领域全球领先的前瞻性重大创新中心,与?IBM?和英特尔(Intel)并称科技界的“3I”。

IMEC?从?2004?年起参与了从45nm到7nm的芯片前沿技术的研发,核心科研合作伙伴覆盖了全球几乎所有顶尖信息技术公司,如英特尔、IBM、德州仪器、应用材料、AMD、索尼、台积电、西门子、三星、爱立信和诺基亚等,拥有来自近80个国家4000名研究人员。

在国内,以中芯国际为代表的晶圆代工企业也与IMEC有着紧密合作:2015年中芯国际先进制程研发项目签约仪式在人民大会堂举行,IMEC、华为和高通在合作方中各占一席,四方共同进行标准单元库的定义、优化和制造工艺的开发。

原文标题:科研前线 | IMEC首次在12吋晶圆上实现3D CFET集成

文章出处:【微信公众号:芯片揭秘】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

3D

+关注

关注

9文章

2965浏览量

111402 -

晶圆

+关注

关注

53文章

5213浏览量

130299 -

IMEC

+关注

关注

0文章

59浏览量

22625

原文标题:科研前线 | IMEC首次在12吋晶圆上实现3D CFET集成

文章出处:【微信号:ICxpjm,微信公众号:芯片揭秘】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

下一代高速芯片晶体管解制造问题解决了!

IMEC首次在12吋晶圆上实现3D CFET集成

IMEC首次在12吋晶圆上实现3D CFET集成

评论