声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

pll

+关注

关注

6文章

891浏览量

136692 -

功率

+关注

关注

14文章

2101浏览量

72078 -

RF

+关注

关注

65文章

3179浏览量

169458

发布评论请先 登录

相关推荐

热点推荐

PLL技术在FPGA中的动态调频与展频功能应用

随着现代电子系统的不断发展,时钟管理成为影响系统性能、稳定性和电磁兼容性(EMI)的关键因素之一。在FPGA设计中,PLL因其高精度、灵活性和可编程性而得到广泛应用,本文将深入探讨PLL技术

PLL用法

易灵思的FPGA在生成PLL的方式与别的厂家稍有区别,这与其的core和interface架构是相对应的。对于易灵思的FPGA来讲,PLL,GPIO,MIPI,LVDS和DDR相对于core部分都是

集成整数 N 分频 PLL 和 VCO 的 350-5000 MHz 宽带接收混频器 skyworksinc

电子发烧友网为你提供()集成整数 N 分频 PLL 和 VCO 的 350-5000 MHz 宽带接收混频器相关产品参数、数据手册,更有集成整数 N 分频 PLL 和 VCO 的 35

发表于 05-22 18:31

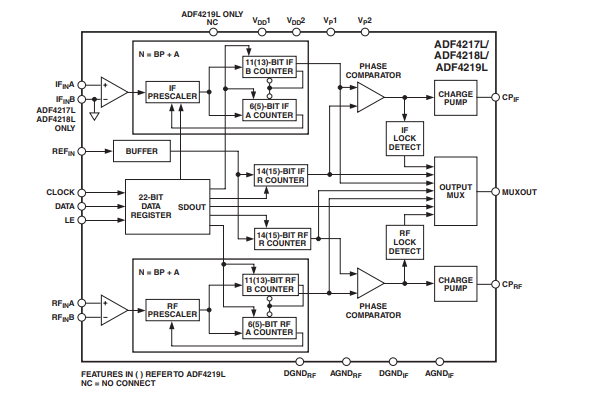

ADF4217L/ADF4218L/ADF4219L低功耗、双通道RF/IF整数N分频PLL技术手册

ADF4218L频率合成器IC与VCO和环路滤波器一起使用时,可构成完整的锁相环(PLL)。这款ADI解决方案可以为无线应用中的RF信号上变频和下变频提供先进的本振(LO)。该PLL由

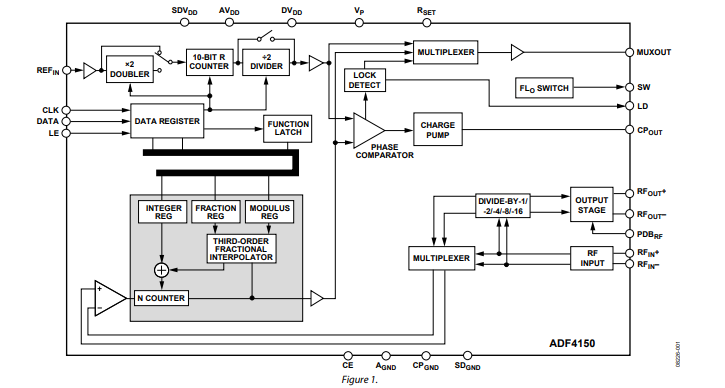

ADF4150小数N/整数N分频PLL频率合成器技术手册

ADF4150结合外部电压控制振荡器(VCO)、环路滤波器和外部基准频率使用时,可实现小数N分频或整数N分频锁相环(PLL)频率合成器。

它能够与外部VCO器件配合使用,且与ADF4350软件

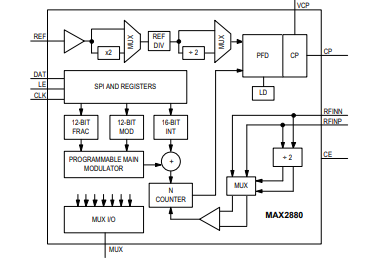

MAX2880 250MHz-12.4GHz、高性能、分数/整数型N分频PLL技术手册

MAX2880为高性能锁相环(PLL),提供整数或分数N分频工作模式。器件配合外部参考时钟振荡器、环路滤波器和VCO,可以构成超低噪声、低杂散频率合成器,可接受高达12.4GHz的RF

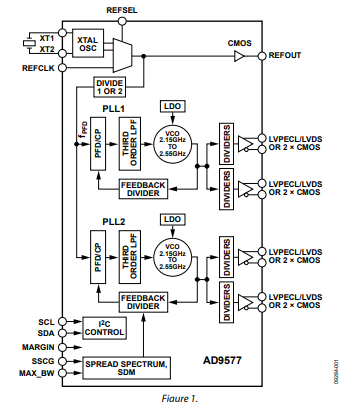

AD9577带双路PLL、扩频和余量微调功能的时钟发生器技术手册

AD9577既提供一个多路输出时钟发生器功能,又带有两个片上锁相环内核PLL1和PLL2,专门针对网络时钟应用而优化。PLL设计基于ADI公司成熟的高性能、低抖动频率合成器产品系列,确

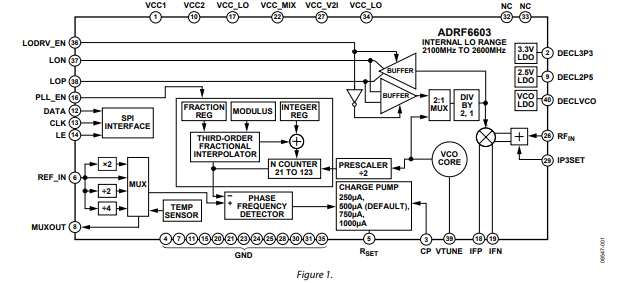

ADRF6603 1,100 MHz至3,200MHz接收混频器,集成小数N分频PLL和VCO技术手册

ADRF6603是一款高动态范围有源混频器,集成小数N分频锁相环(PLL)和压控振荡器(VCO),用于内部混频器LO的产生。

ADRF6603与ADRF6602共同构成了一个集成PLL/混频器系列,涵盖2100 MHz至2

LMX2595 EVM说明–具有集成VCO的20GHz宽带低噪声PLL

电子发烧友网站提供《LMX2595 EVM说明–具有集成VCO的20GHz宽带低噪声PLL.pdf》资料免费下载

发表于 11-26 14:35

?4次下载

锁相环PLL的噪声分析与优化 锁相环PLL与相位噪声的关系

锁相环(PLL)是一种反馈控制系统,它通过比较输入信号和输出信号的相位差异,调整输出信号以实现相位锁定。在许多应用中,如无线通信、频率合成和时钟同步,PLL的性能直接关系到系统的整体性能

锁相环PLL技术在通信中的应用

技术的基本原理 PLL技术主要由相位比较器、环路滤波器和压控振荡器(Voltage-Controlled Oscillator,VCO)三部分组成。相位比较器接收输入信号和反馈信号,并

锁相环PLL的工作原理 锁相环PLL应用领域

锁相环(Phase-Locked Loop,简称PLL)是一种电子电路,它能够自动调整输出信号的相位,使其与输入信号的相位同步。这种电路在电子工程领域有着广泛的应用,特别是在频率合成、时钟恢复、调制

PLL1705/PLL1706双通道PLL多时钟发生器数据表

电子发烧友网站提供《PLL1705/PLL1706双通道PLL多时钟发生器数据表.pdf》资料免费下载

发表于 08-22 11:32

?0次下载

高性能RF PLL和PLL VCO技术的介绍

高性能RF PLL和PLL VCO技术的介绍

评论