了解在启用PIPE模式的情况下创建PCI Express IP设计的过程,以便可以使用Mentor Graphics Questa Verification IP(QVIP)进行模拟。 PIPE模式模拟通过移除tra来大大加快模拟时间

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

赛灵思

+关注

关注

33文章

1797浏览量

132594 -

IP

+关注

关注

5文章

1825浏览量

153194 -

PIC

+关注

关注

8文章

507浏览量

89574

发布评论请先 登录

相关推荐

热点推荐

简仪科技推出PXIe-3171 PXI Express嵌入式控制器

PXIe-3171配备集成的PCI Express交换机,支持四个x4或两个x8的PXI Express配置,通过PCI Express 3

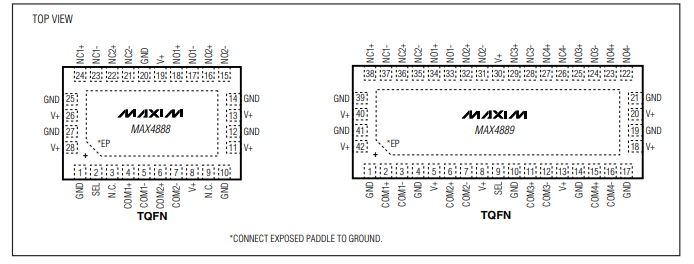

MAX4888/MAX4889 2.5Gbps PCI Express无源开关技术手册

MAX4888/MAX4889高速无源开关可在两个接收端之间切换PCI Express? (PCIe)数据。MAX4888是四路单刀/双掷(4 x SPDT)开关,非常适合在两个接收端之间切换2路

QDMA Subsystem for PCI Express v5.0产品指南

AMD QDMA Subsystem for PCI Express( PCIe )旨在利用多队列的概念实现高性能 DMA,以搭配 PCI Express Integrated Blo

PCI Express Gen5自动化多通道测试方案

对高速链路(如PCI Express)的全面表征需要对被测链路的发送端(Tx)和接收端(Rx)进行多差分通道的测量。由于需要在不同通道之间进行同轴连接的物理切换,这对于完全自动化的测试环境来说是一个

基于Altera Agilex? 7 400G Ethernet IP 与FPC202芯片控制使用手册

* (CXL) v1.1 或 400G 以太网连接的设计提供了一个完整的原型开发和参考平台。 使用 Agilex 7 FPGA I 系列 FPGA 开发套件可以: 使用 Altera 或第三方的适用 IP*,利用符合 PCI-Express 外形规格的开发板开发和测试 P

发表于 12-12 10:20

?1234次阅读

Xilinx 7系列FPGA PCIe Gen3的应用接口及特性

Xilinx7系列FPGA集成了新一代PCI Express集成块,支持8.0Gb/s数据速率的PCI Express 3.0。本文介绍了7

Efinity FIFO IP仿真问题 -v1

Efinity目前不支持联合仿真,只能通过调用源文件仿真。 我们生成一个fifo IP命名为fifo_sim 在Deliverables中保留Testbench的选项。 在IP的生成目

KeyStone设备的PCI Express (PCle)常见问题

电子发烧友网站提供《KeyStone设备的PCI Express (PCle)常见问题.pdf》资料免费下载

发表于 10-11 10:21

?0次下载

VIAVI Xgig 4K16 PCI Express 4.0 协议分析仪平台介绍

VIAVI Xgig 4K16 PCI Express 4.0 协议分析仪功能强大的 PCIe Gen 4.0 分析系统,拥有先进的跟踪、分析和干扰功能,能够对流量进行全面分析

使用TI PCI-Express Gen5.0转接驱动器进行眼图扫描

电子发烧友网站提供《使用TI PCI-Express Gen5.0转接驱动器进行眼图扫描.pdf》资料免费下载

发表于 08-31 10:12

?0次下载

LMK6H和LMKDB1xxx PCI Express合规性报告

电子发烧友网站提供《LMK6H和LMKDB1xxx PCI Express合规性报告.pdf》资料免费下载

发表于 08-29 09:47

?0次下载

PCI Express IP设计的过程与仿真介绍

PCI Express IP设计的过程与仿真介绍

评论