十余家ADAS设计和自动驾驶芯片公司已在FinFET工艺中采用DesignWare IP

重点:

基于7nm工艺技术的控制器和PHY IP具有丰富的产品组合,包括LPDDR4X、MIPI CSI-2、D-PHY、PCI Express 4.0以及安全IP。

IP解决方案支持TSMC 7nm工艺技术所需的先进汽车设计规则,满足可靠性和15年汽车运行要求。

ISO 26262 ASIL Ready IP包含安全包、FMEDA报告及安全手册,以加速芯片功能安全评估。

2018年10月18日,中国 北京——新思科技(Synopsys, Inc.,纳斯达克股票市场代码: SNPS)宣布,推出支持TSMC 7nm FinFET工艺技术的汽车级DesignWare?Controller和PHY IP。DesignWare LPDDR4x、MIPI CSI-2、D-PHY、PCI Express 4.0以及安全IP在TSMC 7nm工艺技术实现了先进的汽车设计规则,以满足ADAS和自动驾驶芯片的可靠性及运行要求。推出此项支持TSMC 7nm工艺技术的汽车级IP进一步扩展了新思科技FinFET工艺的ISO 26262 ASIL Ready IP解决方案的产品组合,并已被十余家领先的汽车厂商所采用。该IP满足严格的AEC-Q100温度要求,为汽车芯片提供高可靠性。此外,新思科技还提供包含故障模式和FMEDA报告的汽车安全包,能够节省设计人员数月的开发时间,并加快芯片安全功能评估。

TSMC设计基础设施市场部高级总监Suk Lee表示:“ TSMC与新思科技多年的成功合作经验有助于共同用户实现芯片在性能、功耗及面积方面的目标。新思科技通过推出支持TSMC 7nm FinFET工艺技术的汽车级DesignWareIP,持续致力于为设计人员提供高质量IP,实现其卓越的设计目标,并加快产品上市时间。”

新思科技IP营销副总裁John Koeter表示:“开发汽车级IP需要大量的专业知识和严苛的工艺要求,确保IP符合严格的ISO 26262功能安全标准和AEC-Q100可靠性标准。新思科技将继续大规模投资、开发支持TSMC 7nm等最先进工艺技术的汽车级IP,帮助设计人员提高芯片的功能安全性、可靠性和汽车质量认证。“

关于新思?

新思科技(Synopsys, Inc.,纳斯达克股票市场代码: SNPS)致力于创新改变世界,在芯片到软件的众多领域,新思科技始终引领技术趋势,与全球科技公司紧密合作,共同开发人们所依赖的电子产品和软件应用。新思科技是全球排名第一的芯片自动化设计解决方案提供商,全球排名第一的芯片接口IP供应商,同时也是信息安全和软件质量的全球领导者。作为半导体、人工智能、汽车电子及软件安全等产业的核心技术驱动者,新思科技的技术一直深刻影响着当前全球五大新兴科技创新应用:智能汽车、物联网、人工智能、云计算和信息安全。

新思科技成立于1986年,总部位于美国硅谷,目前拥有13000多名员工,分布在全球100多个分支机构。2018财年预计营业额31亿美元,拥有3000多项已批准专利,为美国标普500指数成分股龙头企业。

自1995年在中国成立新思科技以来,新思科技已在北京、上海、深圳、厦门、武汉、西安、南京、香港、澳门九大城市设立机构,员工人数超过1100人,建立了完善的技术研发和支持服务体系,秉持“加速创新、推动产业、成就客户”的理念,与产业共同发展,成为中国半导体产业快速发展的优秀伙伴和坚实支撑。新思科技携手合作伙伴共创未来,让明天更有新思!

-

TSMC

+关注

关注

3文章

178浏览量

85547 -

新思科技

+关注

关注

5文章

874浏览量

51670 -

adas

+关注

关注

310文章

2263浏览量

210390 -

7nm工艺

+关注

关注

0文章

39浏览量

8737

发布评论请先 登录

新思科技携手台积公司开启埃米级设计时代

BiCMOS工艺技术解析

Cadence UCIe IP在Samsung Foundry的5nm汽车工艺上实现流片成功

新思科技推出Virtualizer原生运行虚拟仿真技术

聆思科技获得Ceva-Waves Wi-Fi 6 IP授权

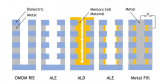

ALD和ALE核心工艺技术对比

新思科技推出超以太网与UALink IP解决方案

安森美推出基于BCD工艺技术的Treo平台

锐成芯微推出基于8nm工艺的PVT Sensor IP

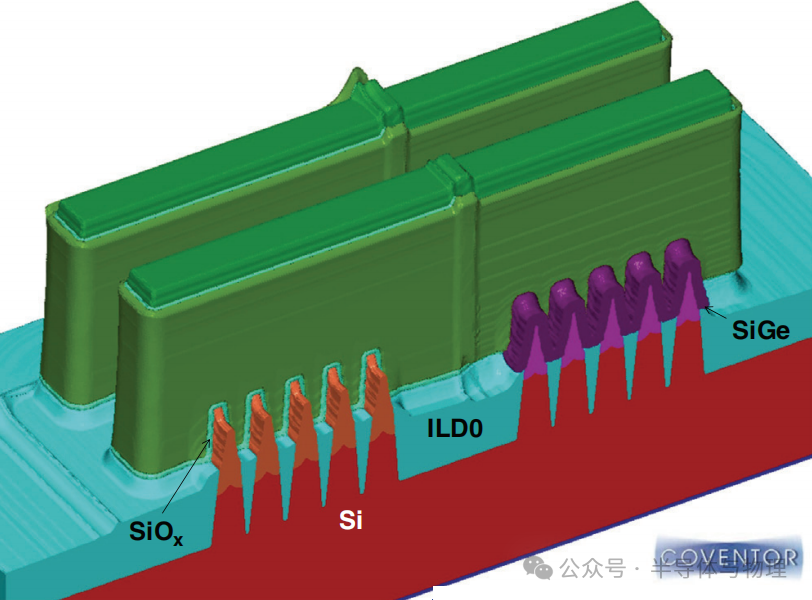

所谓的7nm芯片上没有一个图形是7nm的

新思科技推出基于TSMC 7nm FinFET工艺技术的汽车级IP

新思科技推出基于TSMC 7nm FinFET工艺技术的汽车级IP

评论