CDCL1810A 是一款高性能时钟分配器。可编程分频器 P0 和 P1,对输出频率与输入频率的比值具有很高的灵活性: F 外 = F 在 /P,其中 P (P0,P1) = 1, 2, 4, 5, 8, 10, 16, 20, 32, 40, 80.

该CDCL1810A支持一个差分LVDS时钟输入和总共10个差分 CML 输出。如果 CML 输出是交流耦合的,则与 LVDS 接收器兼容。

*附件:cdcl1810a.pdf

通过仔细观察输入电压摆幅和共模电压限制,该 CDCL1810A可以支持单端时钟输入,如引脚配置和功能中所述。

所有器件设置均可通过SDA/SCL串行双线接口进行编程。 串行接口为1.8V 仅宽容。

该器件在 1.8V 电源环境中工作,其特点是工作温度范围为 –40°C 至 +85°C。 该CDCL1810A采用48引脚QFN (RGZ)封装。

特性

- 其他1.8 V单电源

- 具有 10 个输出的高性能时钟分配器

- 低输入输出附加抖动:低至 10fs RMS

- 低压差分信号 (LVDS) 输入,100Ω

差分片上终端,频率高达 650 MHz - 差分电流模式逻辑 (CML) 输出,50Ω

单端片上端接,频率高达 650 MHz - 两组,每组五个输出,每个输出具有独立的频

分比 - 输出频率以 1、2、4、5、

8、10、16、20、32、40 和 80 的分压比导出 - 符合 ANSI TIA/EIA-644-A-2001 LVDS 标准要求

- 功耗:410 mW(典型值)

- 每个输出的输出使能控制

- SDA/SCL 设备管理接口

- 48引脚VQFN (RGZ)封装

- 工业温度范围:–40°C 至 +85°C

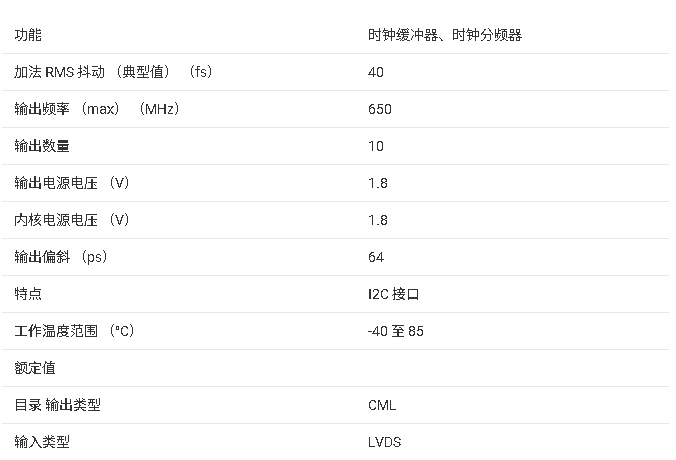

参数

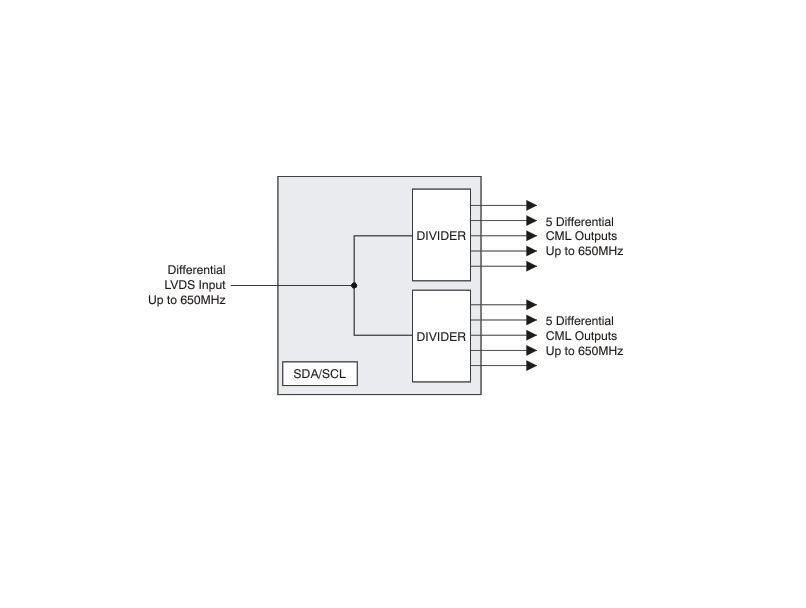

方框图

?1. 产品概述?

CDCL1810A是德州仪器(TI)推出的1.8V供电、10路输出的高性能时钟分配器,专为高速串行通信系统设计。其核心特点包括:

- ?低抖动性能?:输入至输出附加抖动低至10fs RMS(12kHz-5MHz频偏)。

- ?灵活分频?:支持两组独立分频(P0/P1),分频比1/2/4/5/8/10/16/20/32/40/80可编程。

- ?接口兼容性?:支持LVDS输入(最高650MHz)和CML输出(兼容AC耦合LVDS接收器)。

?2. 关键特性?

- ?电气参数?:

- ?封装?:48引脚VQFN(7mm×7mm),需焊接散热焊盘至地以优化性能。

?3. 应用场景?

?4. 功能模块?

- ?输入?:单路差分LVDS,支持单端DC耦合(需符合引脚配置限制)。

- ?输出?:10路差分CML,分两组独立控制(YP[4:0]和YP[9:5]),每组支持独立分频和使能。

- ?控制接口?:通过SDA/SCL(I?C兼容)配置分频比、输出使能等,支持4个可选设备地址。

?5. 设计注意事项?

- ?布局建议?:

- 缩短电源去耦电容走线,优先使用0201封装(正面贴装)或0402(背面贴装)。

- 散热焊盘需通过多通孔接地,否则性能可能显著下降。

- ?同步限制?:分频器重编程时,两组输出可能存在相位偏移(分频比>1时需注意)。

?6. 版本与订购信息?

- 提供工业级(-40°C至+85°C)型号:CDCL1810ARGZR(卷带)、CDCL1810ARGZT(小卷带)。

- 与旧版CDCL1810的主要差异:取消输出同步功能,支持输出独立配置而不影响其他通道。

?7. 文档支持?

- 包含完整寄存器映射、时序图、热阻参数及典型应用电路(如多DSP时钟分配方案)。

- 强调静电防护(HBM 2000V/CDM 500V)和焊接工艺要求(回流焊峰值温度260°C)。

该文档为硬件工程师提供了从选型到布板的全面参考,适用于高速时钟网络设计的可靠性验证与实现。

-

接收器

+关注

关注

15文章

2590浏览量

74854 -

分频器

+关注

关注

43文章

509浏览量

51648 -

串行接口

+关注

关注

3文章

422浏览量

44610 -

lvds

+关注

关注

2文章

1151浏览量

68189 -

分配器

+关注

关注

0文章

206浏览量

26609

发布评论请先 登录

音视频/信号分配器,音视频/信号分配器是什么意思

VGA分配器,VGA分配器是什么意思

分配器,什么是分配器

深入剖析SLUB分配器和SLAB分配器的区别

单线分配器与双线分配器的区别是什么

CDCE72010十路输出高性能时钟同步器、抖动消除器和时钟分配器数据表

CDCL1810 1.8V 10路输出高性能时钟分配器数据表

CDCL6010 1.8V 11输出时钟乘法器、分配器、抖动消除器和缓冲器数据表

CDCL1810A 1.8V、10 输出高性能时钟分配器数据表

?CDCL1810A 高性能时钟分配器技术文档总结

?CDCL1810A 高性能时钟分配器技术文档总结

评论