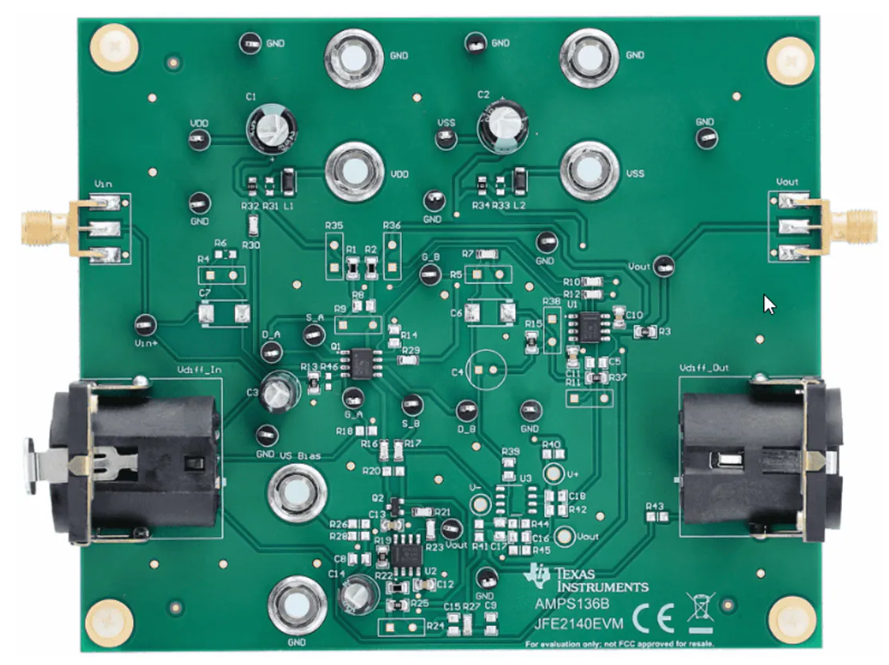

Texas Instruments JFE2140EVM JFET评估模块 (EVM) 设计用于对JFE2140器件进行基本功能评估。JFE2140是一款双通道超低噪声低栅极电流音频N通道JFET。Texas Instruments JFE2140EVM采用闭环前置放大器配置,在±5V分立式电源上提供60dB增益。可以针对各种电路配置对用户进行修改。

数据手册:*附件:Texas Instruments JFE2140EVM JFET评估模块 (EVM)数据手册.pdf

特性

板布局

JFE2140EVM评估模块技术解析:超低噪声JFET前置放大器的设计与应用

产品概述

JFE2140EVM评估模块是德州仪器(TI)推出的一款专为高性能音频和传感器信号调理设计的评估平台,基于JFE2140匹配对离散JFET器件。该模块采用SOIC-8封装,提供完整的超低噪声前置放大器解决方案,特别适合需要极高信噪比的应用场景。

?核心特性?:

- ?超低噪声性能?:0.9nV/√Hz输入参考噪声(5mA偏置时)

- ?灵活偏置调节?:工作电流可调范围50μA至20mA

- ?专业级接口?:SMA和XLR双输入/输出连接方式

- ?多功能测试点?:关键节点均设有测试点便于测量

- ?可扩展设计?:提供电阻/电容焊盘选项用于信号路径优化

评估模块硬件设计

1. 电源架构设计

?供电系统配置?:

- ?默认双电源?:±5V供电(VDD=+5V, VSS=-5V)

- ?关键电源管理?:

- 100nF陶瓷电容(C1,C2)用于高频去耦

- 10μF电解电容(C3,C14)用于低频滤波

- 2.5kΩ电阻(R1,R2)建立偏置电压

?热管理要点?:

- 推荐环境温度:15°C至35°C

- 高偏置电流时需监控Q1(JFE2140)温升

2. 信号路径设计

?输入电路?:

- 交流耦合输入通过10μF电容(C3)

- 1MΩ电阻(R13)设置栅极偏置电压

- SMA接口(J1/J8)和测试点(Vin)并行接入

?输出电路?:

- OPA202运放构成增益级

- 49.9Ω隔离电阻(R3)提升容性负载驱动能力

- 输出电压范围:±2V(相对于中电源电压)

关键电路分析

1. 超低噪声前置放大器

评估模块核心电路为闭环前置放大器:

- ?第一级?:JFE2140构成共源放大器

- ?第二级?:OPA202运放提供主增益

- ?反馈网络?:R37(10kΩ)和R15(10Ω)设定1001V/V增益

- ?尾电流源?:典型值2mA(通过R19/R22设置)

?性能指标?:

- 中频增益:60dB(1000V/V)

- 带宽特性:-3dB带宽约100kHz

- 输入阻抗:1MΩ(由R13决定)

2. PCB布局要点

专业六层板设计:

- ?顶层?:

- 关键信号路径最短化

- 对称差分走线布局

- 电源去耦电容靠近器件引脚

- ?内层?:

- 完整地平面降低噪声

- 电源层分割设计

- 多过孔连接降低阻抗

- ?测试点分布?:

- 20个多功能测试点覆盖所有关键节点

- 黑色TH测试点便于示波器连接

典型应用场景

评估指南

1. 快速启动步骤

- 连接双电源:

- J1.3接+5V,J1.1接-5V

- 最大供电电压±18V

- 信号输入连接:

- 单端模式:J1(SMA IN+),J3接地

- 差分模式:J1/J3差分输入

- 输出测量:

- SMA接口J8或测试点Vout

- 典型输出幅度1Vpp(对应1mVpp输入)

2. 配置建议

- ?增益调整?:修改R37/R15比值

- ?带宽优化?:调整C10-C13电容值

- ?偏置设置?:通过R19/R22调节尾电流

- ?ESD防护?:操作时佩戴防静电手环

-

JFET

+关注

关注

3文章

183浏览量

22963 -

双通道

+关注

关注

5文章

1179浏览量

34655 -

低噪声

+关注

关注

0文章

451浏览量

24017 -

评估模块

+关注

关注

0文章

1504浏览量

8102

发布评论请先 登录

放大器,低噪声前置放大器参数,前置放大器厂家

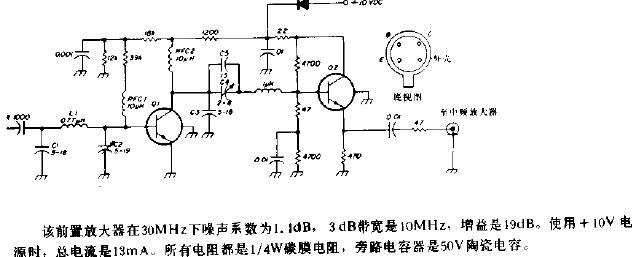

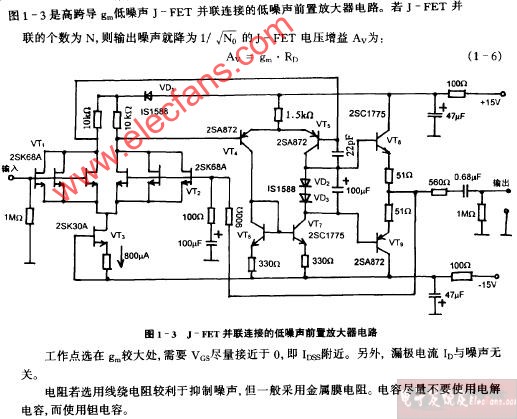

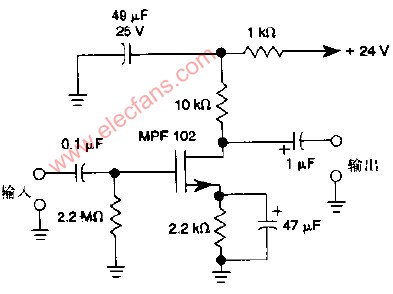

分立元件设计的低噪声前置放大器实用电路

低噪声前置放大器电路的设计方法

低噪声前置放大器电路的设计步骤

前置放大器电路噪声分析

AD8332-EVALZ:双VGA、超低噪声前置放大器和可编程RIN评估板数据表

JFE2140EVM评估模块技术解析:超低噪声JFET前置放大器的设计与应用

JFE2140EVM评估模块技术解析:超低噪声JFET前置放大器的设计与应用

评论