TPIC6A596是一款单片、高压、大电流电源逻辑8位移位寄存器,设计用于需要相对高负载功率的系统。该器件在输出端包含一个内置电压钳位,用于电感瞬态保护。电源驱动器应用包括继电器、螺线管和其他中电流或高压负载。每个漏极开路DMOS晶体管都具有独立的斩波限流电路,以防止短路时损坏。

*附件:tpic6a596.pdf

该器件包含一个 8 位串行输入并行输出移位寄存器,该寄存器为 8 位 D 型存储寄存器供电。数据分别通过移位寄存器时钟(SRCK)和寄存器时钟(RCK)上升沿的移位寄存器和存储寄存器传输。当移位寄存器清除 (SRCLR) 为高电平时,存储寄存器将数据传输到输出缓冲器。写入数据和读取数据仅在 RCK 较低时有效。当SRCLR为低电平时,器件中的所有寄存器都被清除。当输出使能G保持为高电平时,输出缓冲器中的所有数据都保持为低电平,所有漏极输出都关断。当G保持低电平时,来自存储寄存器的数据对输出缓冲器是透明的。串行输出 (SER OUT) 在 SRCK 的下降沿从器件中时钟输出,为级联应用提供额外的保持时间。这将为时钟信号可能偏斜、器件彼此不靠近或系统必须承受电磁干扰的应用提供更高的性能。

输出为低侧漏极开路DMOS晶体管,输出额定值为50V,连续灌电流能力为350mA。当输出缓冲器中的数据为低电平时,DMOS晶体管输出关断。当数据为高电平时,DMOS晶体管输出具有灌电流能力。

提供单独的电源接地 (PGND) 和逻辑接地 (LGND) 端子,以促进最大的系统灵活性。所有PGND端子均内部连接,每个PGND端子必须外部连接到电源系统接地,以尽量减少寄生阻抗。LGND 和 PGND 之间的单点连接必须以减少逻辑和负载电路之间串扰的方式从外部进行。

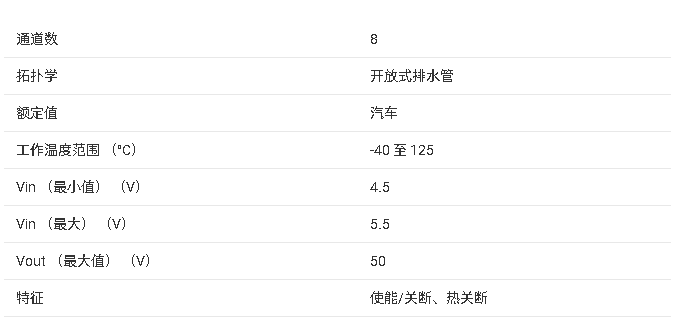

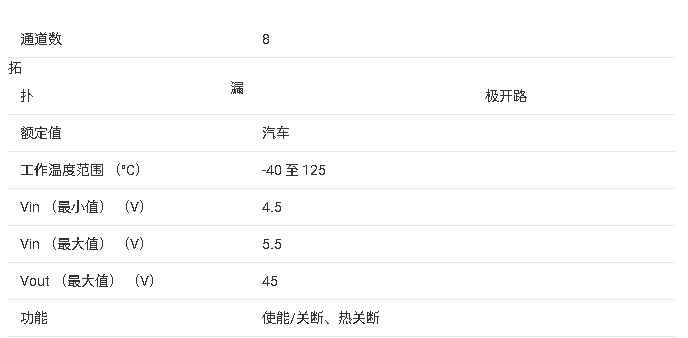

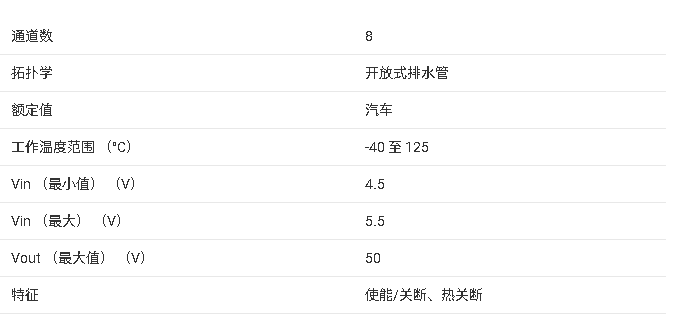

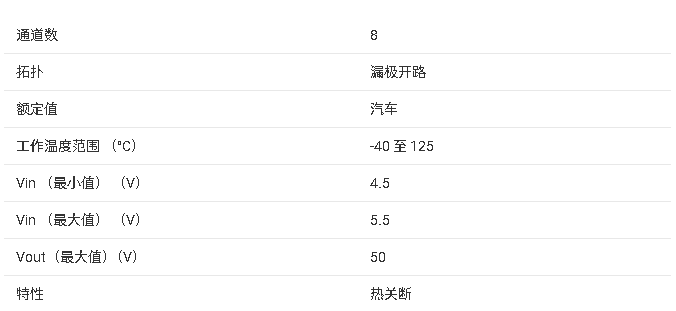

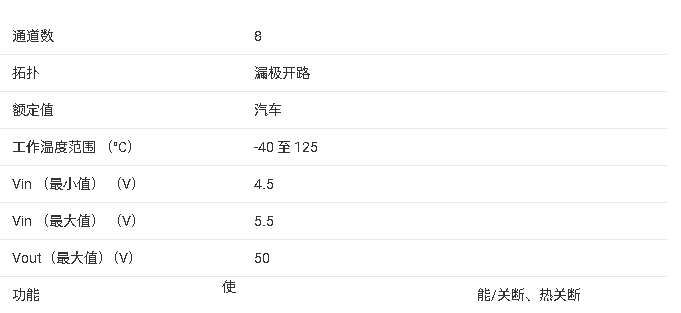

该TPIC6A596采用热增强型双列直插式 (NE) 封装和宽体表面贴装 (DW) 封装。该TPIC6A596的特性是在?40°C至125°C的工作温度范围内工作。

特性

- 低 rDS(on):1Ω(典型值)

- 输出短路保护

- 雪崩能量:75mJ

- 8个350mA DMOS输出

- 50V 开关能力

- 增强多级级联

- 所有寄存器均通过单输入清除

- 低功耗

参数

?1. 核心特性?

- ?低导通电阻?:典型值1Ω,支持高效功率传输

- ?输出保护?:短路保护、75mJ雪崩能量耐受能力

- ?驱动能力?:8路开漏DMOS输出,每路350mA连续灌电流,50V开关耐压

- ?级联优化?:增强型级联设计,支持多级扩展

- ?控制功能?:单输入清除所有寄存器,低功耗设计

?2. 典型应用?

?3. 关键功能描述?

- ?双寄存器结构?:8位串入并出移位寄存器 + 8位D型存储寄存器

- 数据在SRCK上升沿移入移位寄存器

- 在RCK上升沿将数据锁存至存储寄存器

- ?保护机制?:

- 独立电流斩波限流电路防止短路损坏

- 内置电压钳位抑制感性负载瞬态

- ?级联支持?:SEROUT引脚在SRCK下降沿输出数据,优化多器件时序

?4. 电气参数要点?

| 参数 | 条件 | 典型值 |

|---|---|---|

| 工作电压 | Vcc | 4.5-5.5V |

| 导通电阻 | ID=350mA | 1Ω |

| 工作温度 | 全范围 | -40~125°C |

| 时钟频率 | 级联模式 | ≤10MHz |

?5. 封装选项?

- ?PDIP-20? (NE):24.0×6.86mm

- ?SOIC-24? (DW):15.4×7.5mm

?6. 设计注意事项?

- 需单独连接功率地(PGND)与逻辑地(LGND)

- 上电时应通过SRCLR引脚初始化寄存器

- Vcc低于4.5V或高于5.5V时可能影响可靠性

-

继电器

+关注

关注

133文章

5465浏览量

152316 -

电感

+关注

关注

54文章

6222浏览量

104996 -

移位寄存器

+关注

关注

3文章

329浏览量

22868 -

限流电路

+关注

关注

1文章

24浏览量

17809 -

瞬态保护

+关注

关注

1文章

15浏览量

5864

发布评论请先 登录

带低端电源DMOS开关的TPIC6595电源+逻辑8位移位寄存器

?TPIC6A596 8位功率逻辑移位寄存器技术文档总结

?TPIC6A596 8位功率逻辑移位寄存器技术文档总结

评论