文章来源:学习那些事

原文作者:小陈婆婆

在先进封装技术演进中,台积电的InFO(Integrated Fan-Out)平台通过扇出型重布线技术重新定义了芯片级集成的可能性。

InFO-R和 InFO-L

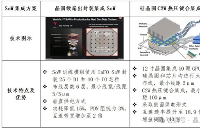

InFO-R作为基础架构,采用"芯片嵌入+RDL成型"的工艺路径。芯片在晶圆级基板上完成精准定位后,通过光刻工艺直接在芯片表面构建多层铜重布线层(RDL),线宽/线距(L/S)可压缩至2μm/2μm级别。这种设计使单块封装即可集成多颗异质芯片(如逻辑、存储、射频模块),并通过扇出型走线实现芯片间横向互连。苹果M系列芯片的封装即采用该技术,在保持12英寸晶圆级尺寸的同时,将APU与LPDDR5内存的互连带宽提升到200GB/s,较传统FCBGA封装提升3倍。值得注意的是,台积电近期公布的InFO-R Gen3工艺已实现RDL层数突破至6层,支持1.6Tbps的SerDes通道集成,为5G基站和数据中心加速器提供了高密度互连解决方案。

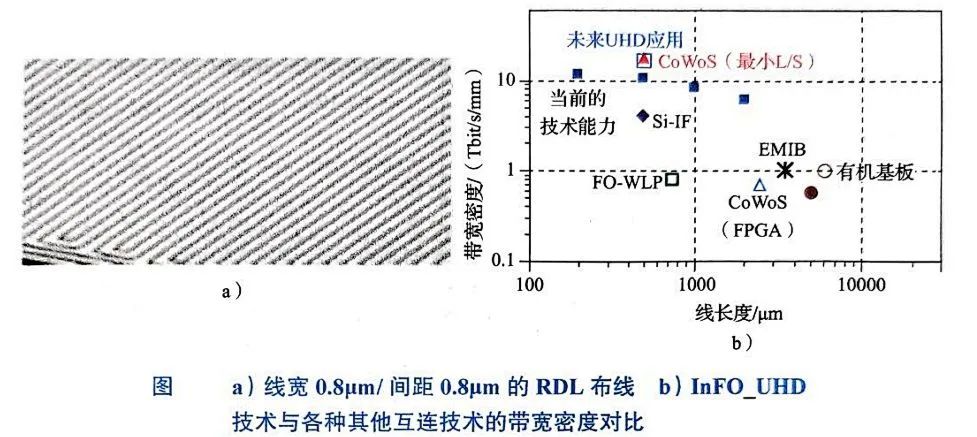

针对局部高密度互连需求,InFO-L平台通过嵌入式LSI(局部硅互连)芯片解决了传统RDL的密度瓶颈。该技术将微型硅桥接片嵌入RDL层中,在特定区域实现亚微米级互连(如0.8μm节距),同时保留扇出工艺的大面积布局优势。英特尔在Meteor Lake处理器中采用的Foveros技术即属此类,其LSI芯片通过预先植入的深沟槽电容(DTC)有效抑制电源噪声,使多芯片系统在150W功耗下仍能维持1.1V的核心电压稳定度。行业动态显示,AMD下一代Zen5架构处理器将采用InFO-L与3D V-Cache技术的混合封装,通过LSI芯片实现三级缓存与计算核心的垂直互连,预计带宽密度将突破300GB/s/mm?。

从技术演进路径看,InFO平台正通过材料创新与工艺解耦持续拓展边界。玻璃基板的应用研究已进入实操阶段,其高平整度与超薄化特性可支持更精密的TSV制造;而RDL层与LSI芯片的协同设计,则推动封装从被动互连向主动功能集成转型。

此外,InFO与SoIC技术的深度融合正在催生新一代3D系统级封装——通过前道键合实现芯片垂直堆叠,再通过扇出型RDL完成横向扩展,这种"立体扇出"架构已在台积电的3DFabric技术路线图中明确标注为2026年量产目标。这些进展共同印证了先进封装技术正在从"连接载体"演变为"系统赋能者",为摩尔定律的延续提供关键支撑。

超高密度互连的InFO封装

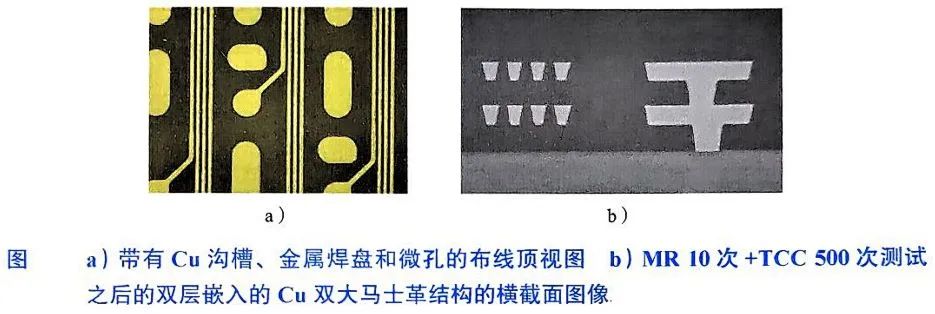

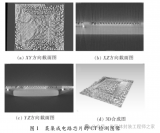

在先进封装技术向亚微米级互连密度突破的进程中,台积电的InFO-UHD(超高密度互连扇出型封装)技术通过工艺创新重新定义了晶圆级封装的性能边界。作为InFO平台的延伸,该技术采用铜双大马士革工艺与液态光敏介质膜结合,在300mm晶圆上实现了线宽/间距(L/S)低至0.8μm/0.8μm的精细布线,单层RDL通过5μm级微孔与2μm/1μm逃逸布线构建多层互连网络。其核心突破在于通过化学机械抛光(CMP)工艺实现铜覆盖层与种子层的精准平坦化,不仅解决了传统半加成工艺(SAP)中铜布线钻蚀与附着力不足的问题,更将介质层厚度均匀性控制在±0.5μm以内,为高频信号传输提供了超低损耗的传输通道。

可靠性验证显示,经10次回流焊+500次温度循环(65~150℃)及96小时无偏压HAST测试后,Cu-介质层界面未出现分层,微孔与焊盘内部亦无裂纹,印证了该工艺在极端环境下的稳定性。信号完整性方面,InFO-UHD通过优化RDL表面粗糙度(低至0.5nm),将50GHz频段下的归一化传输损耗(NTL)控制在传统SAP工艺的70%以下,尤其在差分对设计(GSSG链路)中,通过线宽/间距/高度(L/S/H)的精确调优,有效抑制了电容效应对阻抗匹配的影响。

性能对比数据凸显其技术优势:在逻辑-逻辑集成场景中,双层RDL结构可实现10Tbit/s/mm的带宽密度,较CoWoS平台提升2.5倍;能量效率方面,500μm线长下达到0.061pJ/bit,与硅转接板技术(Si-IF)持平,但线宽仅为后者的40%,且在HBM2存储接口中以0.62pJ/bit的能效超越硅转接板的0.83pJ/bit。值得关注的是,该技术无需依赖半导体晶圆厂的前道制程设备,可基于现有InFO产线升级,显著降低了高端封装的准入门槛。

-

芯片

+关注

关注

460文章

52852浏览量

446351 -

晶圆

+关注

关注

53文章

5240浏览量

130433 -

先进封装

+关注

关注

2文章

488浏览量

719

原文标题:InFO芯片先置集成技术及其封装

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

PCB技术详解:HDI技术实现高密度互连板

探讨高密度小间距LED屏工艺

高密度互连PCB有什么不同的地方

为什么要使用高密度互连?

PCB技术详解:HDI技术实现高密度互连板资料下载

详解超高密度互连的InFO封装技术

详解超高密度互连的InFO封装技术

评论