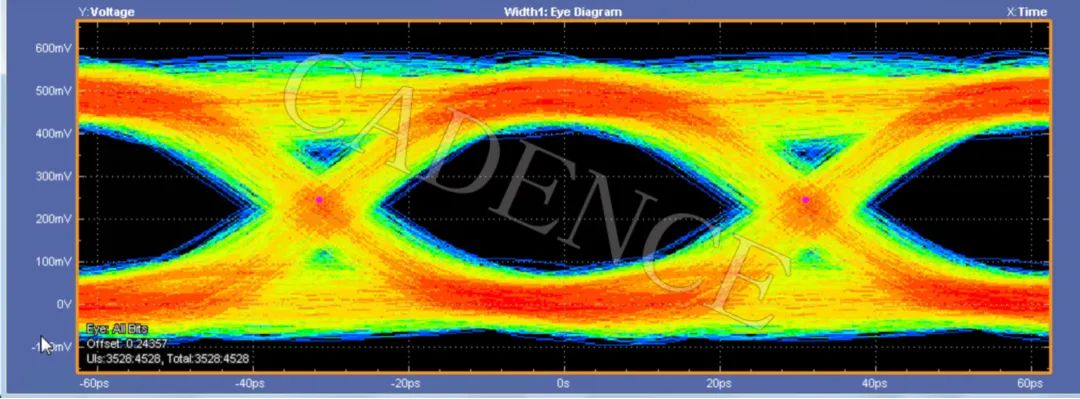

我们很高兴展示基于台积电成熟 N4 工艺打造的Gen1 UCIe IP 的 16GT/s 眼图。该 IP 一次流片成功且眼图清晰开阔,为寻求 Die-to-Die连接的客户再添新选择。

图1:Cadence UCIe IP 的 16GT/s 接收端眼图

UCIe 提供芯片间连接,支持跨技术节点的异构集成。凭借我们经过流片验证的 D2D IP,这一突破为我们共有的客户在多芯片设计实施上提供了更大灵活性。这建立在我们先前展示的 16GT/s IP 成功基础上,其标准和先进的 3nm 封装设计均已被 IEEE 会议收录。

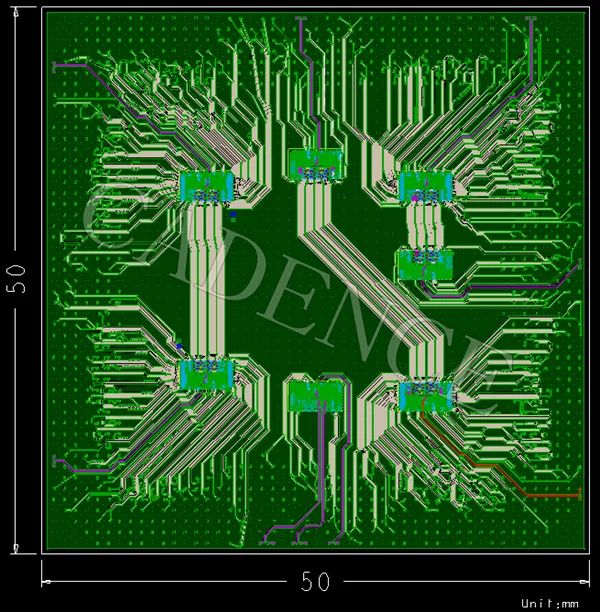

广泛的测试旨在最大限度地覆盖用例,这一直是 Cadence 芯片验证的基石。为此,我们在台积电 N4 工艺上的 UCIe 测试芯片集成了三对(而非一对)芯片间连接,成功演示了跨多种通道长度的数据传输。芯片对间距分别为 5mm、15mm 和 25mm,基板尺寸为 50mm×50mm。

图2:Cadence 采用大尺寸基板设计测试多种通道长度

与所有 UCIe-SP 测试芯片一样,发射端(Tx)眼图也输出至商用示波器,实现对信号质量的实时监测。这进一步证明了设计的稳健性,并让我们能更深入地了解这款低功耗、高速 IP 的性能。

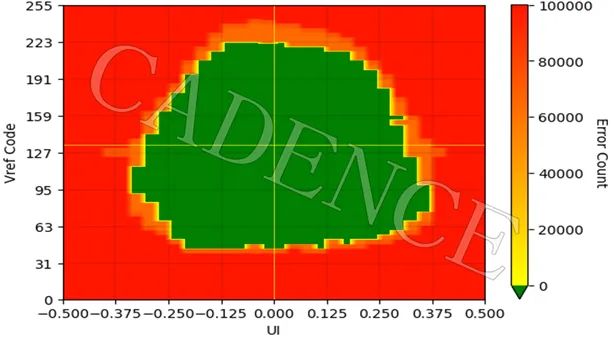

图3:16GT/s 发射端输出眼图

(连接至示波器,PRBS23 码型)

自 2018 年以来,Cadence 一直是高速 D2D 连接领域值得信赖的 IP 合作伙伴。此次最新的 16GT/s UCIe 流片演示延续了我们的征程。

欢迎联系我们,一起探讨 Cadence 丰富的 D2D 经验及广泛的芯片间连接 IP 组合如何助力加速您的分解式设计。

-

台积电

+关注

关注

44文章

5765浏览量

170757 -

Cadence

+关注

关注

67文章

987浏览量

144878 -

眼图

+关注

关注

1文章

72浏览量

21476

原文标题:硅片一次性成功:Cadence 基于台积电 N4 工艺交付 16GT/s UCIe Gen1 IP

文章出处:【微信号:gh_fca7f1c2678a,微信公众号:Cadence楷登】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Cadence携手台积公司,推出经过其A16和N2P工艺技术认证的设计解决方案,推动 AI 和 3D-IC芯片设计发展

小米玄戒O1、联发科天玑9400e与高通骁龙8s Gen4的全面对比分析

Cadence推出DDR5 12.8Gbps MRDIMM Gen2内存IP系统解决方案

西门子与台积电合作推动半导体设计与集成创新 包括台积电N3P N3C A14技术

Cadence UCIe IP在Samsung Foundry的5nm汽车工艺上实现流片成功

高通AR1 Gen1芯片详细介绍和应用案例

Cadence基于台积电N4工艺交付16GT/s UCIe Gen1 IP

Cadence基于台积电N4工艺交付16GT/s UCIe Gen1 IP

评论