文章来源:老虎说芯

原文作者:老虎说芯

本文主要讲述晶圆制造中的Die是什么。

1. 什么是Die?(What is a Die?)

简单来说,Die(发音为/da?/,中文常称为裸片、裸晶、晶粒或晶片)是指从一整片圆形硅晶圆(Wafer)上,通过精密切割(Dicing)工艺分离下来的、单个含有完整集成电路(IC)功能的小方块。

你可以把它想象成:

晶圆 (Wafer)是一张印满了邮票的大版纸。

Die (晶粒)就是从这张大版纸上撕下来的那一枚枚独立的邮票。

每一片Die都是一个未经封装的、功能齐全的电路单元,比如一个CPU核心、一个GPU核心、一个存储器模块或一个射频收发器。

关键点:

形态:通常是正方形或矩形,非常薄,表面有极其复杂的电路结构。

材质:主要由高纯度单晶硅制成。

状态:这是未封装(Unpackaged)的状态。它非常脆弱,直接暴露在空气中容易受到污染和物理损伤。

单复数:它的单数是Die,复数是Dice或Dies。

2. Die的生命周期:从晶圆到芯片 (The Lifecycle of a Die)

要理解Die,最好的方式是了解它在整个生产流程中的位置。

第1步:晶圆制造 (Wafer Fabrication)

一切始于一块高纯度的硅晶圆(Wafer)。

在超净间(Cleanroom)里,通过光刻(Photolithography)、蚀刻(Etching)、薄膜沉积(Deposition)、离子注入(Ion Implantation)等数百道复杂工序,在晶圆表面制作出成千上万个完全相同的电路结构。

此时,所有的Die还都连在一起,共同存在于晶圆之上,形成一个网格状阵列(Array)。

第2步:晶圆测试 (Wafer Probing / CP Test)

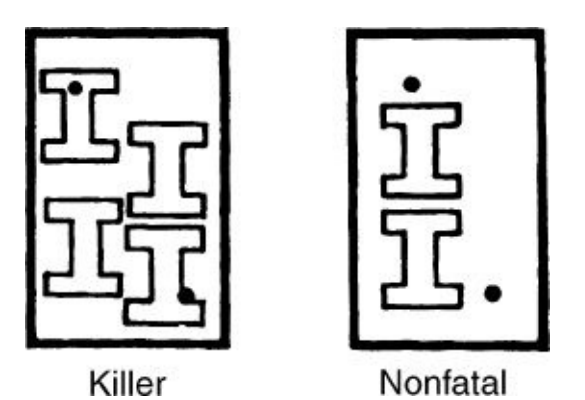

在切割之前,需要对晶圆上的每一个Die进行初步的电性测试。

这个过程叫做晶圆探针测试(Circuit Probing, 简称CP测试)。探针卡(Probe Card)上的细小探针会接触到每个Die上的焊盘(Bond Pad),以检测其功能是否正常。

测试不合格的Die会被标记下来(传统上是点上墨点,现在通常是在电子地图Wafer Map中记录),在后续工序中被废弃。这个步骤是为了尽早剔除次品,避免在无用的Die上浪费后续的封装成本。

第3步:晶圆切割 (Wafer Dicing)

通过CP测试的晶圆会被送到切割机(Dicing Saw)上。

高速旋转的钻石切割刀会沿着Die之间的**切割道(Scribe Line)**进行精确切割,将一整片晶圆分离成数千个独立的Die。

第4步:芯片封装 (Packaging / Assembly)

从晶圆上取下的合格Die(此时称为Good Die),会被送入封装流程。

a. 固晶 (Die Attach):将Die的背面粘贴到封装基板(Substrate)或引线框架(Leadframe)上。

b. 引线键合 (Wire Bonding / Flip-Chip):建立Die与外部世界的电气连接。

引线键合 (Wire Bonding):用极细的金线或铜线,将Die上的焊盘(Bond Pad)连接到基板或引脚上。

倒装焊 (Flip-Chip):Die的正面(有电路的一面)直接朝下,通过其上的焊球(Solder Bump)直接连接到基板上。这种方式路径更短,性能更好,是高性能芯片的主流选择。

c. 塑封 (Molding):用环氧树脂(Epoxy)将Die、引线等所有内部结构包裹起来,形成我们常见的黑色“芯片”外观。这起到了保护内部Die、散热和方便安装的作用。

经过封装后,脆弱的Die就变成了坚固耐用的芯片(Chip)或IC,可以焊接到PCB板上使用了。

3. 为什么Die的概念对工程师如此重要?

不同领域的工程师关注Die的不同方面,它是连接设计和制造的桥梁。

对于IC设计工程师 (Design Engineer):

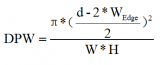

Die Size (晶粒面积)是成本的决定性因素。Die越小,一片晶圆上能生产出的Die就越多(Gross Die per Wafer),单个Die的成本就越低。因此,在满足性能的前提下,优化布局布线以缩小Die Size是设计的核心目标之一。

焊盘布局 (Pad Layout)直接影响到后续的封装方案和信号完整性。

对于工艺/制造工程师 (Process/Manufacturing Engineer):

良率 (Yield)是他们的生命线。良率 = (一片晶圆上合格的Die数量) / (总Die数量)。他们致力于通过优化生产工艺,减少缺陷,提高每一个Die的功能完好率。

对于封装工程师 (Packaging Engineer):

Die是他们工作的起点。他们需要根据Die的尺寸、厚度、焊盘位置、功耗(散热需求)来设计最合适的封装方案,确保电气性能、散热性能和可靠性。

对于测试工程师 (Test Engineer):

他们需要针对Die的功能编写测试程序,无论是在切割前的CP测试,还是封装后的成品测试(Final Test, FT),都是为了确保Die的功能符合设计规范。

总而言之,Die是半导体价值链的绝对核心。它是在硅晶圆上制造的、包含完整电路功能的、未经封装的裸露芯片。

它是设计的画布:承载着电路设计的智慧。

它是制造的成果:体现了半导体工艺的极限。

它是成本的基石:其面积和良率直接决定了最终产品的价格。

它是性能的源泉:芯片的所有计算和处理能力都源于这块小小的硅片。

-

芯片

+关注

关注

460文章

52771浏览量

444681 -

晶圆制造

+关注

关注

7文章

298浏览量

24754 -

晶粒

+关注

关注

0文章

30浏览量

3961

原文标题:深入理解晶圆制造中的Die

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

晶圆制造中的T/R的概念、意义及优化

为什么晶圆是圆的?芯片是方的?

晶圆制造中的Die是什么

晶圆制造中的Die是什么

评论