现有的晶体管都是基于 PN 结或肖特基势垒结而构建的。在未来的几年里,随着CMOS制造技术的进步,器件的沟道长度将小于 10nm。在这么短的距离内,为使器件能够工作,将采用非常高的掺杂浓度梯度。进入纳米领域,常规 CMOS 器件所面临的许多问题都与PN结相关。传统的按比例缩小将不再继续通过制造更小的晶体管而达到器件性能的提高。半导体工业界正努力从器件几何形状、结构以及材料方面寻求新的解决方案。无结场效应器件有可能成为适用于 10nm及以下技术节点乃至按比例缩小的终极器件。无结场效应晶体管与传统反型模式 MOS晶体管或其他结型晶体管相比有以下优点:①它们与常规CMOS工艺兼容、易于制作;②它们没有源漏PN 结;③短沟道效应大为减弱;④由于避开了半导体/栅绝缘层粗糙界面对载流子的散射,载流子受到界面散射影响有限,迁移率不会降低;⑤由于避开了粗糙表面对载流子的散射,器件具备优异的抗噪声能力;⑥放宽了对降低栅极介电层厚度的严格要求;⑦无结场效应晶体管属于多数载流子导电器件,靠近漏极的电场强度比常规反型沟道的MOS 晶体管要低,因此,器件的性能及可靠性得以提高。一些取代硅作为候选沟道材料(包括锗硅、锗、III-V 族化合物半导体、碳纳米管、石墨烯以及 MoS2等二维材料)在积极的探索与研究当中,甚至真空沟道也在考虑之列。这一新领域有望突破摩尔定律的藩禽,改变微电子学的面貌。新的后 CMOS 器件需要集成这些异质半导体或其他高迁移率沟道材料在硅衬底上。集成电路器件工艺与材料学家和工程师们要紧密合作,共同迎接未来新的挑战。

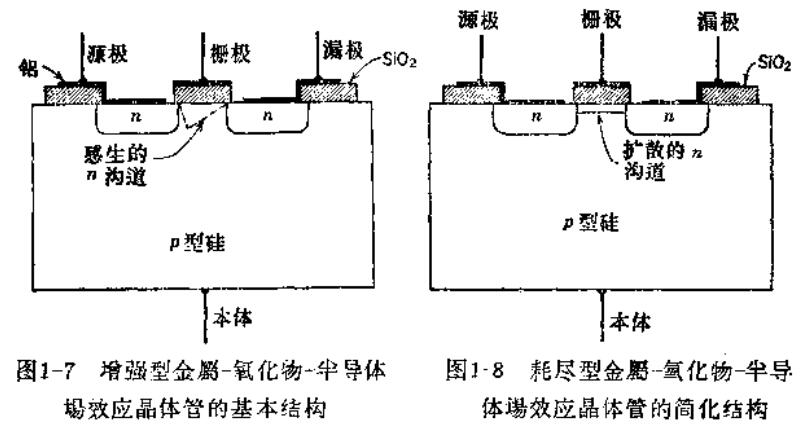

常规的 CMOS 晶体管,从源区至沟道和漏区由两个背靠背的PN 结组成,沟道的掺杂类型与其漏极与源极相反。当足够大的电位差施于栅极与源极之间时,电场会在栅氧化层下方的半导体表面感应少子电荷,形成反型沟道;这时沟道的导电类型与其漏极与源极相同。沟道形成后,MOSFET 即可让电流通过,器件工作于反型模式(IM)。由于栅氧化层与半导体沟道界面的不完整性,载流子受到散射,导致迁移率下降及可靠性降低。进一步地,伴随 MOS 器件特征尺寸持续不断地按比例缩小,基于PN结的 MOS 场效应晶体管结构弊端也越来越明显。通常需要将一个掺杂浓度为1×1019cm-3的N 型半导体在几纳米范围内转变为浓度为1X1018cm-3的P型半导体,采用这样超陡峭掺杂浓度梯度是为了避免源漏穿通造成漏电。而这样设计的器件将严重限制器件工艺的热预算。由于掺杂原子的统计分布以及在一定温度下掺杂原子扩散的自然属性,在纳米尺度范围内制作这样超陡峭的 PN结变得极困难,造成晶体管阈值电压下降,漏电严重,甚至无法关闭。这是未来半导体制造业难以逾越的障碍。

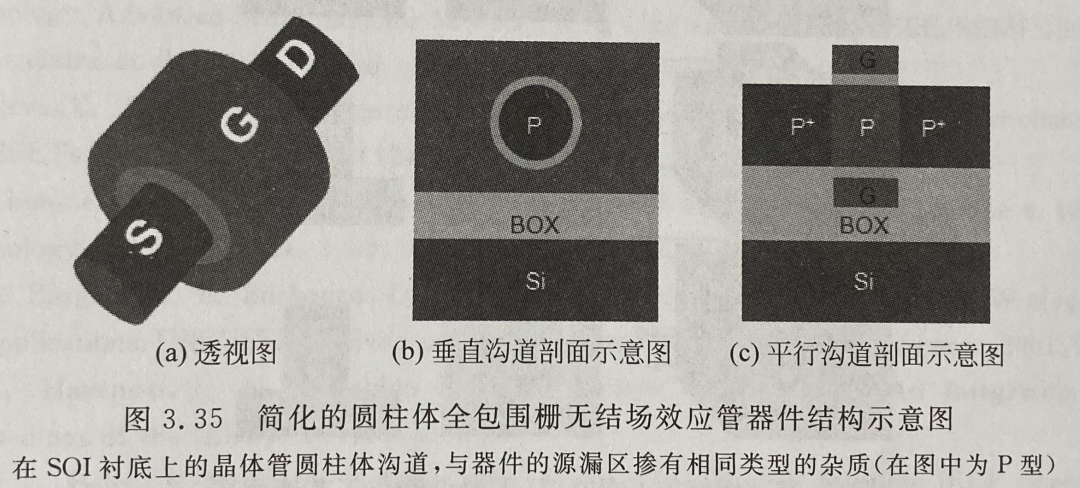

为克服由PN结所构成器件在纳米尺度所面临的障碍,2005年,中芯国际的肖德元等人首次提出一种圆柱体全包围栅无结场效应晶体管(Gate-All-Around-Cylindrical Junctionless Field Effect Transistor, GAACJLT)及其制作方法,它属于多数载流子导电器件。与传统的MOSFET 不同,无结场效应晶体管(JLT)由源区、沟道、漏区,栅氧化层及栅极组成,从源区至沟道和漏区,其杂质掺杂类型相同,没有 PN 结,属于多数载流子导电的器件。图3.35描绘了这种简化了的圆柱体全包围栅无结场效应晶体管器件的结构透视图和沿沟道及垂直于沟道方向的器件剖面示意图。在SOI 衬底上晶体管有一个圆柱体的单晶硅沟道,它与器件的源漏区掺杂类型相同(在图中为P型)。绝缘体栅介质将整个圆柱体沟道包裹起来,在其上面又包裹金属栅。导电沟道与金属栅之间被绝缘体介质隔离,沟道内的多数载流子(空穴)在圆柱体沟道体内而非表面由源极达到漏极。通过栅极偏置电压使器件沟道内的多数载流子累积或耗尽,可以调制沟道电导进而控制沟道电流。当栅极偏置电压大到将圆柱体沟道靠近漏极某一截面处的空穴完全耗尽掉,在这种情况下,器件沟道电阻变成准无限大,器件处于关闭状态。由于栅极偏置电压可以从360°方向将圆柱体沟道空穴由表及里将其耗尽,这样大大增强了栅极对圆柱体沟道的控制能力,有效地降低了器件的阈值电压。由于避开了不完整的栅氧化层与半导体沟道界面,载流子受到界面散射影响有限,提高了载流子迁移率。此外,无结场效应晶体管属于多数载流子导电器件,沿沟道方向,靠近漏极的电场强度比常规反型沟道的MOS 晶体管要来得低,器件的性能及可靠性得以大大提高。

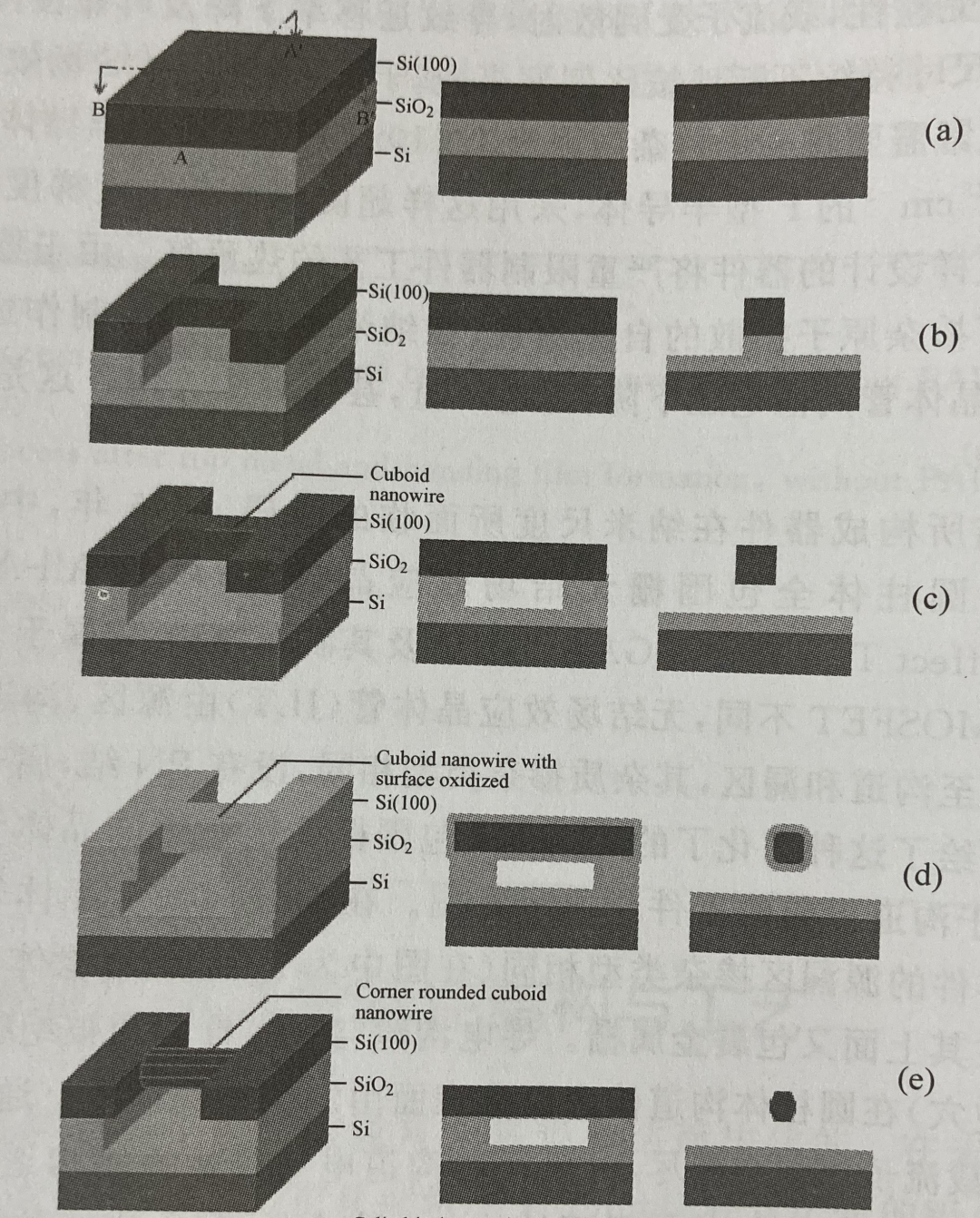

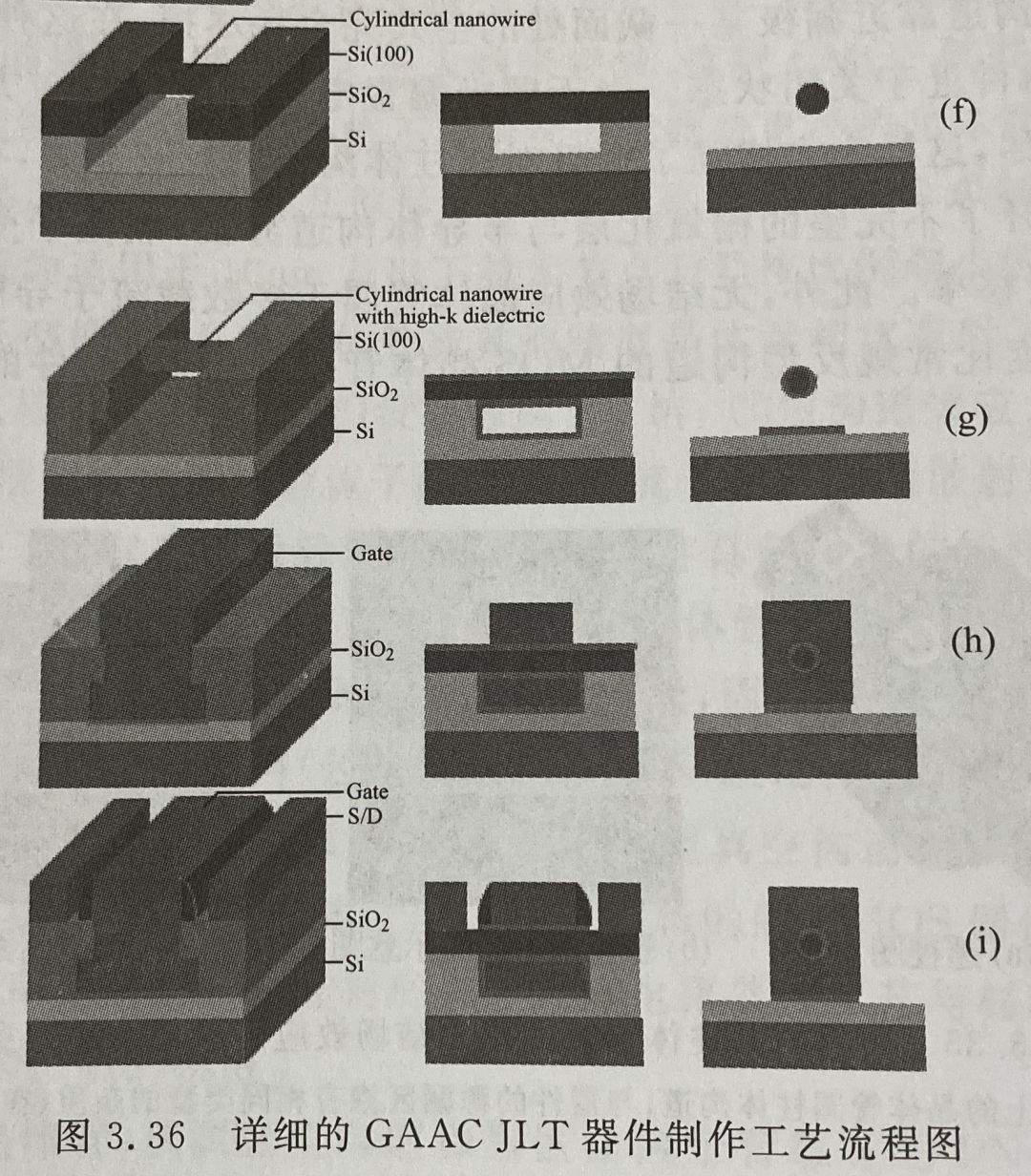

我们发展了一种栅极将圆柱体沟道全部包围的GAAC JLT 全新制作工艺,如图3.36所示。首先,在SOI衬底上对N型与P型沟道分别进行沟道离子注入掺杂,经光刻图形化,刻蚀半导体硅材料层和部分埋入电介质层(BOX),形成半导体材料柱和电介质支撑柱;接下来,使用缓冲氧化物蚀刻剂(BOE)进行埋入电介质层横向蚀刻工艺以选择性地去除显露的底切部分氧化物使电介质支撑柱的中段形成镂空,形成接近立方体形状的硅纳米桥;经多次氧化与氧化物去除将其圆角化处理,最后在氢气氛围下进行高温退火,形成圆柱体硅纳米线桥;接下来,在衬底上沉积栅介质层及金属层将中段镂空处圆柱体硅纳米线全部包裹;经光刻,刻蚀金属层形成金属栅极;形成绝缘体介质侧墙结构,对圆柱体硅纳米线两端的暴露部分进行与器件沟道掺杂类型相同的离子注入重掺杂,形成源区和漏区,最后源漏区形成镍硅化物以降低接触电阻。

无结全包围圆柱形沟道栅晶体管,载流子由源极流经整个圆柱体半导体沟道体内流向漏极,避开了栅氧化层与半导体沟道界面的不完整性,载流子不易受到界面散射的影响,通常其低频噪音比传统 MOSFET低五个数量级。在施加热载流子应力后,器件表现出很低的ION退化,具有更高的使用寿命,这归功于载流子流经纳米线的中心以及邻近漏极一侧位置的电场峰值下降。器件具备更高的性能和可靠性以及更强的按比例缩小能力。此外,无结圆柱体全包围栅场效应晶体管与传统的CMOS 工艺兼容性较好且极大地简化了器件制造工艺,适合于10nm 及以下技术节点CMOS大规模集成电路的生产制造。

-

CMOS

+关注

关注

58文章

6035浏览量

239166 -

MOSFET

+关注

关注

150文章

8686浏览量

221119 -

晶体管

+关注

关注

77文章

10029浏览量

142171

原文标题:无结场效应晶体管器件结构与工艺----纳米集成电路制造工艺 张汝京等 编著

文章出处:【微信号:Semi Connect,微信公众号:Semi Connect】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

场效应晶体管

一文让你秒懂场效应晶体管的所有参数

MOS管与场效应晶体管背后的联系,看完后就全明白了

场效应晶体管的选用经验分享

MOSFET和鳍式场效应晶体管的不同器件配置及其演变

什么是鳍式场效应晶体管?鳍式场效应晶体管有哪些优缺点?

什么是场效应晶体管

如何进行场效应晶体管的分类和使用

无结场效应晶体管器件结构与工艺

无结场效应晶体管器件结构与工艺

评论