来源:芯系半导体

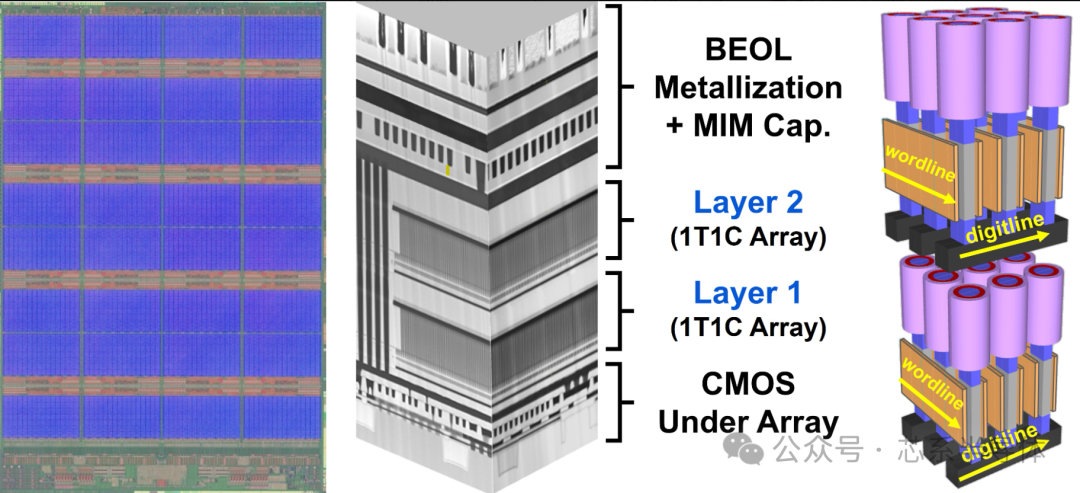

使用直接晶圆到晶圆键合来垂直堆叠芯片,可以将信号延迟降到可忽略的水平,从而实现更小、更薄的封装,同时有助于提高内存/处理器的速度并降低功耗。目前,晶圆堆叠和芯片到晶圆混合键合的实施竞争异常激烈,这被视为堆叠逻辑与内存、3D NAND,甚至可能在高带宽存储(HBM)中的多层DRAM堆叠的关键技术。垂直堆叠使得芯片制造商能够将互连间距从35?m的铜微凸点提升到10?m甚至更小。

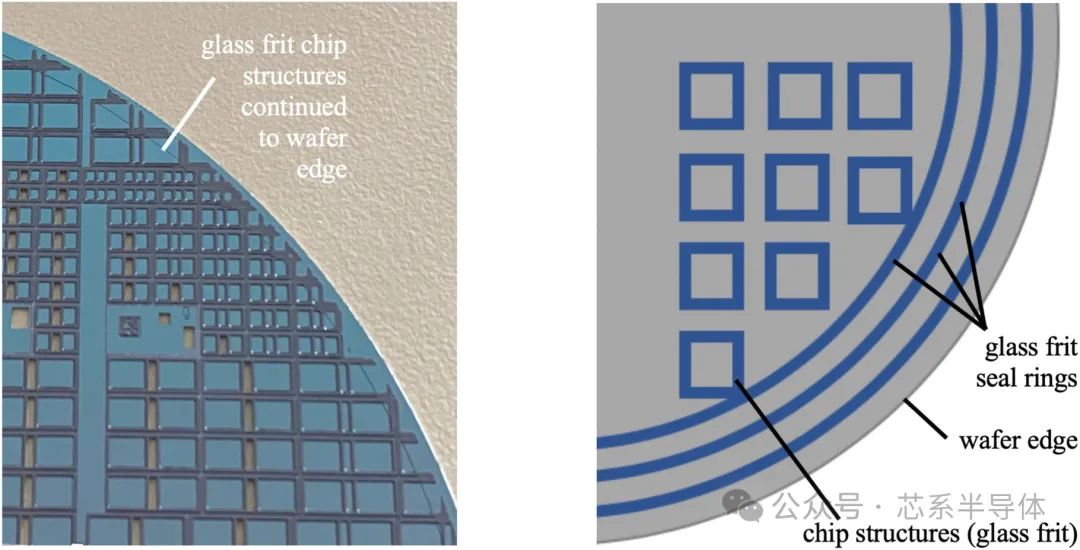

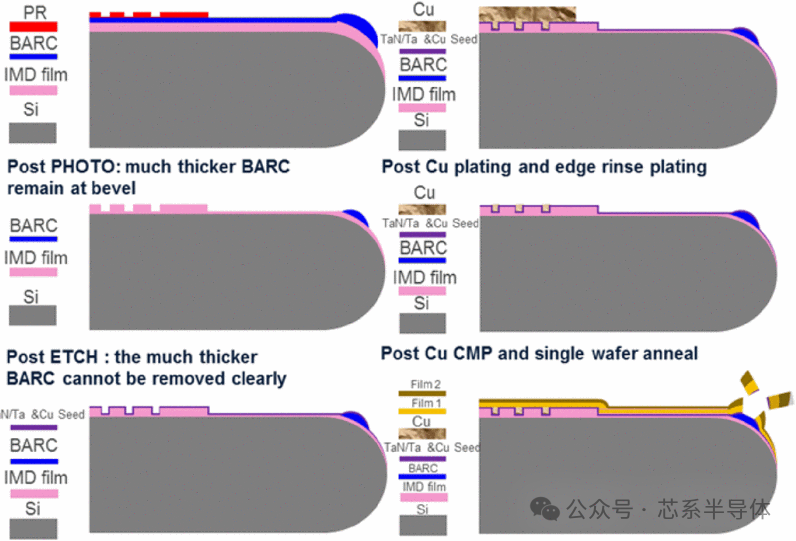

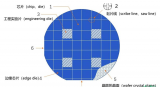

然而,垂直堆叠也伴随着成本问题,这使得芯片制造商急于寻找减少晶圆边缘缺陷的方法。这些缺陷显著影响了晶圆上所有芯片的良率,而晶圆键合需要极为平坦、无缺陷的300mm晶圆。为了更好地控制整个晶圆加工过程中的晶圆边缘缺陷,以及在融合和混合键合过程中,工程师们正在微调新旧工艺。这些工艺包括一系列技术,涉及晶圆边缘的湿法和干法蚀刻、化学机械抛光(CMP)、边缘沉积和边缘修整步骤。

性能和功率效率的提升是显著的,先进封装正在通过芯片堆叠实现更高的处理速度和能力,将内存更接近CPU和GPU,将信息传输的线路缩短,从而加速计算。数据传输仍然占据芯片成本的很大一部分,通常需要进行几十到几百次内存访问,也许你只有两到四个周期来获取你需要的值。系统如果能将内存更靠近处理器,将大大提升性能。而且,通过垂直堆叠发送信号,相比将信号从芯片传输到外部内存再返回的长距离传输,能显著节省能量消耗。

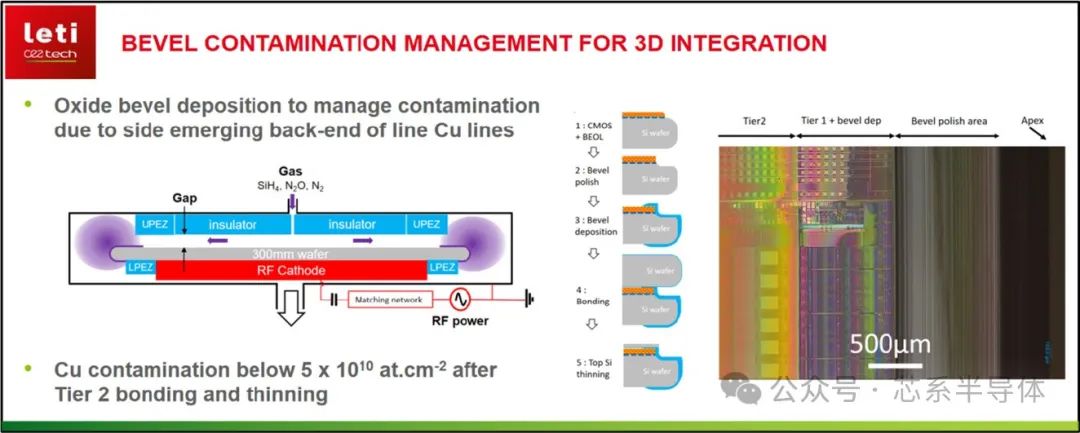

工艺也在针对先进封装的特定需求进行优化。例如,Lam Research与其合作伙伴CEA-Leti优化了一种面向先进封装应用的边缘沉积工艺,该工艺已于去年推出。在晶圆薄化之前,对键合晶圆的边缘进行沉积,可以提供增强支撑。这些结构需要材料来填补边缘的空隙,因此沉积的薄膜作为支撑层起作用。否则,在CMP过程中,由于去除速度在边缘更快,设备晶圆可能会在边缘发生开裂,导致形成缺口,这种缺口最终可能导致晶圆间隙接近零。如果没有边缘沉积,晶圆在薄化过程中可能会发生边缘开裂,严重影响良率。

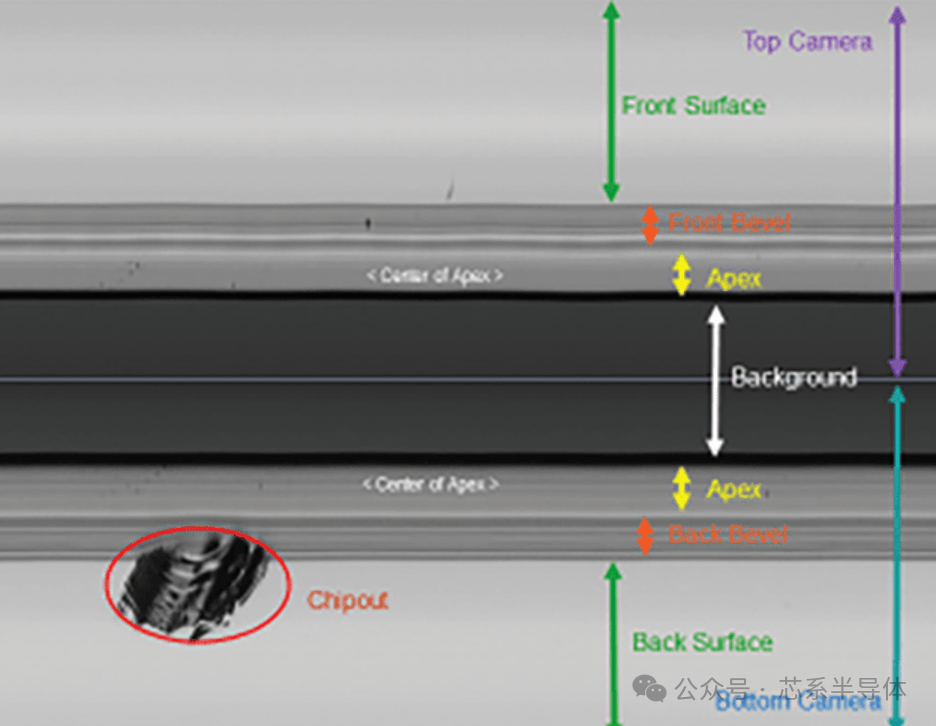

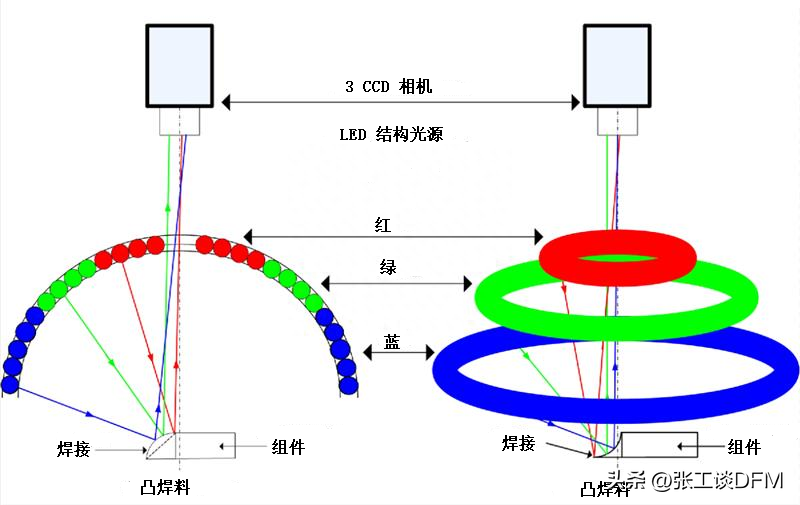

使用基于人工智能的先进工艺控制(APC)软件,工程师可以提高整个晶圆以及堆叠中晶圆之间的均匀性分析。 APC涵盖等离子体限制、薄膜均匀性、光刻工艺的均匀性等方面的分析 。准备进行混合键合的晶圆必须满足严格的工艺规格,以确保高良率的混合键合,例如极为平坦(<1nm的中心到边缘非均匀性)、无颗粒的晶圆、出色的晶圆/晶圆或芯片/晶圆对准、<200nm的芯片放置精度等。晶圆边缘缺陷包括颗粒、崩边、划痕、薄膜剥离、晶圆处理过程中造成的损伤,这些缺陷可能会脱落并成为影响产品良率的缺陷。

CMP挑战

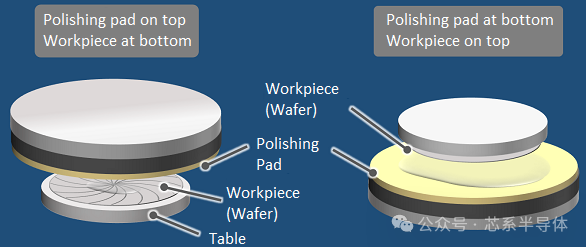

CMP(化学机械平坦化)最早由IBM在1980年代末期为引入铜大马士革互连技术而开发,它为平整化晶圆并在更薄的封装中增加更多功能提供了巨大的支持。晶圆平整度、控制边缘滚落以及减少颗粒是CMP的关键目标。如今,除了在平整化浅沟槽隔离、介电材料和BEOL互连中的铜时使用外,晶圆研磨和CMP还在优化过程中被用于在键合后显著薄化300mm硅晶圆的背面。

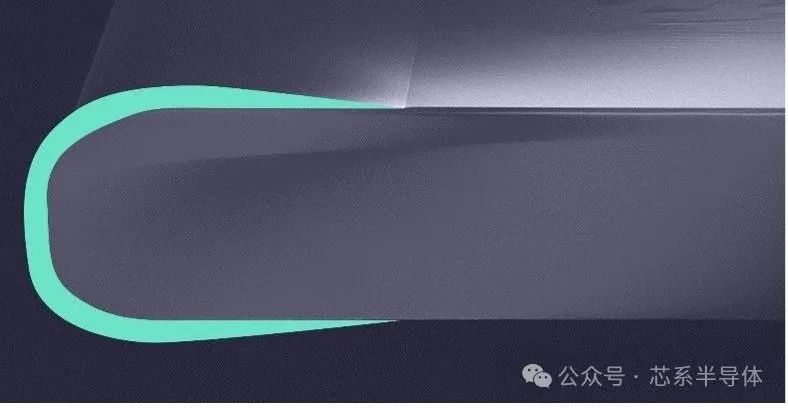

器件晶圆的质量也取决于起始硅的质量,晶圆边缘的处理一直是一个问题。因为边缘没有邻近材料,所以会发生不连续性或突变,改变了这些区域的物理特性。在裸硅晶圆的抛光过程中已经采取了一些措施来弥补这种变化,例如使用保持环。在这个CMP过程中,保持环支持晶圆在抛光夹具中,而晶圆边缘仅与保持环接触的部分非常小,裸硅晶圆边缘本质上被塑造成三个部分——一个锥形部分、更钝的边缘,再一个锥形部分,这被证明是理想的设计,有助于提高CMP性能,相比之下,圆形边缘的效果较差。

通量对所有晶圆工艺至关重要,如果CMP操作过快,就会引入非均匀性,并且有更高的机械损伤风险。因此,必须在最大化去除速率和保持均匀性、缺陷控制之间找到一个非常微妙的平衡。CMP设备供应商,如应用材料(Applied Materials)、江森自控技术(Ebara Technologies)和Axus Technology,与垫片和化学液体供应商一起,针对每个应用优化晶圆和晶圆间的均匀性,为目标工艺应用设计整个方案(化学试剂、抛光片、修整盘、P-CMP清洁剂)。

化学和机械工程师会考虑化学试剂、抛光片、修整盘的组合,控制CMP垫片的各种特性,包括刚性或硬度。颗粒的大小、分布和组成极为重要,因为这些特性部分决定了去除速率在晶圆之间的变化情况,表面图案工程和优化的抛光垫技术也被采用,同时还会使用实时传感和反馈技术,以便用户在CMP过程中及时调整并进行修正。CMP和湿法/干法蚀刻工艺都在专用设备上优化,以去除晶圆边缘的缺陷。

干法与湿法刻蚀

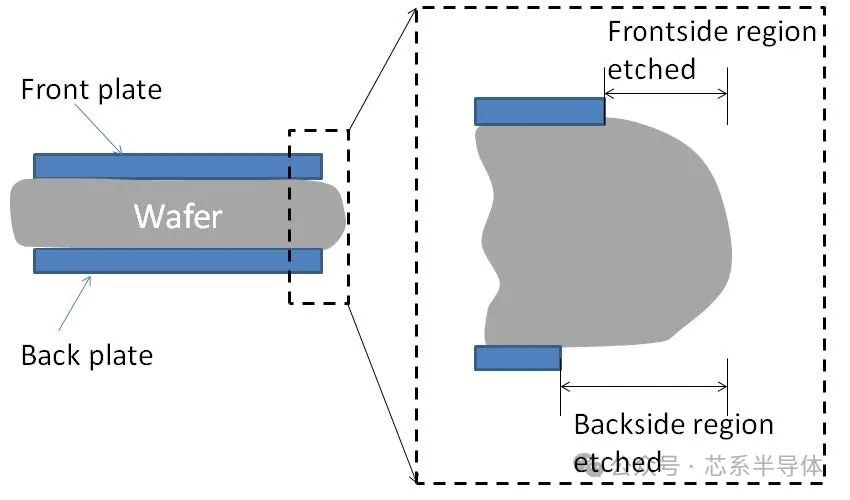

倒角刻蚀已投入生产约15年,旨在通过去除任何不需要的材料,如会损坏晶圆或从倒角移动到晶圆中心的颗粒缺陷来提高良率,需要在整个生产线上实施倒角刻蚀,因为工艺流程中有些环节会积聚这些材料。刻蚀设备经过优化,可去除晶圆边缘上的任何类型薄膜,无论是介电材料、金属还是有机物。在倒角的反应离子刻蚀(RIE)过程中,晶圆被上、下两块板固定,以确保只有晶圆的边缘、倒角部分和背面边缘暴露在外。

刻蚀过程根据客户和具体工艺流程的不同有不同的使用方式,一些客户等到积累了多层薄膜后,再清理至硅表面;而有时他们只是去除一层,比如用于深刻蚀NAND流程的厚碳硬掩模,这种碳掩模也是导电的,可能导致RIE腔室内的电弧,倒角刻蚀可以解决这些潜在的污染问题。

尽管湿法和干法清洁工艺各有其优势,但设备制造商通常会根据高产量生产选择其中一种。随着技术节点的缩小,这个问题变得更加重要,因为人们希望从晶圆边缘获得更多的良品。目前我们有一个2毫米的边缘排除要求,而客户更希望是1毫米,所以晶圆边缘的缺陷变得越来越重要。

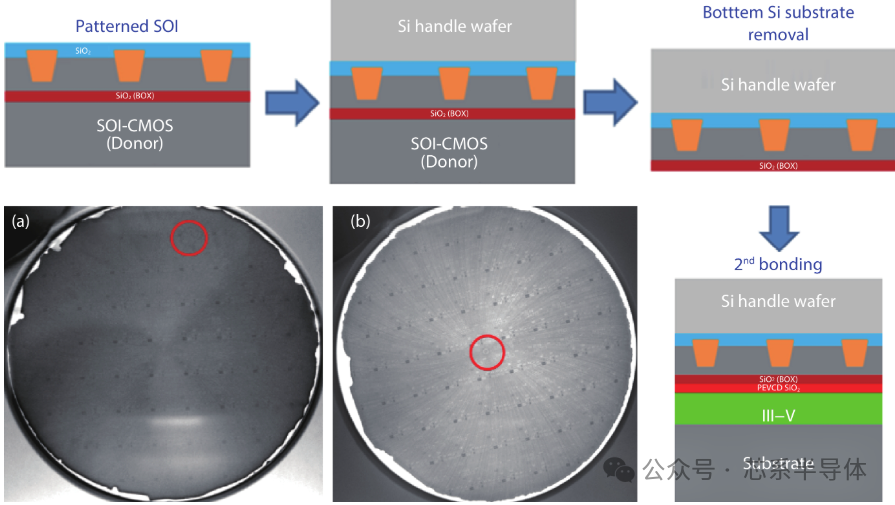

为了成功处理这些薄晶圆,在最终研磨/薄化步骤期间及之后,设备晶圆首先会与一片符合半导体行业标准的玻璃晶圆或硅载体晶圆进行键合。在键合步骤之前,这些晶圆将至少经过一步CMP处理步骤、随后的CMP后处理清洁步骤和键合过程本身。如果这些步骤不能达到关键质量要求,键合晶圆的边缘可能会出现空洞,甚至可能影响整个接合面。

例如,如果你有一层硅氮氧化物薄膜,可能会因为倒角处粘附力较弱而发生剥离。如果是像氮化钛(TiN)这样的材料,由于热应力也可能会发生剥离,因此可以用SC1清洁,而且对于去除背面聚合物也有类似的应用。经过等离子刻蚀后的薄膜,背面会有聚合物附着在边缘。CMP后也可能会有剥离现象。你需要去除这些,以防止剥离部分重新沉积在晶圆前面,造成缺陷并影响器件。

由于薄晶圆的处理和加工是一项挑战,大多数芯片制造商使用暂时键合技术,将晶圆键合到玻璃晶圆上,以便在加工过程中提供支持。对于这些非常薄的应用,尤其是当晶圆的厚度被薄化到仅为200?m时,客户使用Tyco环来固定晶圆,因为弯曲是最大的难题。

干法沉积

NAND设备是Lam公司首次开发倒角沉积的关键应用。倒角沉积系统沉积保护性的二氧化硅层,最早开始为3D NAND设备进行边缘沉积,现在它已经扩展到其他应用,其中最有趣的用途之一是支持3D封装的键合晶圆应用。沉积可以发生在正面、倒角或背面上的前几个毫米,从几百埃的厚度到几微米的材料。

另一个目前处于研发阶段的新应用是沉积薄的氮化硅薄膜,以控制铜污染。对于现有的应用,Lam公司的工程师预计每一步的良率提升将在0.2%到0.5%之间。

晶圆薄化与边缘修整

用于先进器件的基底硅晶圆薄化会引入显著的应力,当将其薄化时,基底硅变得越来越薄,因此会揭示出多个热应力和机械应力,表现为变形。例如,对于NAND和先进逻辑器件来说,剩下的硅几乎没有了,剩余的全是金属堆叠,而这些金属层会增加应力。

为了更好地理解去除的硅量,可以考虑原始晶圆的厚度。对于300毫米硅晶圆,原始厚度为775微米,经过所有器件加工后,薄化至35到50微米。尤其是当你开始考虑‘内存计算’的概念时,你将逻辑芯片直接堆叠在非常高性能、高带宽的内存之上,这样就涉及到完全不同的器件和完全不同的力和应力,这些应力存在于两者之间。

边缘修整过程是一种湿法工艺,可以去除晶圆外缘的1到1.5毫米,可以在预粘接或粘接步骤时进行。但假设你正在进行融合粘接,每个晶圆都有CMP滚落,然后基本上就是倒角。所以如果你将它们粘接在一起,始终会有一个区域没有完全填充。基本上会有一个非常非常小的间隙,慢慢地变为零。如果你现在开始研磨它,那个区域会变得非常脆弱,因为修整过程就像用刀修边。因此,如何控制这个边缘并管理它,目前是一个热门话题。

在芯片到晶圆的粘接中,芯片边缘的凸点非常容易受到应力的影响。如果设计人员无法改变应力分布,就必须调整设计规则,将I/O引脚移到芯片的中心。在晶圆到晶圆的粘接中,比如用于HBM时,晶圆边缘的凸点最容易受到应力影响。你会发现边缘有倒角,这很难控制,而且可能会有应力放大的边缘损伤。人们正在寻找不同的方法来解决这一问题。晶圆边缘修整在晶圆到晶圆的粘接、批量硅去除和CMP之前进行。许多传统的CMP供应商提供边缘修整工艺。

结论

晶圆边缘缺陷是制造中面临的重要挑战,正在通过CMP、干湿刻蚀、边缘沉积和晶圆边缘修整等方式加以解决。尽管一些领先的器件制造商已经在生产中使用了混合粘接技术,但它仍然是一个相对不成熟且成本较高的过程。通过专门为晶圆堆叠优化这些工艺,更多行业领域将能够使用这一赋能技术。

-

处理器

+关注

关注

68文章

19935浏览量

236183 -

堆叠

+关注

关注

0文章

37浏览量

16884 -

芯片晶圆

+关注

关注

0文章

6浏览量

8020 -

先进封装

+关注

关注

2文章

479浏览量

663

原文标题:芯片晶圆堆叠过程中的边缘缺陷修整

文章出处:【微信号:wc_ysj,微信公众号:旺材芯片】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

晶圆级多层堆叠技术及其封装过程

什么是3D芯片堆叠技术3D芯片堆叠技术的发展历程和详细资料简介

LED封装过程中的存在缺陷检测方法介绍

芯片晶圆里TaN薄膜是什么?TaN薄膜的性质、制备方法

五彩斑斓的芯片晶圆:不仅仅是科技的结晶

芯片晶圆堆叠过程中的边缘缺陷修整

芯片晶圆堆叠过程中的边缘缺陷修整

评论