文章来源:半导体与物理

原文作者:jjfly686

本文介绍了在芯片制造中的应变硅技术的原理、材料选择和核心方法。

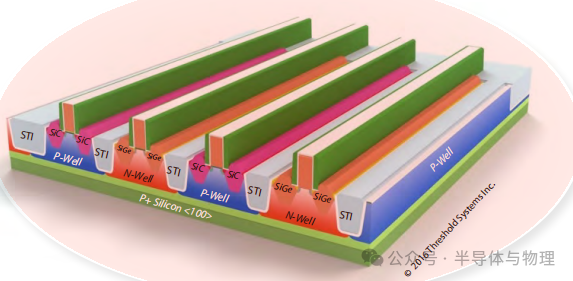

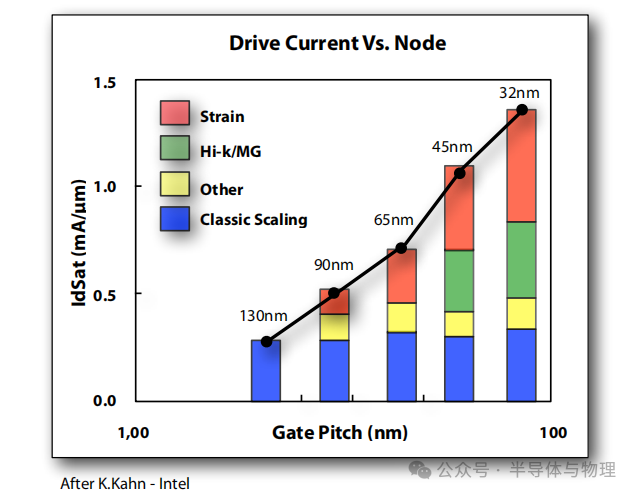

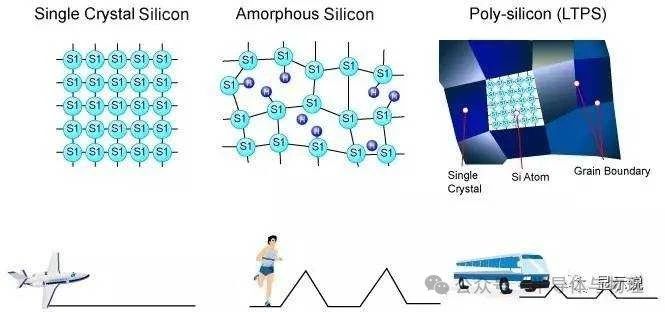

随着晶体管尺寸进入纳米级,传统硅基器件的性能面临物理极限,包括量子隧穿效应导致漏电流激增,栅介质变薄引发迁移率退化,以及短沟道效应加剧。应变硅技术通过对沟道施加机械应力改变硅晶格结构,从而优化载流子迁移率,成为延续摩尔定律的关键手段。

PMOS与NMOS的材料选择:SiGe与SiC

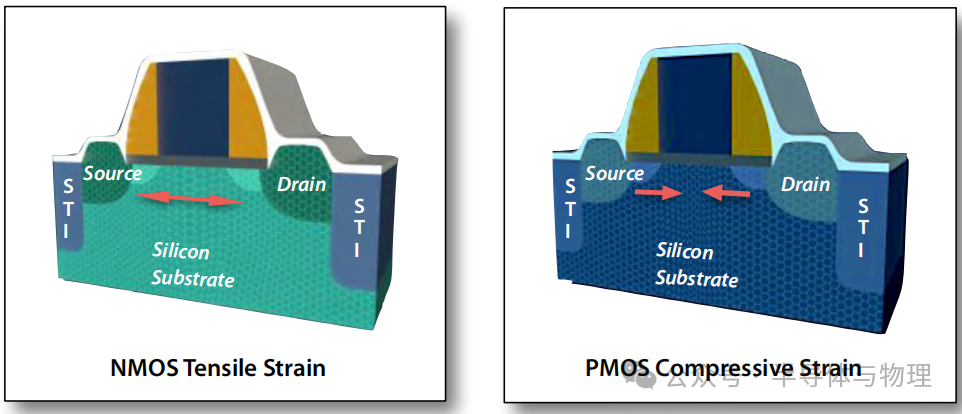

为了分别满足PMOS(空穴导电)和NMOS(电子导电)的需求,需采用不同材料引入特定应力:

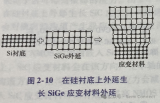

PMOS:SiGe(锗硅合金)引入压应力

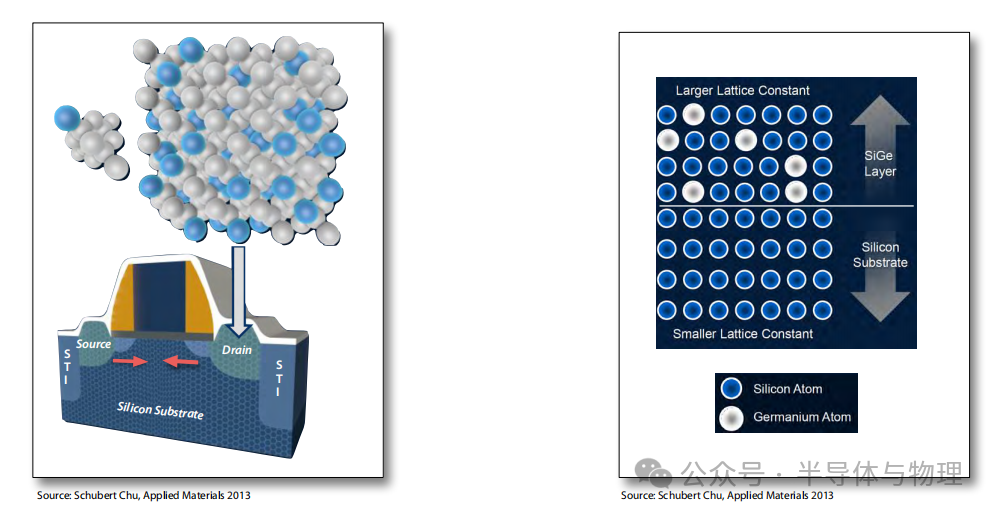

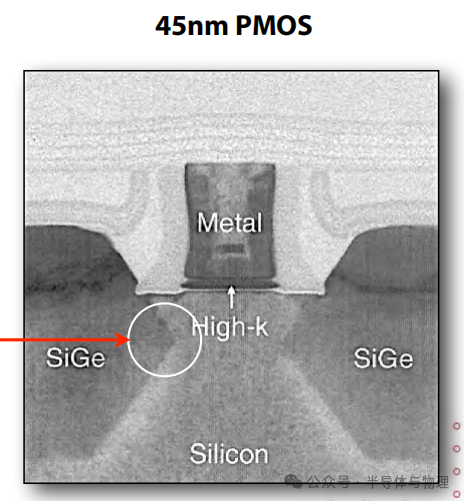

锗(Ge)的晶格常数比硅大4.2%。当PMOS的源漏区替换为SiGe时,其晶格膨胀会挤压沟道硅层,产生压应力,使空穴迁移率提升50%以上。在20 nm节点中,SiGe中锗含量达55%,通过优化外延层位置(如将SiGe晶体边缘靠近沟道)进一步增强应力。

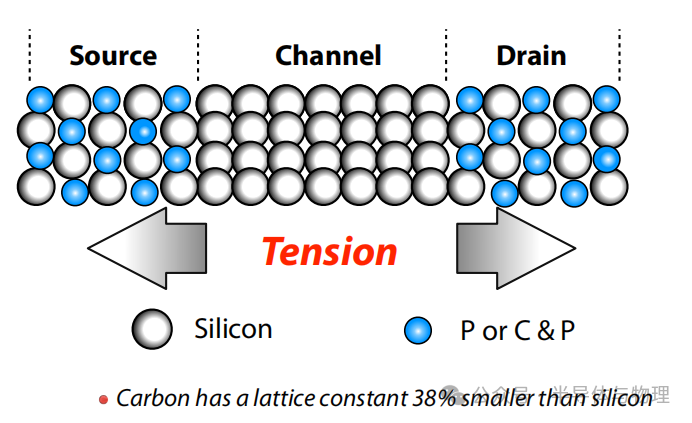

NMOS:SiC(碳化硅)或掺碳/磷硅引入张应力

碳(C)的晶格常数比硅小38%。在NMOS源漏区引入掺碳硅外延层(如Si:C或Si:C/P),可拉伸沟道晶格,产生张应力,使电子迁移率提升20%。需平衡材料稳定性与应力强度。例如,碳掺杂需精确控制浓度以避免晶格缺陷。

应变引入的核心方法

选择性外延替换源漏区

刻蚀原有源漏区→外延生长SiGe(PMOS)或Si:C(NMOS)→退火激活掺杂原子。

应力记忆技术(Stress Memorization Technique, SMT)

通过掩膜边缘位错诱导张应力。例如,在45/32 nm节点中,采用预非晶化离子注入(PAI)+氮化硅应力覆盖层,退火后形成位错,提升NMOS短沟道迁移率10%。

-

NMOS

+关注

关注

3文章

370浏览量

35801 -

晶体管

+关注

关注

77文章

10039浏览量

142430 -

芯片制造

+关注

关注

11文章

697浏览量

29844

原文标题:芯片制造中的应变硅技术

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

【「大话芯片制造」阅读体验】+ 芯片制造过程和生产工艺

最全最详尽的半导体制造技术资料,涵盖晶圆工艺到后端封测

可控硅及组件-厂家介绍

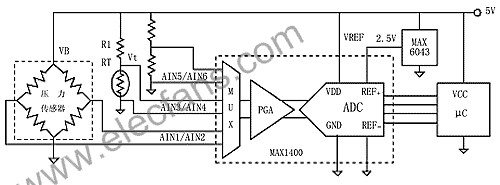

如何实现具有较大信号输出的硅应变计与ADC的接口

如何实现较大信号输出的硅应变计与模数转换器(ADC)的接口

多晶硅在芯片制造中的作用

芯片制造中的应变硅技术介绍

芯片制造中的应变硅技术介绍

评论