概述

AD9525旨在满足长期演进(LTE)和多载波GSM基站设计的转换器时钟要求。

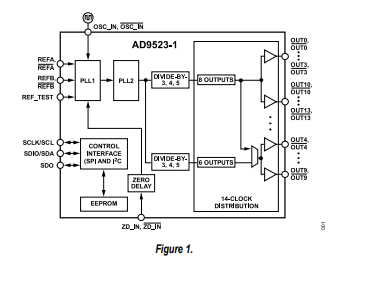

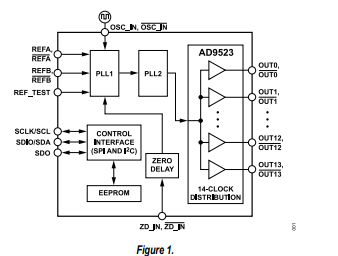

AD9525提供低功耗、多路输出时钟分配功能,具有低抖动性能,并且片内集成锁相环(PLL),可以配合外部VCO或VCXO使用。VCO输入和八个LVPECL输出最高工作频率为3.6 GHz。所有输出共用一个分频器,分频范围为1到6。

AD9525提供了一个专用输出,可用于提供一个用于重置或同步数据转换器的可编程信号。输出信号可以通过一个SPI写入操作激活。

AD9525提供48引脚LFCSP封装,可以采用3.3 V单电源供电。外部VCXO或VCO的工作电压最高可达5.5 V。

AD9525的工作温度范围为?40°C至+85°C的扩展工业温度范围。

数据表:*附件:AD9525旨在满足长期演进(LTE)和多载波GSM基站设计的转换器时钟技术手册.pdf

特性

- 集成超低噪声频率合成器

- 8个差分3.6 GHz LVPECL输出和1个LVPECL或2个CMOS SYNC输出

- 2个差分参考输入和1个单端参考输入

应用

LTE和多载波GSM基站

为高速ADC、DAC提供时钟

自动测试设备(ATE)和高性能仪器仪表

40/100Gb/s OTN线路端时钟

电缆/DOCSIS CMTS时钟

测试与测量

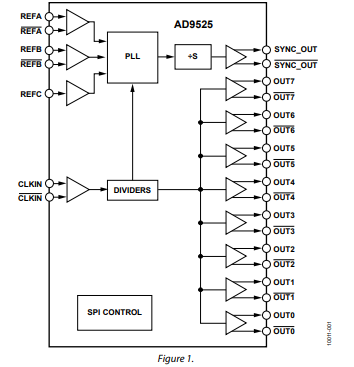

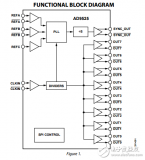

框图

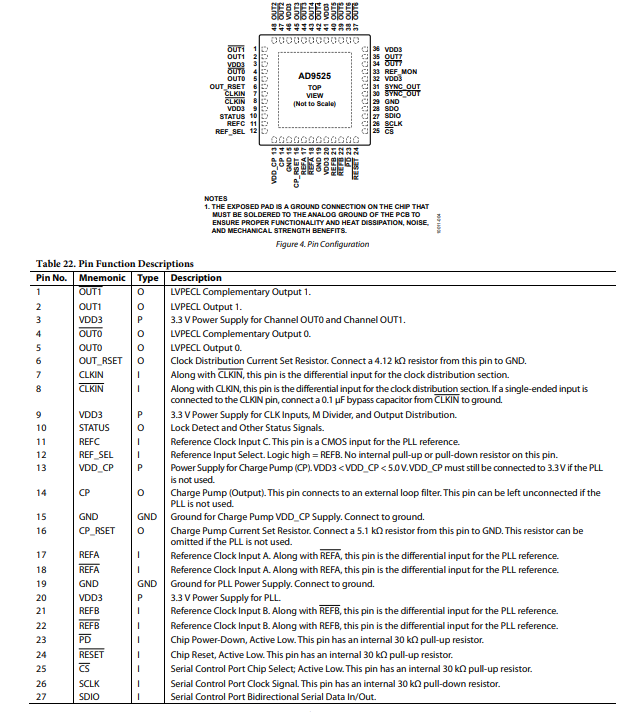

引脚配置描述

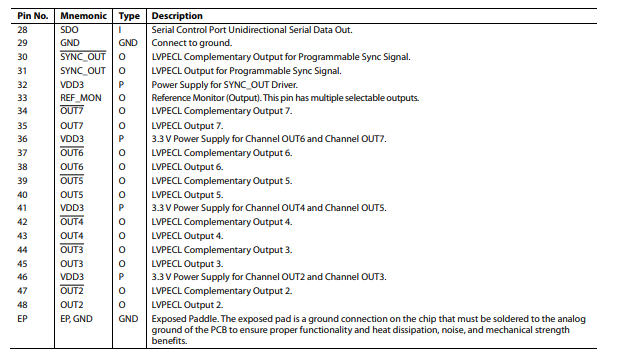

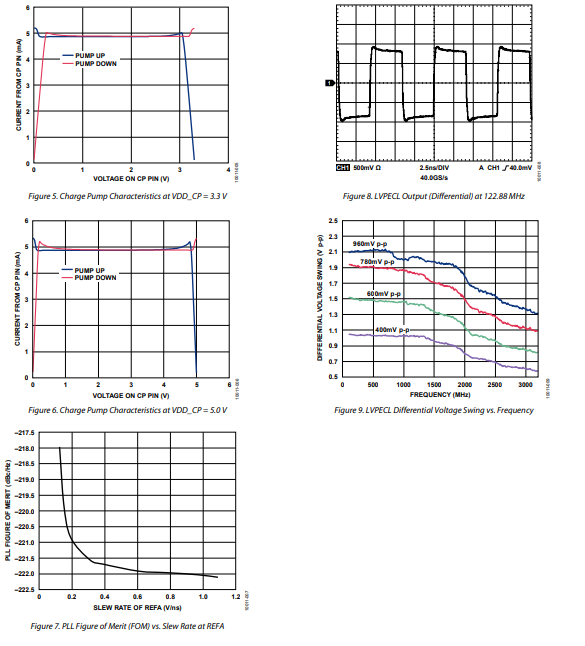

典型性能特征

术语解释

相位抖动和相位噪声

理想正弦波可被视为在每个周期内,相位随时间从0°到360°持续且均匀地变化。实际信号会在一段时间内显示出与理想相位变化的偏差量,这种现象被称为相位抖动。尽管有许多因素会导致相位抖动,但一个主要因素是随机噪声,其统计特性呈高斯(正态)分布。

这种相位抖动会导致正弦波在频域中的能量扩散,产生连续的功率谱。该功率谱通常以给定频率偏移处每单位Hz的dBc值来表示,它是相对于载波频率功率,在1Hz带宽内所包含功率的比值(以分贝表示) 。对于每次测量,偏移频率处的功率值也会给出。

对某一频率偏移区间(例如10kHz到10MHz)内的总功率进行积分也具有实际意义。这被称为该频率偏移区间上的积分相位噪声;它能直观地反映出该频率偏移区间内相位噪声所导致的时间抖动情况。

相位噪声对模数转换器(ADC)、数模转换器(DAC)和射频混频器的性能有不利影响。它会降低这些转换器和混频器可实现的动态范围,尽管影响方式略有不同。

时间抖动

相位噪声是频域现象,而在时域中,其表现为时间抖动。观察正弦波时,两个连续过零点之间的时间会发生变化。观察方波时,(时间)抖动表现为信号边沿与理想(规则)触发时刻的偏差。在这两种情况下,与理想时间的偏差量就是时间抖动。由于这些变化是随机的,所以时间抖动的规格以均方根(rms)或1σ(高斯分布中的1个标准差)表示。

在数模转换器(DAC)或模数转换器(ADC)的采样时钟上出现的时间抖动,会降低信号噪声比(SNR)和动态范围。最低的可能抖动能使给定转换器发挥出最高性能。

附加相位噪声

附加相位噪声是指可归因于被测外部振荡器或时钟源的相位噪声量。通过减去任何外部振荡器或时钟源的相位噪声,就可以预测该器件在与各种振荡器和时钟源配合使用时,对系统总相位噪声的影响程度,因为每个振荡器和时钟源都会对总相位噪声产生各自的贡献。在许多情况下,一个元件的相位噪声会主导系统的相位噪声。当存在多个相位噪声源时,总相位噪声是各个贡献源的均方根总和。

附加时间抖动

附加时间抖动是指可归因于被测外部器件或子系统的时间抖动量。通过减去任何外部振荡器或时钟源的时间抖动,就能够预测该器件在与各种振荡器和时钟源配合使用时,对系统总时间抖动的影响程度,因为每个振荡器和时钟源都会对总时间抖动产生各自的贡献。在许多情况下,一个外部振荡器或时钟源的时间抖动会主导系统的时间抖动。

-

转换器

+关注

关注

27文章

9152浏览量

152700 -

LTE

+关注

关注

15文章

1368浏览量

179424 -

时钟

+关注

关注

11文章

1909浏览量

133493 -

GSM

+关注

关注

9文章

837浏览量

124864 -

AD9525

+关注

关注

0文章

5浏览量

9285

发布评论请先 登录

ADI推出业界最低抖动RF时钟IC AD9525

用于评估AD9525 3.6 GHz时钟发生器的评估板AD9525/PCBZ

用于评估AD9525 2950 MHz VCO时钟发生器的评估板AD9525/PCBZ-VCO

Xilinx推出Smarter无线电解决方案 可满足新一代LTE与多载波GSM平台性能需求

低电压输出低抖动时钟发生器ad9525数据表

AD9525 AD9525旨在满足长期演进(LTE)和多载波GSM基站设计的转换器时钟要求。

AD9525旨在满足长期演进(LTE)和多载波GSM基站设计的转换器时钟技术手册

AD9525旨在满足长期演进(LTE)和多载波GSM基站设计的转换器时钟技术手册

评论