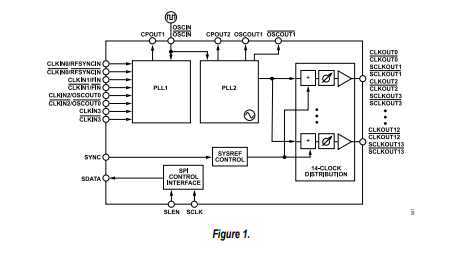

SC6302是一款兼容HMC7044的高性能双环路整数、小数分频抖动衰减器,能够执行频率转换、选择参考信号并生成超低相位噪声的时钟提供给并行或串行(JESD204B)接口的高速数据转换器。SC6302提供14路低噪声且可配置的输出,可以灵活地匹配RF收发器系统中的许多不同器件接口,比如数据转换器、本振、发送/接收模块、FPGA和数字前端(DFE)ASIC。

SC6302可产生最多7对DCLK和SYSREF,符合JESD204B接口要求。该器件具有出色的串扰、频率隔离以及杂散性能,支持单端和差分输出频率。DCLK和SYSREF时钟输出可配置为不同的输出信号标准,如CML、LVDS、LVPECL和LVCMOS。

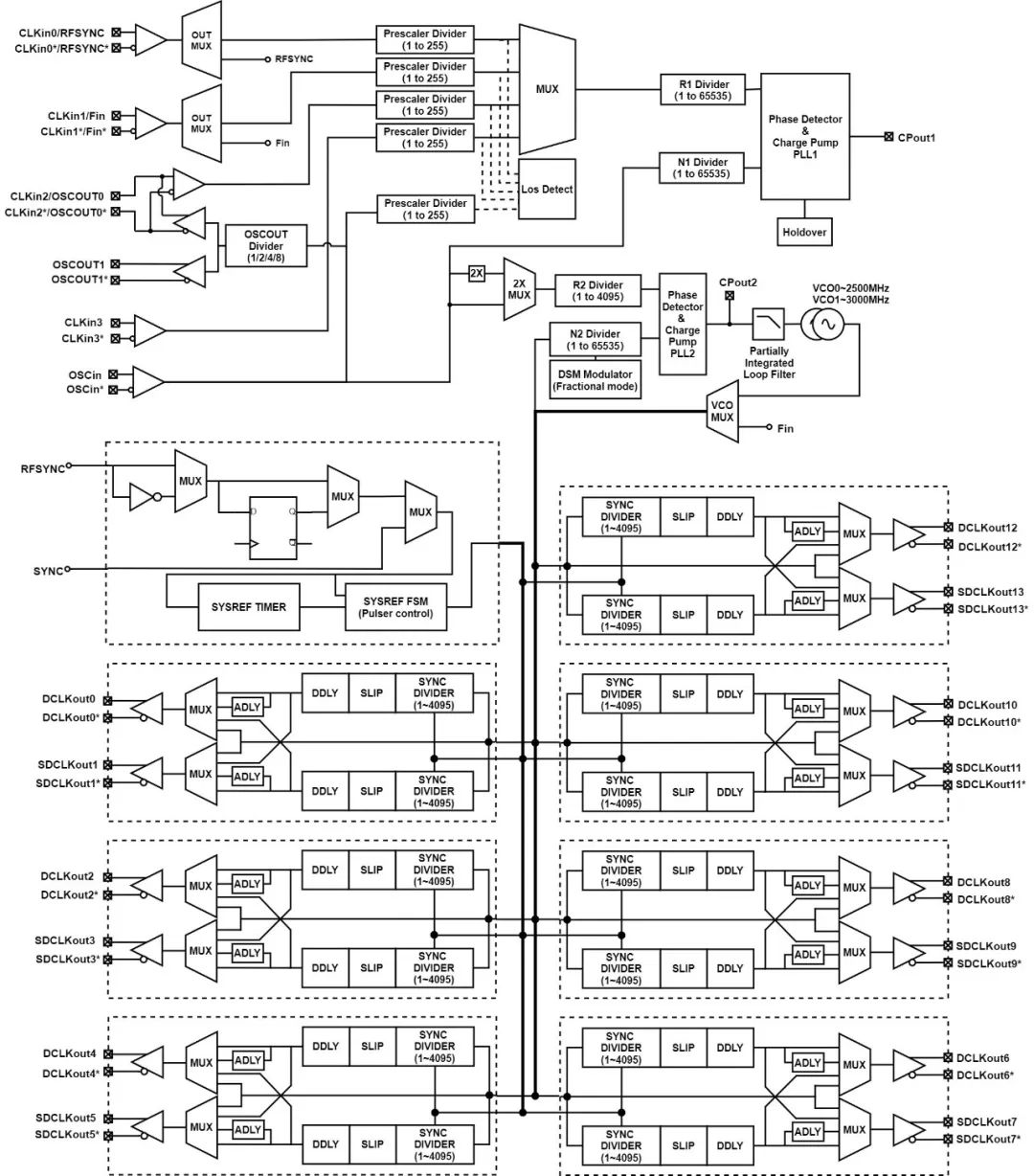

SC6302功能模块示意图

主要性能:

?支持JEDEC JESD204B

?超低RMS抖动

48fs RMS Jitter(12kHz到20MHz)@2457.6M

底噪:-153dBc/Hz@2457.6MHz

?PLL2可提供多达14路差分时钟

最多7个SYSREF时钟

时钟最大输出频率3.2GHz

支持LVPECL,LVDS,CML等输出接口

?支持最多2个缓冲压控振荡器(VCXO)输出

?信号丢失(LOS)检测和无中断参考切换

?4 个GPIO报警/状态指示器

?支持最高3200MHz的外部VCO输入

?工作温度:-40℃到85℃

?工作电压:3.15V到3.45V

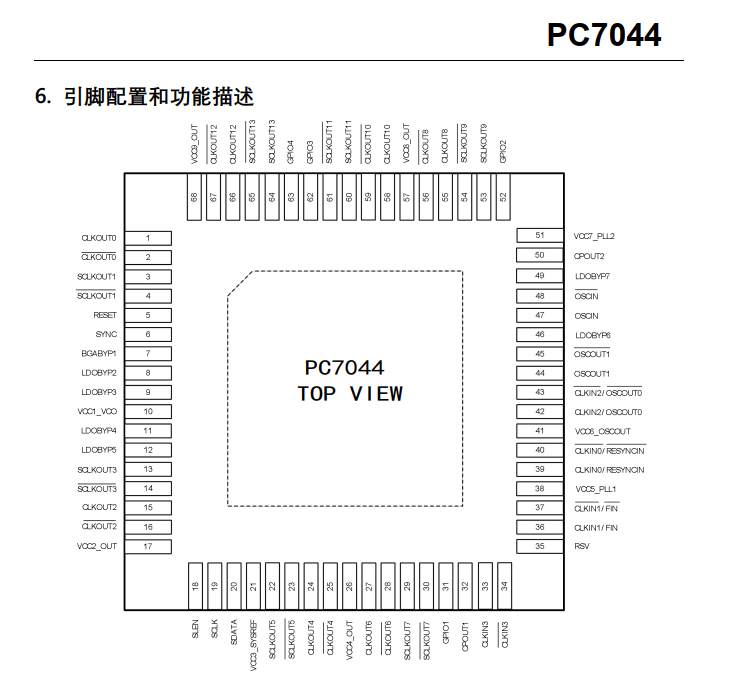

?QFN-68封装

应用场景:JESD204B时钟产生、无线基础设施(多载波GSM、LTE、W-CDMA)、数据转换器时钟、微波基带卡、相控阵参考分配

注:如涉及作品版权问题,请联系删除。

-

衰减器

+关注

关注

4文章

726浏览量

35287 -

消除器

+关注

关注

0文章

55浏览量

8883

发布评论请先 登录

HMC7044外参考时钟切换失败的原因?

替代HMC7044超低噪高性能时钟抖动消除器支持JESD204B

请问HMC7044锁相环可以配出8路2.5G,相位可调的时钟吗?

hmc7044使用外部VCO时钟输入时,如何使得时钟能够相位对齐 ?

AD9172参考板上7044给出的时钟电平是什么呢?

HMC7044: 带 JESD204B 接口的高性能、3.2 GHz、14 路输出抖动衰减器

HMC7044B支持JESD204B和JESD204C的高性能、3.2GHz、14输出抖动衰减器技术手册

14路差分输出时钟抖动消除器SC6302,兼容HMC7044

14路差分输出时钟抖动消除器SC6302,兼容HMC7044

评论