这里以钛金的LVDS为例。

LVDS RX 时钟选择

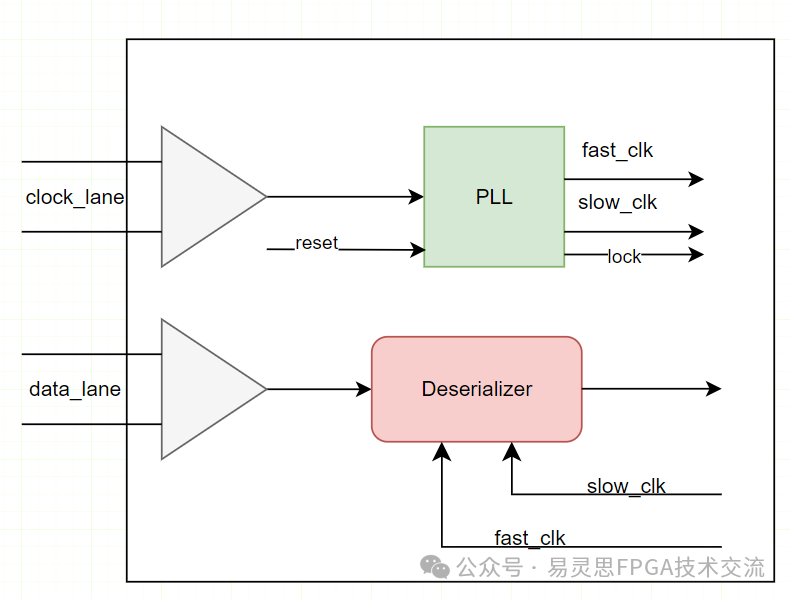

LVDS时钟的接收要连接名字为GPIOx_P_y_PLLINz名字的差分对,这样的管脚直接驱动PLL,产生LVDS接收需要的fast_clk和slow_clk,这种主要是用于数据和时钟的速率不是1:1,比如大家常见的1:7,1:8和1:10等,这时就要使用串化/解串器;如果时钟和数据的速率比是1:1并且速率不高,也可以考虑用GCLK走时钟来采集数据。

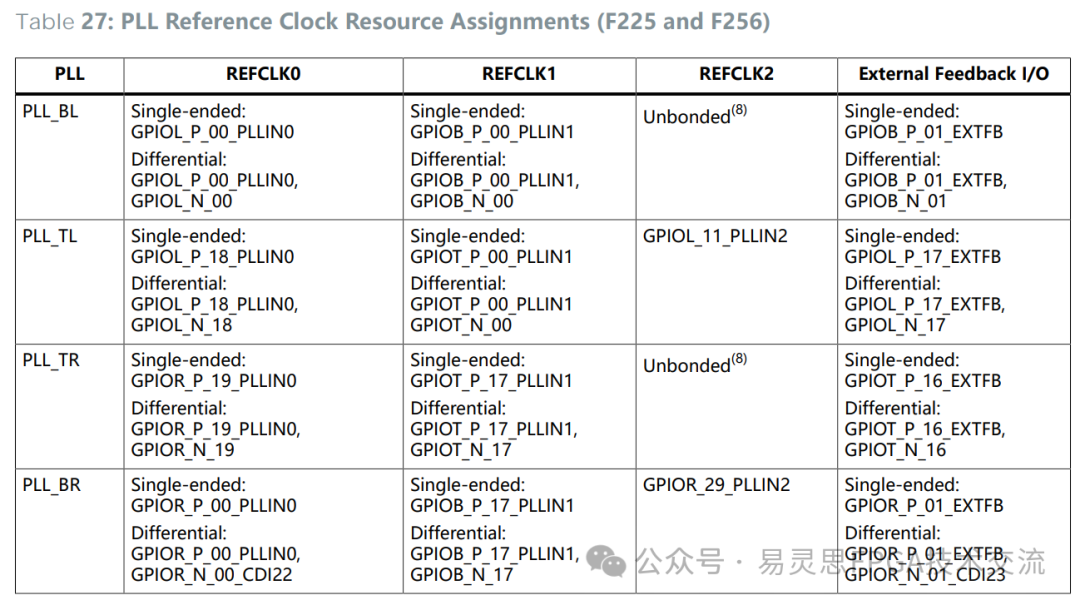

以Ti60F225为例,它共有4个PLL,分别为PLL_BL,PLL_BR,PLL_TR和PLL_TL4个PLL,在要求解串器的情况下,最大只能接收4组LVDS,这是在不考虑PLL作为别的用途的前提下的。

LVDS的PLL的复位信号的处理

有些时候LVDS并不是连续的,这就要对PLL进行复位处理。在处理方式上我们可以检测PLL_LOCKED信号是否锁定,如果隔一段时间没有锁定就对PLL进行一次复位。然后再循环检测锁定信号和复位的过程,直到PLL_LOCKED信号为高。目前遇到一些LVDS接收异常的问题很多是通过这样的方式来解决的。这是为了排除PLL假锁的情况。

interface设置

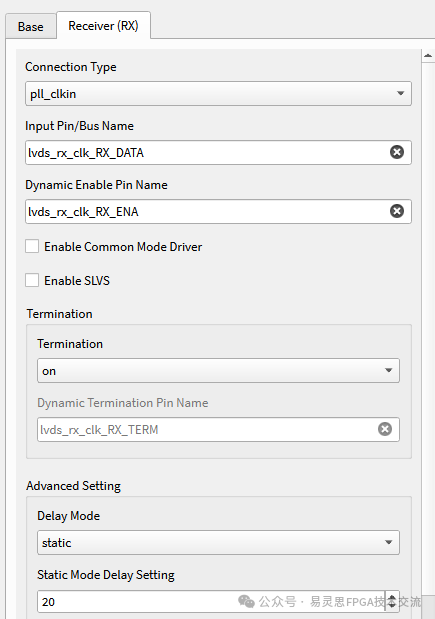

(1)rx clock设置

Enable Common Mode Driver:当使用交流耦合时。要勾选Enable Common Mode Driver。

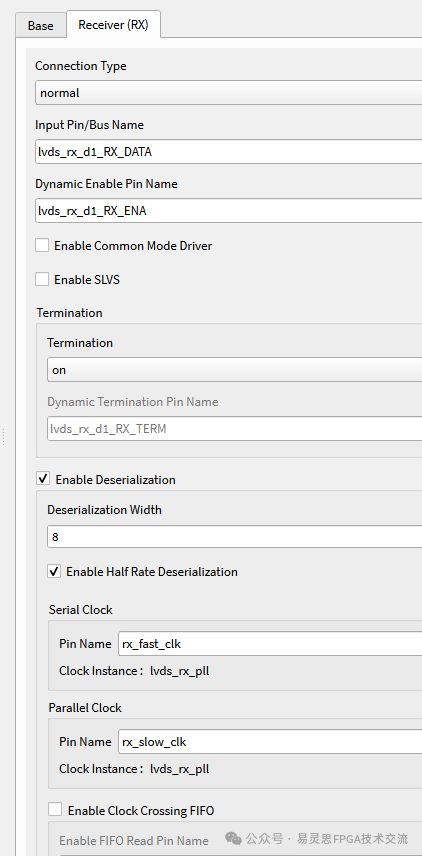

(2) data 设置

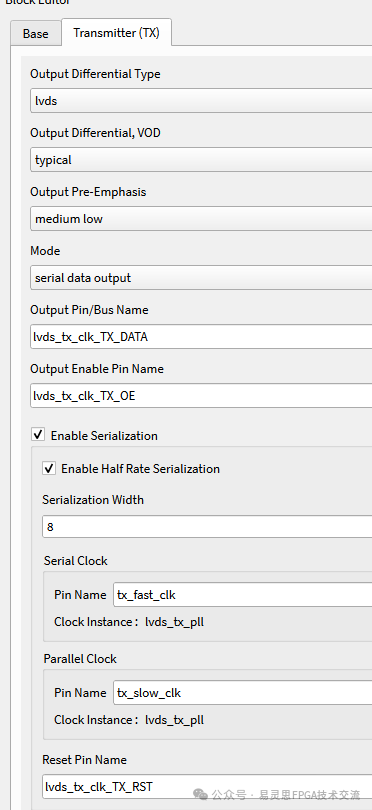

Enable Deserialization使能解串因子,Enable Half Rate Deseralization:是指双沿采样 。在带有解串器的设置中要指定解串时钟和并行的时钟。对于发送设置也是大致相同的,只不过要指定的是串化因子。

(3)发送时钟的设置

发送时钟不同于接收时钟,发送与数据的设置比较相近。把发送时钟按如下设置。

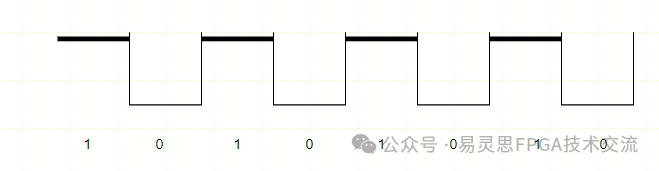

assign lvds_tx_clk_TX_DATA = 8'hAA;

经过串化之后,时钟波形就变成了如下的样子。如果发送的数据是8'hF0时钟又会是什么样子呢?大家可以自己思考下。

当然LVDS输出时钟选择serial data output 如果设置为clk输出,时钟速率最大为数据速率的1/8.具体使用可以先试试。

当然LVDS输出时钟选择serial data output 如果设置为clk输出,时钟速率最大为数据速率的1/8.具体使用可以先试试。

信号控制

对于数据一般不会出错,大家可能会忘记的是设置使能和复位。注意使能和复位都是高有效。所以正常运行时要把使能设置为高,复位设置为低。

assign lvds_rx_clk_RX_ENA = 1'b1;assign lvds_rx_d0_RX_ENA = 1'b1;assign lvds_rx_d1_RX_ENA = 1'b1; assign lvds_rx_d2_RX_ENA = 1'b1;assign lvds_rx_d3_RX_ENA = 1'b1;assign lvds_rx_d0_RX_RST = 1'b0;assign lvds_rx_d1_RX_RST = 1'b0; assign lvds_rx_d2_RX_RST = 1'b0;assign lvds_rx_d3_RX_RST = 1'b0; assign lvds_tx_d0_TX_RST = 1'b0;assign lvds_tx_d1_TX_RST = 1'b0; assign lvds_tx_d2_TX_RST = 1'b0;assign lvds_tx_d3_TX_RST = 1'b0;assign lvds_tx_d0_TX_OE = 1'b1;assign lvds_tx_d1_TX_OE = 1'b1;assign lvds_tx_d2_TX_OE = 1'b1;assign lvds_tx_d3_TX_OE = 1'b1;

PLL的设置

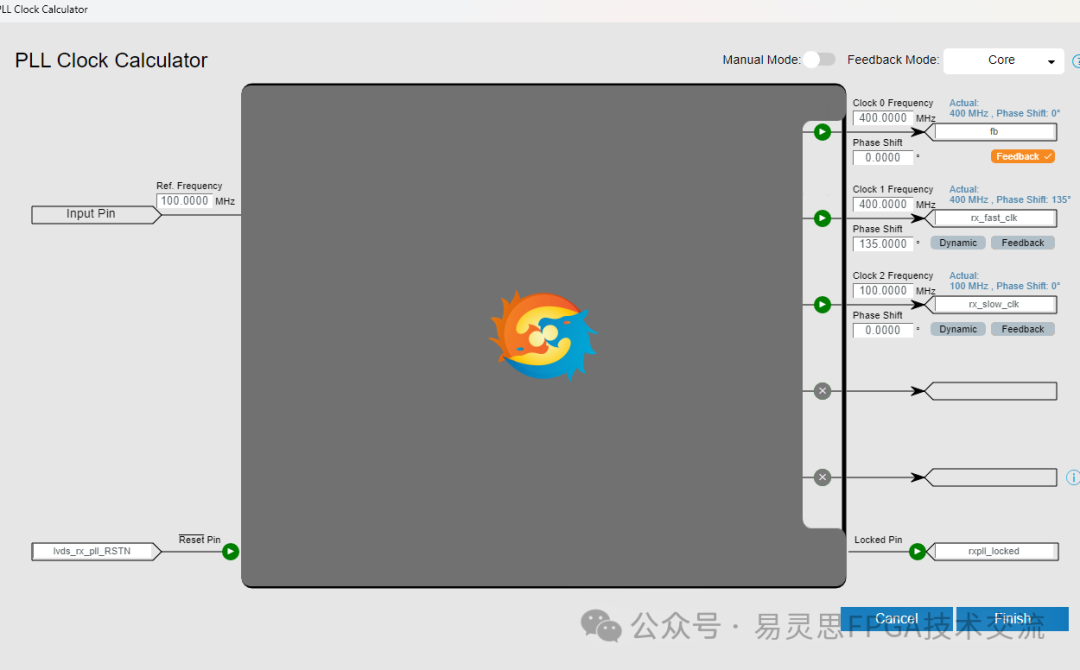

接收的fast_clk是否要移相,由源端时钟与数据的相位关系来决定,如果源是边沿对应,fast_clk可以移相90或者135;如果是中心对齐,则可以设置相位为0或者为45。

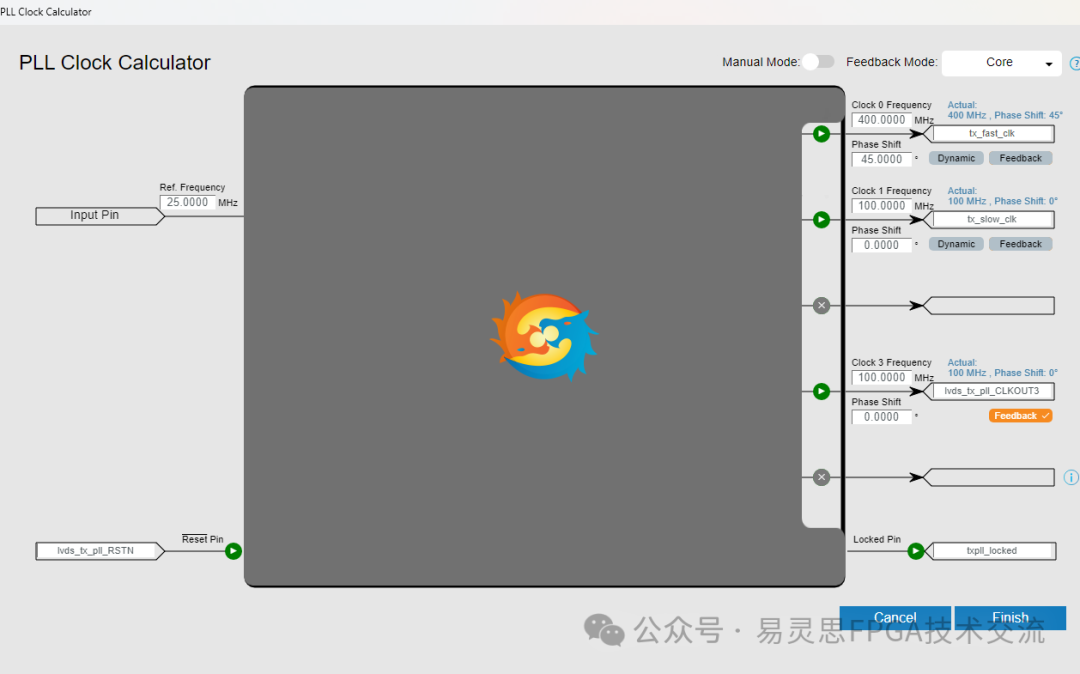

发送数据如果与时钟有相位差,比如中心,那边需要产生三个时钟,fast_tx_clk_c,fast_tx_clk_d及slow_tx_clk.fast_tx_clk_c用于时钟的fast_clk,为90度,而fast_tx_clk_d为0度,用于数据的fast_clk.

当然大家也可以根据产生的波形或者数据的延时进行适当的调整。

串化/解串数据的排列

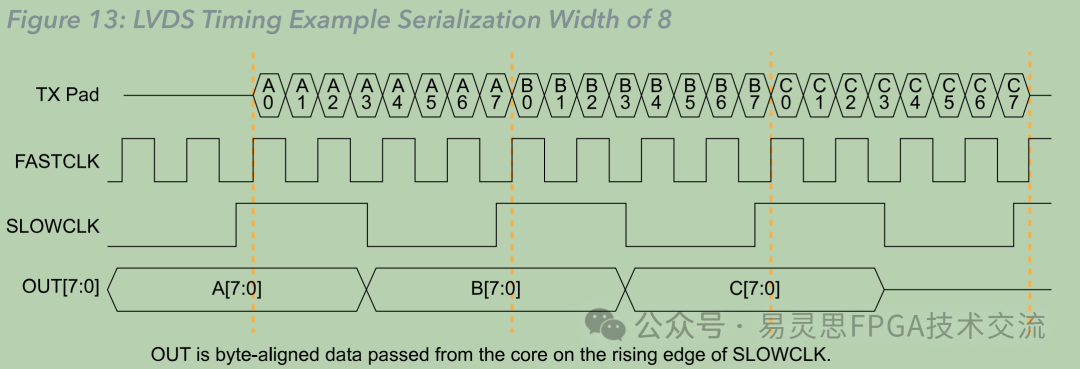

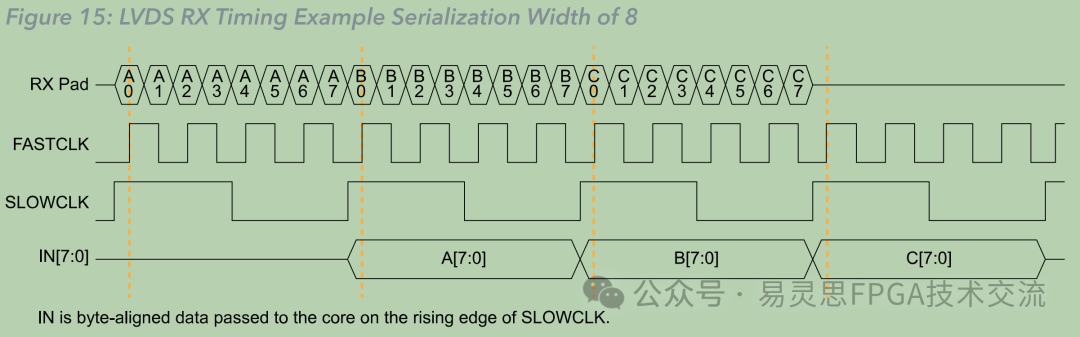

如下图所示,发送时LSB先发送,当然接收也是LVDS先接收。

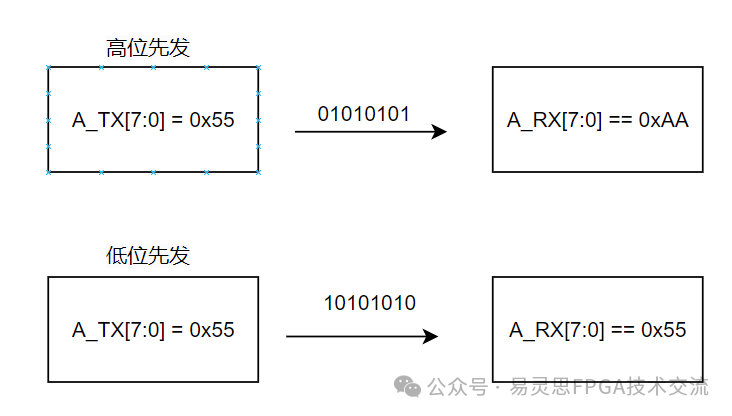

所以要注意发送端与接收端的大小端问题。以下图为例,如果发送端是高位先发送,那接收端的数据刚好是反的。处理上应该是先把数据位对调,比如

A_RX_ALIGN = {A_RX[0],A_RX[1],A_RX[2],A_RX[3],A_RX[4],A_RX[5],A_RX[6],A_RX[7]}

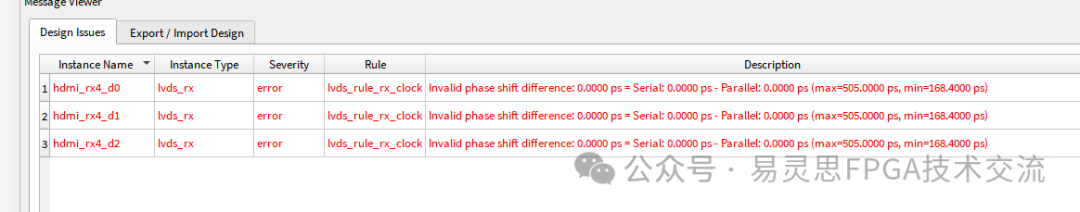

在帮助客户调试HDMI的时候发现,LVDS不能够进行动态调节相位。解决方案是:

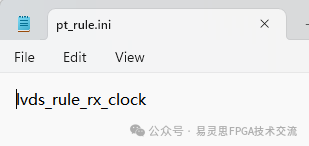

(1)在工程目录下建议pt_rule.ini文件;

(2)在文件中输入想要开放权限的rule,以下图为例,报错的Rule是lvds_rule_rx_clock。效果如下。

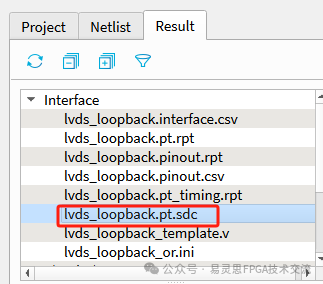

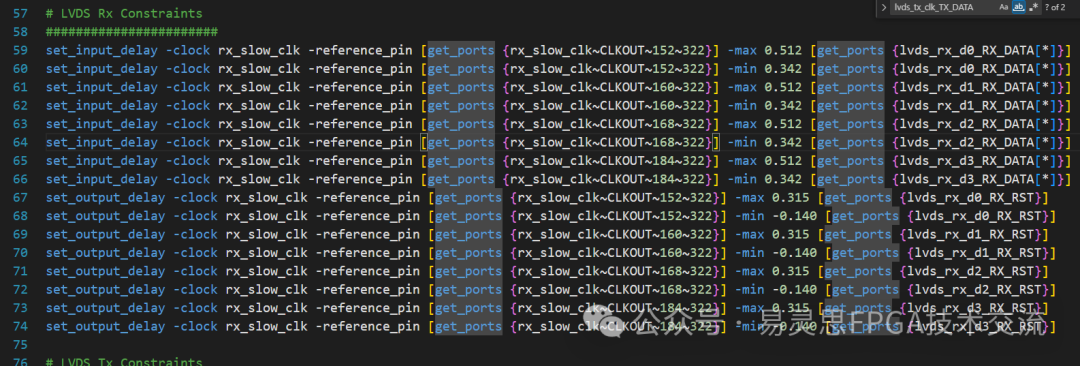

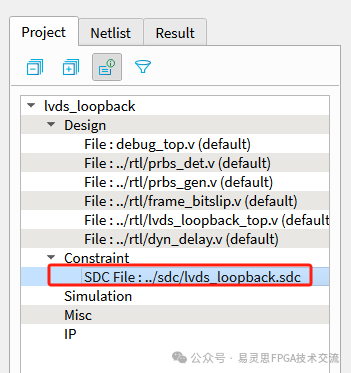

约束添加

需要再次强调的是,Result --> interface --> xx.pt.sdc文件中会有相关的约束模板;我们可以复制该文件到工程目录下,根据实际需要进行调整

里面关于LVDS的约束部分如下,大家可以自己打开仔细查看

并添加到Project -->Constraint下。

Trion的LVDS也有相似的操作,这里先只给出一些注意事项,如果需要补充会再次更新。

1. 如果需要在LVDS IO里差分信号同单端信号混用,须最少隔开2对差分IO;例如:使用RXP09/RXN09就不能使用RX07/08/10/11作为差分信号

2. 关于LVDS设备间的互连,要求LVDS RX端的 Vid,Vicm 与LVDS TX端的Vod,Vocm电平标准匹配即可互连

3、LVDS RX源同步时钟管脚只能通过GPIOx_RXP/Ny_CLKP/Nz经对应PLL输入。

4、每一个LVDS Bank中的IO用作单端输出,不能超过14个,引起同步开关噪声(SSN)风险,输入没有限制

T20的GPIOB_CLKN0/GPIOB_CLKP0,用做LVDS时只能作为LVDS RX时钟直接进入锁相环,不能进入内部逻辑

Trion LVDS常用经验

(1)post-divider要修改成2,反馈时钟用slow_clock.

(2)客户测试LVDS发送时钟lvds输出改3pf,数据改10pf,暂时没问题。后续生产小批量看下一致性

(3)添加LVDS约束

现象:(1)pll锁不定,时钟路径由FPGA给出到sensor,再由sensor的LVDS给到FPGA进入pll;

(2)把VCC电压从1.2V抬到1.25V可以解决一部分问题;

(3)常温下FPGA PLL不能锁定,但是如果用风枪加热一下到40度左右PLL就能锁定;

(4)客户第一次做了10多块板不存在该问题,第二次做了100块,有10块左右出现了上面的PLL锁不定问题。

(5)该现象会跟随芯片走。

解决思路:

(1)目前已经确认客户都没有控制LVDS接收PLL的复位,目前要求客户在PLL参考时钟稳定之后再重新复位一下再重新锁定。

审核编辑 黄宇

-

时钟

+关注

关注

11文章

1903浏览量

133380 -

lvds

+关注

关注

2文章

1129浏览量

67671

发布评论请先 登录

怎么使用LVDS IO引脚作为1位ADC?

FPGA跟一个ADC通过LVDS进行通信,LVDS信号的共模电压在1.2V左右

SN65LVDS179-Q1,SN65LVDS180-Q1,

65LVDS95-Q1,pdf(LVDS SERDES Tr

ADN4667 3 V LVDS Quad CMOS Dif

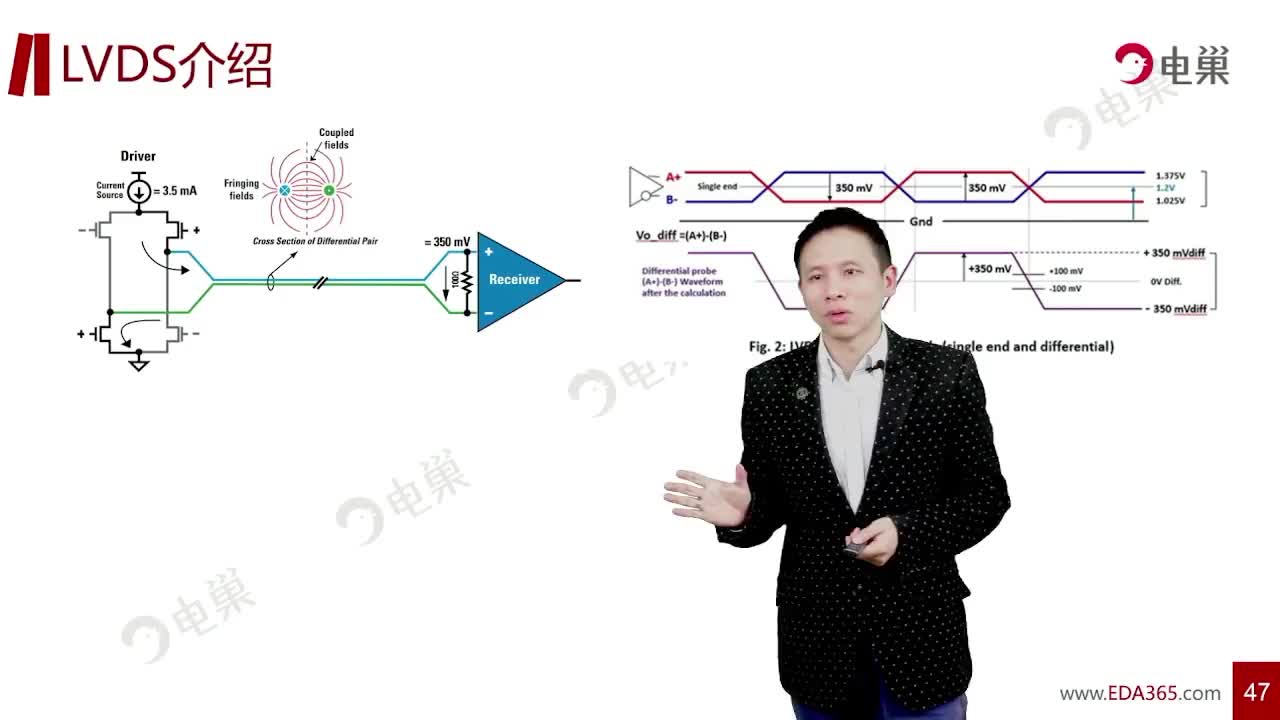

LVDS信号电平特性

SN65LVDS93A-Q1 SN65LVDS93A-Q1 Flatlink 发送器

SN65LVDS95-Q1 汽车类 LVDS SERDES 收发器

SN65LVDS84AQ-Q1 SN75LVDS84A-Q1, SN65LVDS84AQ-Q1

SN65LVDS1 单路 LVDS 发送器

如何解决FPGA引脚与LVDS信号相连时兼容性的问题

浅谈LVDS-V1

浅谈LVDS-V1

评论