锁频环为什么锁定后又发生失锁现象?

锁频环是一种非常重要的电子电路,常见于通信设备、数字信号处理、时钟恢复和频率合成等领域。锁频环的作用是将输入信号与输出信号的频率进行锁定,使得输出信号与输入信号的频率和相位保持恒定关系。然而,尽管锁频环被设计用于保持频率的稳定性,但有时会发生失锁现象。

首先,我们需要了解锁频环的基本工作原理。锁频环通常由相位比较器、低通滤波器、锁定放大器和电压控制振荡器等组成。相位比较器用于比较输入信号和反馈信号的相位差,产生误差信号。低通滤波器用于滤除误差信号中的高频成分,得到稳定的控制电压。锁定放大器将控制电压放大,并驱动电压控制振荡器,使其输出信号的频率与输入信号相等或者是输入信号的某个倍数。

当锁频环处于稳定锁定状态时,输入信号与输出信号的频率和相位保持固定的关系。然而,多种因素可能会导致锁频环失锁,下面将逐一进行详细讨论。

第一个可能的原因是输入信号的幅值过大或者过小。在理想情况下,输入信号的幅值应该是锁频环能够正常工作的范围内合适的幅值。如果输入信号的幅值过大,可能导致相位比较器的输出饱和,使得锁频环无法正常工作。相反,如果输入信号的幅值过小,可能导致相位比较器的输出信号太微弱,无法有效地驱动锁频环的其他部分。因此,适当调整输入信号的幅值是避免失锁现象的关键。

第二个可能的原因是锁定范围的问题。锁频环的设计应考虑到输入信号的变化范围,并使得锁定范围足够宽广,以适应输入信号在一定范围内的变化。如果锁定范围过小,当输入信号超出该范围时,锁频环就会失锁。因此,为了避免失锁现象,必须对锁定范围进行正确的设计和调整。

第三个可能的原因是噪声的干扰。噪声是所有电子电路中不可避免的存在,而锁频环也不例外。噪声干扰会破坏锁频环中各个部分之间的稳定相位关系,从而导致失锁现象的发生。为了减小噪声对锁频环性能的影响,可以采取一系列措施,例如使用低噪声元件、增加滤波器的带宽等。

第四个可能的原因是环路滞后。在锁频环中,反馈路径的延迟会导致环路滞后,从而破坏锁频环的稳定性。为了解决这个问题,可以采取补偿措施,如增加相位裕度、增加环路带宽等。

此外,还有其他可能导致锁频环失锁的因素,例如温度变化、元件老化、设计不当等。这些因素都有可能影响锁频环的稳定性,导致失锁现象的发生。因此,在设计和使用锁频环时,需要细致地考虑和分析各种潜在因素,并对锁频环进行适当的调整和优化。

综上所述,锁频环失锁是一个复杂的问题,可能由多种因素或其组合导致。在本文中,我们详尽、详实地解释了为什么锁频环会失锁,并讨论了可能的原因。了解这些原因对于设计和优化锁频环是非常重要的,可以帮助我们避免失锁现象的发生,提高锁频环的性能和可靠性。

-

噪声干扰

+关注

关注

0文章

39浏览量

14678 -

锁频环

+关注

关注

0文章

6浏览量

3826

发布评论请先 登录

ADF5355失锁: 在用ADF5355进行多次扫频时,延时给了500ms还是经常会失锁

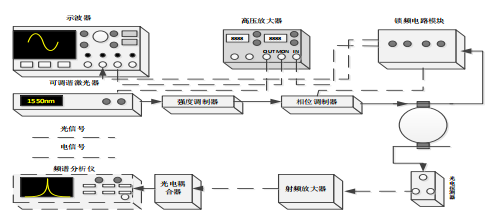

高压放大器在基于高Q微环谐振腔OEO的系统测试中的应用

为何DAC5686高频率输入PLL不能锁定?

CDCE72010运行一段时间后PLL_LOCK失锁怎么解决?

使用LMX2820实现射频信号输出时出现失锁现象,怎么解决?

LMX2820输出信号失锁现象是什么原因导致的?如何解决?

LMX2820EVM锁定后出现一定范围的频率漂移,为什么会这样?

LMK04821 PLL1偶尔会失锁,失锁后大约0.16ms再锁定;PLL2始终锁定,为什么?

LMX2594每次外部触发扫频后,相位会发生变化,为什么?

LMX2820锁定了之后,又失锁,什么因素导致的?

虚焊现象的发生及其预防对策

LMX2492工作一段时间后微波失锁,并且内部寄存器恢复成上电值,为什么?

CDCE62002低温到高温的升温过程中失锁怎么解决?

言必信滤波器 磁环有磁性吗?以及磁环的铁磁现象

锁频环为什么锁定后又发生失锁现象?

锁频环为什么锁定后又发生失锁现象?

评论