本文要点

将 PDN阻抗设计为目标值有助于确保设计的电源稳定性。

PDN 目标阻抗在一定程度上会决定 PDN 上测得的任何电压波动。

确定目标阻抗需要考虑 PDN 上允许的电压波动、输出信号上允许的抖动,或将两者都考虑在内。

阻抗可能是用于普遍概括电子学所有领域信号行为的一项指标。在 PCB 设计中设计具体应用时,我们总是有一些希望实现的目标阻抗,无论是射频走线、差分对,还是阻抗匹配网络。要想确保电源完整性,就要按照 PDN 目标阻抗进行设计,但如何确定 PDN 目标阻抗是一项不小的挑战。

而遗憾的是,没有哪一项行业标准(甚至产品手册中也没有提供一定的规范)可以告诉我们,在 PCB 中实现电源完整性所需的目标阻抗是多少。为此,我们需要针对信号行为、允许的功率波动、甚至 PDN 的拓扑结构来确定最低要求。

1. 对于电源完整性而言,合适的目标阻抗是多少?

去耦电容有助于达到目标阻抗并保持电源完整性

不能想当然地认为任何 PDN 都需要一个特定的目标阻抗水平,因为事实并非如此简单。我们需要选择的阻抗值取决于几个因素,而且根据 PDN 的结构,可能很难确定哪些因素最为重要。影响目标阻抗值的主要因素包括:

电源总线上允许的电压波动

输出信号上允许的时序抖动

数字 IC 中的核心和逻辑电平

流入 PDN 的电流大小和带宽

PDN 是数字的还是模拟的

PDN 的拓扑结构

要确定电源完整性的目标阻抗,有两种最常见的方法,即考虑上述列表中的前两项。虽然该列表中的所有要点都是相互关联的,但前两项通常用于确定 PDN 目标阻抗的设计目标。

最小电压波动的目标阻抗

需要一定的电压波动才能让一定量的电流流入 PDN,而产生电压波动所需的目标阻抗可以由欧姆定律确定。如果知道了允许的电压波动和开关期间的总电流消耗,就可以计算出与这两个值有关的 PDN 阻抗。

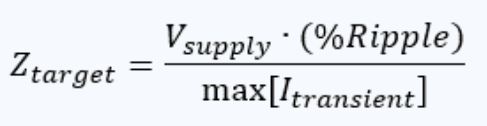

PDN 目标阻抗方程

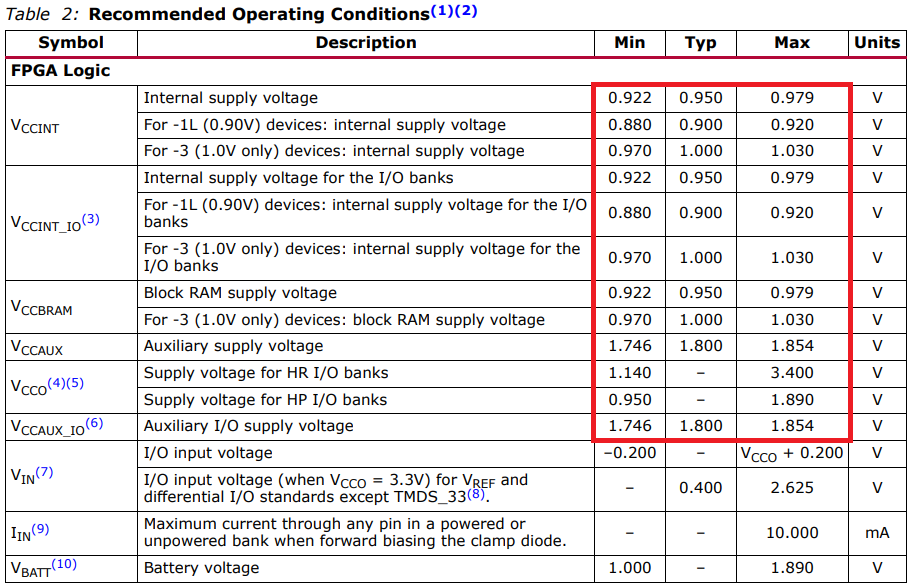

举个例子,只要翻阅一下主处理器的数据手册就可以确定限值。下图所示为 Kintex UltraScale FPGA 的电源电压数据。我们可以根据数据表中列出的电源电压的标称值、最小值和最大值(见下面的红框),对电源轨电压的波动设定一个限制。

某大型 FPGA 的电源电压数据

例如,在第一行中,如果我们考虑到 VCCINT 内部电源电压有 20% 的安全裕度,我们可以将允许的电源轨电压波动设置从 0.927 V 到 0.974 V。接下来,在产品手册中找到开关期间的电流消耗,并使用欧姆定律来确定设计中的 PDN 目标阻抗。只要该电源轨的 PDN 阻抗在整个信号带宽内低于目标值,那么任何电压波动都可以最小化。

最小抖动的目标阻抗

确保抖动最小化是一个重要的目标,有时也可用来确定 PDN 的目标阻抗。当一个数字器件进行开关操作并导致电源总线上的电压波动时,器件中不断变化的逻辑电平会导致信号中的时序和上升速率发生波动。显然,这两者相互依存,并创造了一个有趣的反馈系统,但要使抖动最小化,就必须使这种电源波动最小化。

抖动的典型值可以从 10ps/mV 到 100ps/mV(对于某些逻辑电路而言)不等。高精度时序和测量应用需要将抖动降低至 1 ps/mV。这方面的例子包括点云成像应用,如激光雷达、4D 雷达和其他电子光学应用。

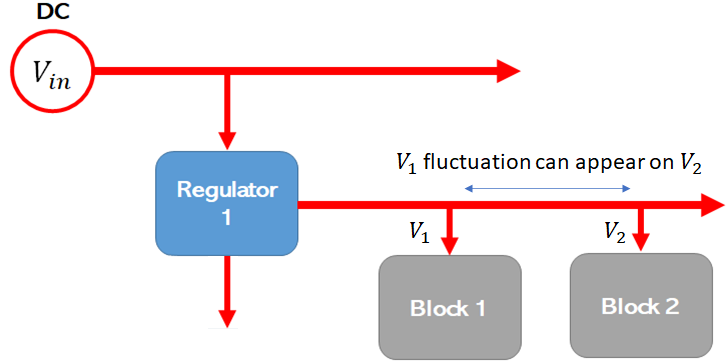

拓扑结构

PDN 的拓扑结构也会影响目标阻抗,但并不是以我们预期的方式。典型 PCB 中的 PDN 可以有一个多总线拓扑结构。在这种拓扑结构中,通常有一个初级稳压器,将输入电压降至高逻辑电平 (5V),并将电源分支至总线。总线上也会放置其他稳压器,用于继续降低电压。详见下面方框图中的示意图。

典型的 PDN 拓扑结构,一条电源总线上有多个电路模块

每个总线段上的不同电路模块和器件可以相互影响,这意味着由一个器件引起的 PDN 上的干扰可以传播到所有其他器件。这可以用 Z 参数矩阵来量化,它也称为阻抗参数矩阵。从该矩阵可以全面了解 PDN 阻抗,以及流入 PDN 某部分的电流如何在其他部分产生纹波。3D 电磁场求解器可用于确定网络参数矩阵,并在开始原型设计之前评估电路板的电源完整性。

2. 努力降低 PDN 阻抗

一般来说,无论 PDN 的拓扑结构如何,我们都应该努力在所需带宽内将 PDN 阻抗降至最低。把 PDN 阻抗降到零是不可能的,但如果能把 PDN 阻抗降到毫欧级别,达到 GHz 级频率,那么设计就会非常顺利。如果使用大量具有不同 ESL 值的去耦电容和相邻平面,将有助于降低 PDN 阻抗,从而使电源总线电压波动和输出信号的抖动保持在一个较低的水平。

在所有设计挑战中,目标阻抗只是电源完整性的一个方面。Cadence Sigrity X 软件可以帮助我们评估设计中的电源完整性,并提供了一整套时域和频域仿真功能,以确定目标阻抗是否需要降低。Sigrity X 提供了一系列可以用于 PDN 阻抗分析的仿真功能,在全面评估系统功能并确保电源完整性上助您一臂之力。

文章来源:Cadence楷登PCB及封装资源中心

审核编辑 黄宇

-

电源

+关注

关注

185文章

18433浏览量

257471 -

阻抗

+关注

关注

17文章

975浏览量

47660 -

PDN

+关注

关注

0文章

84浏览量

23131

发布评论请先 登录

Samtec虎家大咖说 | 浅谈信号完整性以及电源完整性

电源完整性基础知识

使用罗德与施瓦茨RTE1104示波器进行电源完整性测试

电源完整性分析及其应用

电源完整性理论基础

电源完整性分析参考解决方案

如何确定目标阻抗以实现电源完整性?

如何确定目标阻抗以实现电源完整性?

评论